Computer Development at the National Bureau of Standards

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Early Stored Program Computers

Stored Program Computers Thomas J. Bergin Computing History Museum American University 7/9/2012 1 Early Thoughts about Stored Programming • January 1944 Moore School team thinks of better ways to do things; leverages delay line memories from War research • September 1944 John von Neumann visits project – Goldstine’s meeting at Aberdeen Train Station • October 1944 Army extends the ENIAC contract research on EDVAC stored-program concept • Spring 1945 ENIAC working well • June 1945 First Draft of a Report on the EDVAC 7/9/2012 2 First Draft Report (June 1945) • John von Neumann prepares (?) a report on the EDVAC which identifies how the machine could be programmed (unfinished very rough draft) – academic: publish for the good of science – engineers: patents, patents, patents • von Neumann never repudiates the myth that he wrote it; most members of the ENIAC team contribute ideas; Goldstine note about “bashing” summer7/9/2012 letters together 3 • 1.0 Definitions – The considerations which follow deal with the structure of a very high speed automatic digital computing system, and in particular with its logical control…. – The instructions which govern this operation must be given to the device in absolutely exhaustive detail. They include all numerical information which is required to solve the problem…. – Once these instructions are given to the device, it must be be able to carry them out completely and without any need for further intelligent human intervention…. • 2.0 Main Subdivision of the System – First: since the device is a computor, it will have to perform the elementary operations of arithmetics…. – Second: the logical control of the device is the proper sequencing of its operations (by…a control organ. -

Simon E. Gluck Collection of Photographs of EDVAC and MSAC Computers 1990.232

Simon E. Gluck collection of photographs of EDVAC and MSAC computers 1990.232 This finding aid was produced using ArchivesSpace on September 19, 2021. Description is written in: English. Describing Archives: A Content Standard Audiovisual Collections PO Box 3630 Wilmington, Delaware 19807 [email protected] URL: http://www.hagley.org/library Simon E. Gluck collection of photographs of EDVAC and MSAC computers 1990.232 Table of Contents Summary Information .................................................................................................................................... 3 Biographical Note .......................................................................................................................................... 3 Scope and Content ......................................................................................................................................... 4 Administrative Information ............................................................................................................................ 4 Related Materials ........................................................................................................................................... 5 Controlled Access Headings .......................................................................................................................... 5 Additonal Extent Statement ........................................................................................................................... 5 - Page 2 - Simon E. Gluck collection -

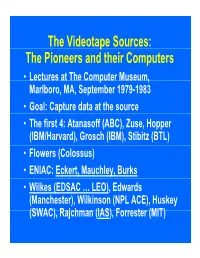

P the Pioneers and Their Computers

The Videotape Sources: The Pioneers and their Computers • Lectures at The Compp,uter Museum, Marlboro, MA, September 1979-1983 • Goal: Capture data at the source • The first 4: Atanasoff (ABC), Zuse, Hopper (IBM/Harvard), Grosch (IBM), Stibitz (BTL) • Flowers (Colossus) • ENIAC: Eckert, Mauchley, Burks • Wilkes (EDSAC … LEO), Edwards (Manchester), Wilkinson (NPL ACE), Huskey (SWAC), Rajchman (IAS), Forrester (MIT) What did it feel like then? • What were th e comput ers? • Why did their inventors build them? • What materials (technology) did they build from? • What were their speed and memory size specs? • How did they work? • How were they used or programmed? • What were they used for? • What did each contribute to future computing? • What were the by-products? and alumni/ae? The “classic” five boxes of a stored ppgrogram dig ital comp uter Memory M Central Input Output Control I O CC Central Arithmetic CA How was programming done before programming languages and O/Ss? • ENIAC was programmed by routing control pulse cables f ormi ng th e “ program count er” • Clippinger and von Neumann made “function codes” for the tables of ENIAC • Kilburn at Manchester ran the first 17 word program • Wilkes, Wheeler, and Gill wrote the first book on programmiidbBbbIiSiing, reprinted by Babbage Institute Series • Parallel versus Serial • Pre-programming languages and operating systems • Big idea: compatibility for program investment – EDSAC was transferred to Leo – The IAS Computers built at Universities Time Line of First Computers Year 1935 1940 1945 1950 1955 ••••• BTL ---------o o o o Zuse ----------------o Atanasoff ------------------o IBM ASCC,SSEC ------------o-----------o >CPC ENIAC ?--------------o EDVAC s------------------o UNIVAC I IAS --?s------------o Colossus -------?---?----o Manchester ?--------o ?>Ferranti EDSAC ?-----------o ?>Leo ACE ?--------------o ?>DEUCE Whirl wi nd SEAC & SWAC ENIAC Project Time Line & Descendants IBM 701, Philco S2000, ERA.. -

SIMD1 Ñ Illiac IV

Illiac IV History Illiac IV n First massively parallel computer ● SIMD (duplicate the PE, not the CU) ● First large system with semiconductor- based primary memory n Three earlier designs (vacuum tubes and transistors) culminating in the Illiac IV design, all at the University of Illinois ● Logical organization similar to the Solomon (prototyped by Westinghouse) ● Sponsored by DARPA, built by various companies, assembled by Burroughs ● Plan was for 256 PEs, in 4 quadrants of 64 PEs, but only one quadrant was built ● Used at NASA Ames Research Center in mid-1970s 1 Fall 2001, Lecture SIMD1 2 Fall 2001, Lecture SIMD1 Illiac IV Architectural Overview Programming Issues n One CU (control unit), n Consider the following FORTRAN code: 64 64-bit PEs (processing elements), DO 10 I = 1, 64 each PE has a PEM (PE memory) 10 A(I) = B(I) + C(I) ● Put A(1), B(1), C(1) on PU 1, etc. n CU operates on scalars, PEs on vector- n Each PE loads RGA from base+1, aligned arrays adds base+2, stores into base, ● All PEs execute the instruction broadcast where “base” is base of data in PEM by the CU, if they are in active mode n Each PE does this simultaneously, giving a speedup of 64 ● Each PE can perform various arithmetic ● and logical instructions For less than 64 array elements, some processors will sit idle ● Each PE has a memory with 2048 64-bit ● words, accessed in less than 188 ns For more than 64 array elements, some processors might have to do more work ● PEs can operate on data in 64-bit, 32-bit, and 8-bit formats n For some algorithms, it may be desirable to turn off PEs n Data routed between PEs various ways ● 64 PEs compute, then one half passes data to other half, then 32 PEs compute, n I/O is handled by a separate Burroughs etc. -

John William Mauchly

John William Mauchly Born August 30, 1907, Cincinnati, Ohio; died January 8, 1980, Abington, Pa.; the New York Times obituary (Smolowe 1980) described Mauchly as a “co-inventor of the first electronic computer” but his accomplishments went far beyond that simple description. Education: physics, Johns Hopkins University, 1929; PhD, physics, Johns Hopkins University, 1932. Professional Experience: research assistant, Johns Hopkins University, 1932-1933; professor of physics, Ursinus College, 1933-1941; Moore School of Electrical Engineering, 1941-1946; member, Electronic Control Company, 1946-1948; president, Eckert-Mauchly Computer Company, 1948-1950; Remington-Rand, 1950-1955; director, Univac Applications Research, Sperry-Rand 1955-1959; Mauchly Associates, 1959-1980; Dynatrend Consulting Company, 1967-1980. Honors and Awards: president, ACM, 1948-1949; Howard N. Potts Medal, Franklin Institute, 1949; John Scott Award, 1961; Modern Pioneer Award, NAM, 1965; AMPS Harry Goode Memorial Award for Excellence, 1968; IEEE Emanual R. Piore Award, 1978; IEEE Computer Society Pioneer Award, 1980; member, Information Processing Hall of Fame, Infornart, Dallas, Texas, 1985. Mauchly was born in Cincinnati, Ohio, on August 30, 1907. He attended Johns Hopkins University initially as an engineering student but later transferred into physics. He received his PhD degree in physics in 1932 and the following year became a professor of physics at Ursinus College in Collegeville, Pennsylvania. At Ursinus he was well known for his excellent and dynamic teaching, and for his research in meteorology. Because his meteorological work required extensive calculations, he began to experiment with alternatives to mechanical tabulating equipment in an effort to reduce the time required to solve meteorological equations. -

The Manchester University "Baby" Computer and Its Derivatives, 1948 – 1951”

Expert Report on Proposed Milestone “The Manchester University "Baby" Computer and its Derivatives, 1948 – 1951” Thomas Haigh. University of Wisconsin—Milwaukee & Siegen University March 10, 2021 Version of citation being responded to: The Manchester University "Baby" Computer and its Derivatives, 1948 - 1951 At this site on 21 June 1948 the “Baby” became the first computer to execute a program stored in addressable read-write electronic memory. “Baby” validated the widely used Williams- Kilburn Tube random-access memories and led to the 1949 Manchester Mark I which pioneered index registers. In February 1951, Ferranti Ltd's commercial Mark I became the first electronic computer marketed as a standard product ever delivered to a customer. 1: Evaluation of Citation The final wording is the result of several rounds of back and forth exchange of proposed drafts with the proposers, mediated by Brian Berg. During this process the citation text became, from my viewpoint at least, far more precise and historically reliable. The current version identifies several distinct contributions made by three related machines: the 1948 “Baby” (known officially as the Small Scale Experimental Machine or SSEM), a minimal prototype computer which ran test programs to prove the viability of the Manchester Mark 1, a full‐scale computer completed in 1949 that was fully designed and approved only after the success of the “Baby” and in turn served as a prototype of the Ferranti Mark 1, a commercial refinement of the Manchester Mark 1 of which I believe 9 copies were sold. The 1951 date refers to the delivery of the first of these, to Manchester University as a replacement for its home‐built Mark 1. -

Oral History Interview with David J. Wheeler

An Interview with DAVID J. WHEELER OH 132 Conducted by William Aspray on 14 May 1987 Princeton, NJ Charles Babbage Institute The Center for the History of Information Processing University of Minnesota, Minneapolis Copyright, Charles Babbage Institute 1 David J. Wheeler Interview 14 May 1987 Abstract Wheeler, who was a research student at the University Mathematical Laboratory at Cambridge from 1948-51, begins with a discussion of the EDSAC project during his tenure. He compares the research orientation and the programming methods at Cambridge with those at the Institute for Advanced Study. He points out that, while the Cambridge group was motivated to process many smaller projects from the larger university community, the Institute was involved with a smaller number of larger projects. Wheeler mentions some of the projects that were run on the EDSAC, the user-oriented programming methods that developed at the laboratory, and the influence of the EDSAC model on the ILLIAC, the ORDVAC, and the IBM 701. He also discusses the weekly meetings held in conjunction with the National Physical Laboratory, the University of Birmingham, and the Telecommunications Research Establishment. These were attended by visitors from other British institutions as well as from the continent and the United States. Wheeler notes visits by Douglas Hartree (of Cavendish Laboratory), Nelson Blackman (of ONR), Peter Naur, Aad van Wijngarden, Arthur van der Poel, Friedrich L. Bauer, and Louis Couffignal. In the final part of the interview Wheeler discusses his visit to Illinois where he worked on the ILLIAC and taught from September 1951 to September 1953. 2 DAVID J. -

A Large Routine

A large routine Freek Wiedijk It is not widely known, but already in June 1949∗ Alan Turing had the main concepts that still are the basis for the best approach to program verification known today (and for which Tony Hoare developed a logic in 1969). In his three page paper Checking a large routine, Turing describes how to verify the correctness of a program that calculates the factorial function by repeated additions. He both shows how to use invariants to establish the correctness of this program, as well as how to use a variant to establish termination. In the paper the program is only presented as a flow chart. A modern C rendering is: int fac (int n) { int s, r, u, v; for (u = r = 1; v = u, r < n; r++) for (s = 1; u += v, s++ < r; ) ; return u; } Turing's paper seems not to have been properly appreciated at the time. At the EDSAC conference where Turing presented the paper, Douglas Hartree criticized that the correctness proof sketched by Turing should not be called inductive. From a modern point of view this is clearly absurd. Marc Schoolderman first told me about this paper (and in his master's thesis used the modern Why3 tool of Jean-Christophe Filli^atreto make Turing's paper fully precise; he also wrote the above C version of Turing's program). He then challenged me to speculate what specific computer Turing had in mind in the paper, and what the actual program for that computer might have been. My answer is that the `EPICAC'y of this paper probably was the Manchester Mark 1. -

John W. Mauchly Papers Ms

John W. Mauchly papers Ms. Coll. 925 Finding aid prepared by Holly Mengel. Last updated on April 27, 2020. University of Pennsylvania, Kislak Center for Special Collections, Rare Books and Manuscripts 2015 September 9 John W. Mauchly papers Table of Contents Summary Information....................................................................................................................................3 Biography/History..........................................................................................................................................4 Scope and Contents....................................................................................................................................... 6 Administrative Information........................................................................................................................... 7 Related Materials........................................................................................................................................... 8 Controlled Access Headings..........................................................................................................................8 Collection Inventory.................................................................................................................................... 10 Series I. Youth, education, and early career......................................................................................... 10 Series II. Moore School of Electrical Engineering, University of Pennsylvania................................. -

Pioneercomputertimeline2.Pdf

Memory Size versus Computation Speed for various calculators and computers , IBM,ZQ90 . 11J A~len · W •• EDVAC lAS• ,---.. SEAC • Whirlwind ~ , • ENIAC SWAC /# / Harvard.' ~\ EDSAC Pilot• •• • ; Mc;rk I " • ACE I • •, ABC Manchester MKI • • ! • Z3 (fl. pt.) 1.000 , , .ENIAC •, Ier.n I i • • \ I •, BTL I (complexV • 100 ~ . # '-------" Comptometer • Ir.ne l ' with constants 10 0.1 1.0 10 100 lK 10K lOOK 1M GENERATIONS: II] = electronic-vacuum tube [!!!] = manual [1] = transistor Ime I = mechanical [1] = integrated circuit Iem I = electromechanical [I] = large scale integrated circuit CONTENTS THE COMPUTER MUSEUM BOARD OF DIRECTORS The Computer Museum is a non-profit. Kenneth H. Olsen. Chairman public. charitable foundation dedicated to Digital Equipment Corporation preserving and exhibiting an industry-wide. broad-based collection of the history of in Charles W Bachman formation processing. Computer history is Cullinane Database Systems A Compcmion to the Pioneer interpreted through exhibits. publications. Computer Timeline videotapes. lectures. educational programs. C. Gordon Bell and other programs. The Museum archives Digital Equipment Corporation I Introduction both artifacts and documentation and Gwen Bell makes the materials available for The Computer Museum 2 Bell Telephone Laboratories scholarly use. Harvey D. Cragon Modell Complex Calculator The Computer Museum is open to the public Texas Instruments Sunday through Friday from 1:00 to 6:00 pm. 3 Zuse Zl, Z3 There is no charge for admission. The Robert Everett 4 ABC. Atanasoff Berry Computer Museum's lecture hall and rece ption The Mitre Corporation facilities are available for rent on a mM ASCC (Harvard Mark I) prearranged basis. For information call C. -

Markov Chain Monte Carlo Methods

Introduction to Machine Learning CMU-10701 Markov Chain Monte Carlo Methods Barnabás Póczos Contents Markov Chain Monte Carlo Methods Sampling • Rejection • Importance • Hastings-Metropolis • Gibbs Markov Chains • Properties Particle Filtering • Condensation 2 Monte Carlo Methods 3 Markov Chain Monte Carlo History A recent survey places the Metropolis algorithm among the 10 algorithms that have had the greatest influence on the development and practice of science and engineering in the 20th century (Beichl&Sullivan, 2000). The Metropolis algorithm is an instance of a large class of sampling algorithms, known as Markov chain Monte Carlo (MCMC) MCMC plays significant role in statistics, econometrics, physics and computing science. There are several high-dimensional problems, such as computing the volume of a convex body in d dimensions and other high-dim integrals, for which MCMC simulation is the only known general approach for providing a solution within a reasonable time. 4 Markov Chain Monte Carlo History While convalescing from an illness in 1946, Stanislaw Ulam was playing solitaire. It, then, occurred to him to try to compute the chances that a particular solitaire laid out with 52 cards would come out successfully (Eckhard, 1987). Exhaustive combinatorial calculations are very difficult. New, more practical approach: laying out several solitaires at random and then observing and counting the number of successful plays. This idea of selecting a statistical sample to approximate a hard combinatorial problem by a much simpler problem is at the heart of modern Monte Carlo simulation. 5 FERMIAC FERMIAC: The beginning of Monte Carlo Methods Developed in the Early 1930’s The Monte Carlo trolley, or FERMIAC, was an analog computer invented by physicist Enrico Fermi to aid in his studies of neutron transport. -

Parallel Architecture Hardware and General Purpose Operating System

Parallel Architecture Hardware and General Purpose Operating System Co-design Oskar Schirmer G¨ottingen, 2018-07-10 Abstract Because most optimisations to achieve higher computational performance eventually are limited, parallelism that scales is required. Parallelised hard- ware alone is not sufficient, but software that matches the architecture is required to gain best performance. For decades now, hardware design has been guided by the basic design of existing software, to avoid the higher cost to redesign the latter. In doing so, however, quite a variety of supe- rior concepts is excluded a priori. Consequently, co-design of both hardware and software is crucial where highest performance is the goal. For special purpose application, this co-design is common practice. For general purpose application, however, a precondition for usability of a computer system is an arXiv:1807.03546v1 [cs.DC] 10 Jul 2018 operating system which is both comprehensive and dynamic. As no such op- erating system has ever been designed, a sketch for a comprehensive dynamic operating system is presented, based on a straightforward hardware architec- ture to demonstrate how design decisions regarding software and hardware do coexist and harmonise. 1 Contents 1 Origin 4 1.1 Performance............................ 4 1.2 Limits ............................... 5 1.3 TransparentStructuralOptimisation . 8 1.4 VectorProcessing......................... 9 1.5 Asymmetric Multiprocessing . 10 1.6 SymmetricMulticore ....................... 11 1.7 MultinodeComputer ....................... 12 2 Review 14 2.1 SharedMemory.......................... 14 2.2 Cache ............................... 15 2.3 Synchronisation .......................... 15 2.4 Time-Shared Multitasking . 15 2.5 Interrupts ............................. 16 2.6 Exceptions............................. 16 2.7 PrivilegedMode.......................... 17 2.8 PeripheralI/O .........................