The Computer As Von Neumann Planned It MD Godfrey* DF Hendry

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Early Stored Program Computers

Stored Program Computers Thomas J. Bergin Computing History Museum American University 7/9/2012 1 Early Thoughts about Stored Programming • January 1944 Moore School team thinks of better ways to do things; leverages delay line memories from War research • September 1944 John von Neumann visits project – Goldstine’s meeting at Aberdeen Train Station • October 1944 Army extends the ENIAC contract research on EDVAC stored-program concept • Spring 1945 ENIAC working well • June 1945 First Draft of a Report on the EDVAC 7/9/2012 2 First Draft Report (June 1945) • John von Neumann prepares (?) a report on the EDVAC which identifies how the machine could be programmed (unfinished very rough draft) – academic: publish for the good of science – engineers: patents, patents, patents • von Neumann never repudiates the myth that he wrote it; most members of the ENIAC team contribute ideas; Goldstine note about “bashing” summer7/9/2012 letters together 3 • 1.0 Definitions – The considerations which follow deal with the structure of a very high speed automatic digital computing system, and in particular with its logical control…. – The instructions which govern this operation must be given to the device in absolutely exhaustive detail. They include all numerical information which is required to solve the problem…. – Once these instructions are given to the device, it must be be able to carry them out completely and without any need for further intelligent human intervention…. • 2.0 Main Subdivision of the System – First: since the device is a computor, it will have to perform the elementary operations of arithmetics…. – Second: the logical control of the device is the proper sequencing of its operations (by…a control organ. -

History of Computer Science from Wikipedia, the Free Encyclopedia

History of computer science From Wikipedia, the free encyclopedia The history of computer science began long before the modern discipline of computer science that emerged in the 20th century, and hinted at in the centuries prior. The progression, from mechanical inventions and mathematical theories towards the modern concepts and machines, formed a major academic field and the basis of a massive worldwide industry.[1] Contents 1 Early history 1.1 Binary logic 1.2 Birth of computer 2 Emergence of a discipline 2.1 Charles Babbage and Ada Lovelace 2.2 Alan Turing and the Turing Machine 2.3 Shannon and information theory 2.4 Wiener and cybernetics 2.5 John von Neumann and the von Neumann architecture 3 See also 4 Notes 5 Sources 6 Further reading 7 External links Early history The earliest known as tool for use in computation was the abacus, developed in period 2700–2300 BCE in Sumer . The Sumerians' abacus consisted of a table of successive columns which delimited the successive orders of magnitude of their sexagesimal number system.[2] Its original style of usage was by lines drawn in sand with pebbles . Abaci of a more modern design are still used as calculation tools today.[3] The Antikythera mechanism is believed to be the earliest known mechanical analog computer.[4] It was designed to calculate astronomical positions. It was discovered in 1901 in the Antikythera wreck off the Greek island of Antikythera, between Kythera and Crete, and has been dated to c. 100 BCE. Technological artifacts of similar complexity did not reappear until the 14th century, when mechanical astronomical clocks appeared in Europe.[5] Mechanical analog computing devices appeared a thousand years later in the medieval Islamic world. -

Computer Development at the National Bureau of Standards

Computer Development at the National Bureau of Standards The first fully operational stored-program electronic individual computations could be performed at elec- computer in the United States was built at the National tronic speed, but the instructions (the program) that Bureau of Standards. The Standards Electronic drove these computations could not be modified and Automatic Computer (SEAC) [1] (Fig. 1.) began useful sequenced at the same electronic speed as the computa- computation in May 1950. The stored program was held tions. Other early computers in academia, government, in the machine’s internal memory where the machine and industry, such as Edvac, Ordvac, Illiac I, the Von itself could modify it for successive stages of a compu- Neumann IAS computer, and the IBM 701, would not tation. This made a dramatic increase in the power of begin productive operation until 1952. programming. In 1947, the U.S. Bureau of the Census, in coopera- Although originally intended as an “interim” com- tion with the Departments of the Army and Air Force, puter, SEAC had a productive life of 14 years, with a decided to contract with Eckert and Mauchly, who had profound effect on all U.S. Government computing, the developed the ENIAC, to create a computer that extension of the use of computers into previously would have an internally stored program which unknown applications, and the further development of could be run at electronic speeds. Because of a demon- computing machines in industry and academia. strated competence in designing electronic components, In earlier developments, the possibility of doing the National Bureau of Standards was asked to be electronic computation had been demonstrated by technical monitor of the contract that was issued, Atanasoff at Iowa State University in 1937. -

Simon E. Gluck Collection of Photographs of EDVAC and MSAC Computers 1990.232

Simon E. Gluck collection of photographs of EDVAC and MSAC computers 1990.232 This finding aid was produced using ArchivesSpace on September 19, 2021. Description is written in: English. Describing Archives: A Content Standard Audiovisual Collections PO Box 3630 Wilmington, Delaware 19807 [email protected] URL: http://www.hagley.org/library Simon E. Gluck collection of photographs of EDVAC and MSAC computers 1990.232 Table of Contents Summary Information .................................................................................................................................... 3 Biographical Note .......................................................................................................................................... 3 Scope and Content ......................................................................................................................................... 4 Administrative Information ............................................................................................................................ 4 Related Materials ........................................................................................................................................... 5 Controlled Access Headings .......................................................................................................................... 5 Additonal Extent Statement ........................................................................................................................... 5 - Page 2 - Simon E. Gluck collection -

A Purdue University Course in the History of Computing

Purdue University Purdue e-Pubs Department of Computer Science Technical Reports Department of Computer Science 1991 A Purdue University Course in the History of Computing Saul Rosen Report Number: 91-023 Rosen, Saul, "A Purdue University Course in the History of Computing" (1991). Department of Computer Science Technical Reports. Paper 872. https://docs.lib.purdue.edu/cstech/872 This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact [email protected] for additional information. A PURDUE UNIVERSITY COURSE IN mE HISTORY OF COMPUTING Saul Rosen CSD-TR-91-023 Mrrch 1991 A Purdue University Course in the History of Computing Saul Rosen CSD-TR-91-023 March 1991 Abstract University COUISes in the history of computing are still quite rarc. This paper is a discussion of a one-semester course that I have taught during the past few years in the Department of Computer Sciences at Purdue University. The amount of material that could be included in such a course is overwhelming, and the literature in the subject has increased at a great rate in the past decade. A syllabus and list of major references are presented here as they are presented to the students. The course develops a few major themes, several of which arc discussed briefly in the paper. The coume has been an interesting and stimulating experience for me. and for some of the students who took the course. I do not foresee a rapid expansion in the number of uniVcCiities that will offer courses in the history of computing. -

Alan Turingturing –– Computercomputer Designerdesigner

AlanAlan TuringTuring –– ComputerComputer DesignerDesigner Brian E. Carpenter with input from Robert W. Doran The University of Auckland May 2012 Turing, the theoretician ● Turing is widely regarded as a pure mathematician. After all, he was a B-star Wrangler (in the same year as Maurice Wilkes) ● “It is possible to invent a single machine which can be used to compute any computable sequence. If this machine U is supplied with the tape on the beginning of which is written the string of quintuples separated by semicolons of some computing machine M, then U will compute the same sequence as M.” (1937) ● So how was he able to write Proposals for development in the Mathematics Division of an Automatic Computing Engine (ACE) by the end of 1945? 2 Let’s read that carefully ● “It is possible to inventinvent a single machinemachine which can be used to compute any computable sequence. If this machinemachine U is supplied with the tapetape on the beginning of which is writtenwritten the string of quintuples separated by semicolons of some computing machinemachine M, then U will compute the same sequence as M.” ● The founding statement of computability theory was written in entirely physical terms. 3 What would it take? ● A tape on which you can write, read and erase symbols. ● Poulsen demonstrated magnetic wire recording in 1898. ● A way of storing symbols and performing simple logic. ● Eccles & Jordan patented the multivibrator trigger circuit (flip- flop) in 1919. ● Rossi invented the coincidence circuit (AND gate) in 1930. ● Building U in 1937 would have been only slightly more bizarre than building a differential analyser with Meccano. -

Alan Turing's Automatic Computing Engine

5 Turing and the computer B. Jack Copeland and Diane Proudfoot The Turing machine In his first major publication, ‘On computable numbers, with an application to the Entscheidungsproblem’ (1936), Turing introduced his abstract Turing machines.1 (Turing referred to these simply as ‘computing machines’— the American logician Alonzo Church dubbed them ‘Turing machines’.2) ‘On Computable Numbers’ pioneered the idea essential to the modern computer—the concept of controlling a computing machine’s operations by means of a program of coded instructions stored in the machine’s memory. This work had a profound influence on the development in the 1940s of the electronic stored-program digital computer—an influence often neglected or denied by historians of the computer. A Turing machine is an abstract conceptual model. It consists of a scanner and a limitless memory-tape. The tape is divided into squares, each of which may be blank or may bear a single symbol (‘0’or‘1’, for example, or some other symbol taken from a finite alphabet). The scanner moves back and forth through the memory, examining one square at a time (the ‘scanned square’). It reads the symbols on the tape and writes further symbols. The tape is both the memory and the vehicle for input and output. The tape may also contain a program of instructions. (Although the tape itself is limitless—Turing’s aim was to show that there are tasks that Turing machines cannot perform, even given unlimited working memory and unlimited time—any input inscribed on the tape must consist of a finite number of symbols.) A Turing machine has a small repertoire of basic operations: move left one square, move right one square, print, and change state. -

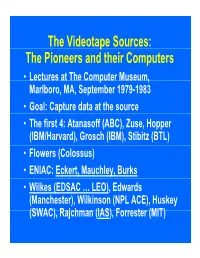

P the Pioneers and Their Computers

The Videotape Sources: The Pioneers and their Computers • Lectures at The Compp,uter Museum, Marlboro, MA, September 1979-1983 • Goal: Capture data at the source • The first 4: Atanasoff (ABC), Zuse, Hopper (IBM/Harvard), Grosch (IBM), Stibitz (BTL) • Flowers (Colossus) • ENIAC: Eckert, Mauchley, Burks • Wilkes (EDSAC … LEO), Edwards (Manchester), Wilkinson (NPL ACE), Huskey (SWAC), Rajchman (IAS), Forrester (MIT) What did it feel like then? • What were th e comput ers? • Why did their inventors build them? • What materials (technology) did they build from? • What were their speed and memory size specs? • How did they work? • How were they used or programmed? • What were they used for? • What did each contribute to future computing? • What were the by-products? and alumni/ae? The “classic” five boxes of a stored ppgrogram dig ital comp uter Memory M Central Input Output Control I O CC Central Arithmetic CA How was programming done before programming languages and O/Ss? • ENIAC was programmed by routing control pulse cables f ormi ng th e “ program count er” • Clippinger and von Neumann made “function codes” for the tables of ENIAC • Kilburn at Manchester ran the first 17 word program • Wilkes, Wheeler, and Gill wrote the first book on programmiidbBbbIiSiing, reprinted by Babbage Institute Series • Parallel versus Serial • Pre-programming languages and operating systems • Big idea: compatibility for program investment – EDSAC was transferred to Leo – The IAS Computers built at Universities Time Line of First Computers Year 1935 1940 1945 1950 1955 ••••• BTL ---------o o o o Zuse ----------------o Atanasoff ------------------o IBM ASCC,SSEC ------------o-----------o >CPC ENIAC ?--------------o EDVAC s------------------o UNIVAC I IAS --?s------------o Colossus -------?---?----o Manchester ?--------o ?>Ferranti EDSAC ?-----------o ?>Leo ACE ?--------------o ?>DEUCE Whirl wi nd SEAC & SWAC ENIAC Project Time Line & Descendants IBM 701, Philco S2000, ERA.. -

The Essential Turing: Seminal Writings in Computing, Logic, Philosophy, Artificial Intelligence, and Artificial Life: Plus the Secrets of Enigma

The Essential Turing: Seminal Writings in Computing, Logic, Philosophy, Artificial Intelligence, and Artificial Life: Plus The Secrets of Enigma B. Jack Copeland, Editor OXFORD UNIVERSITY PRESS The Essential Turing Alan M. Turing The Essential Turing Seminal Writings in Computing, Logic, Philosophy, Artificial Intelligence, and Artificial Life plus The Secrets of Enigma Edited by B. Jack Copeland CLARENDON PRESS OXFORD Great Clarendon Street, Oxford OX2 6DP Oxford University Press is a department of the University of Oxford. It furthers the University’s objective of excellence in research, scholarship, and education by publishing worldwide in Oxford New York Auckland Cape Town Dar es Salaam Hong Kong Karachi Kuala Lumpur Madrid Melbourne Mexico City Nairobi New Delhi Taipei Toronto Shanghai With offices in Argentina Austria Brazil Chile Czech Republic France Greece Guatemala Hungary Italy Japan South Korea Poland Portugal Singapore Switzerland Thailand Turkey Ukraine Vietnam Published in the United States by Oxford University Press Inc., New York © In this volume the Estate of Alan Turing 2004 Supplementary Material © the several contributors 2004 The moral rights of the author have been asserted Database right Oxford University Press (maker) First published 2004 All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, without the prior permission in writing of Oxford University Press, or as expressly permitted by law, or under terms agreed with the appropriate reprographics rights organization. Enquiries concerning reproduction outside the scope of the above should be sent to the Rights Department, Oxford University Press, at the address above. -

John William Mauchly

John William Mauchly Born August 30, 1907, Cincinnati, Ohio; died January 8, 1980, Abington, Pa.; the New York Times obituary (Smolowe 1980) described Mauchly as a “co-inventor of the first electronic computer” but his accomplishments went far beyond that simple description. Education: physics, Johns Hopkins University, 1929; PhD, physics, Johns Hopkins University, 1932. Professional Experience: research assistant, Johns Hopkins University, 1932-1933; professor of physics, Ursinus College, 1933-1941; Moore School of Electrical Engineering, 1941-1946; member, Electronic Control Company, 1946-1948; president, Eckert-Mauchly Computer Company, 1948-1950; Remington-Rand, 1950-1955; director, Univac Applications Research, Sperry-Rand 1955-1959; Mauchly Associates, 1959-1980; Dynatrend Consulting Company, 1967-1980. Honors and Awards: president, ACM, 1948-1949; Howard N. Potts Medal, Franklin Institute, 1949; John Scott Award, 1961; Modern Pioneer Award, NAM, 1965; AMPS Harry Goode Memorial Award for Excellence, 1968; IEEE Emanual R. Piore Award, 1978; IEEE Computer Society Pioneer Award, 1980; member, Information Processing Hall of Fame, Infornart, Dallas, Texas, 1985. Mauchly was born in Cincinnati, Ohio, on August 30, 1907. He attended Johns Hopkins University initially as an engineering student but later transferred into physics. He received his PhD degree in physics in 1932 and the following year became a professor of physics at Ursinus College in Collegeville, Pennsylvania. At Ursinus he was well known for his excellent and dynamic teaching, and for his research in meteorology. Because his meteorological work required extensive calculations, he began to experiment with alternatives to mechanical tabulating equipment in an effort to reduce the time required to solve meteorological equations. -

The Manchester University "Baby" Computer and Its Derivatives, 1948 – 1951”

Expert Report on Proposed Milestone “The Manchester University "Baby" Computer and its Derivatives, 1948 – 1951” Thomas Haigh. University of Wisconsin—Milwaukee & Siegen University March 10, 2021 Version of citation being responded to: The Manchester University "Baby" Computer and its Derivatives, 1948 - 1951 At this site on 21 June 1948 the “Baby” became the first computer to execute a program stored in addressable read-write electronic memory. “Baby” validated the widely used Williams- Kilburn Tube random-access memories and led to the 1949 Manchester Mark I which pioneered index registers. In February 1951, Ferranti Ltd's commercial Mark I became the first electronic computer marketed as a standard product ever delivered to a customer. 1: Evaluation of Citation The final wording is the result of several rounds of back and forth exchange of proposed drafts with the proposers, mediated by Brian Berg. During this process the citation text became, from my viewpoint at least, far more precise and historically reliable. The current version identifies several distinct contributions made by three related machines: the 1948 “Baby” (known officially as the Small Scale Experimental Machine or SSEM), a minimal prototype computer which ran test programs to prove the viability of the Manchester Mark 1, a full‐scale computer completed in 1949 that was fully designed and approved only after the success of the “Baby” and in turn served as a prototype of the Ferranti Mark 1, a commercial refinement of the Manchester Mark 1 of which I believe 9 copies were sold. The 1951 date refers to the delivery of the first of these, to Manchester University as a replacement for its home‐built Mark 1. -

John W. Mauchly Papers Ms

John W. Mauchly papers Ms. Coll. 925 Finding aid prepared by Holly Mengel. Last updated on April 27, 2020. University of Pennsylvania, Kislak Center for Special Collections, Rare Books and Manuscripts 2015 September 9 John W. Mauchly papers Table of Contents Summary Information....................................................................................................................................3 Biography/History..........................................................................................................................................4 Scope and Contents....................................................................................................................................... 6 Administrative Information........................................................................................................................... 7 Related Materials........................................................................................................................................... 8 Controlled Access Headings..........................................................................................................................8 Collection Inventory.................................................................................................................................... 10 Series I. Youth, education, and early career......................................................................................... 10 Series II. Moore School of Electrical Engineering, University of Pennsylvania.................................