Bipolar Transistor

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Imperial College London Department of Physics Graphene Field Effect

Imperial College London Department of Physics Graphene Field Effect Transistors arXiv:2010.10382v2 [cond-mat.mes-hall] 20 Jul 2021 By Mohamed Warda and Khodr Badih 20 July 2021 Abstract The past decade has seen rapid growth in the research area of graphene and its application to novel electronics. With Moore's law beginning to plateau, the need for post-silicon technology in industry is becoming more apparent. Moreover, exist- ing technologies are insufficient for implementing terahertz detectors and receivers, which are required for a number of applications including medical imaging and secu- rity scanning. Graphene is considered to be a key potential candidate for replacing silicon in existing CMOS technology as well as realizing field effect transistors for terahertz detection, due to its remarkable electronic properties, with observed elec- tronic mobilities reaching up to 2 × 105 cm2 V−1 s−1 in suspended graphene sam- ples. This report reviews the physics and electronic properties of graphene in the context of graphene transistor implementations. Common techniques used to syn- thesize graphene, such as mechanical exfoliation, chemical vapor deposition, and epitaxial growth are reviewed and compared. One of the challenges associated with realizing graphene transistors is that graphene is semimetallic, with a zero bandgap, which is troublesome in the context of digital electronics applications. Thus, the report also reviews different ways of opening a bandgap in graphene by using bi- layer graphene and graphene nanoribbons. The basic operation of a conventional field effect transistor is explained and key figures of merit used in the literature are extracted. Finally, a review of some examples of state-of-the-art graphene field effect transistors is presented, with particular focus on monolayer graphene, bilayer graphene, and graphene nanoribbons. -

PN Junction Is the Most Fundamental Semiconductor Device

Fundamentals of Microelectronics CH1 Why Microelectronics? CH2 Basic Physics of Semiconductors CH3 Diode Circuits CH4 Physics of Bipolar Transistors CH5 Bipolar Amplifiers CH6 Physics of MOS Transistors CH7 CMOS Amplifiers CH8 Operational Amplifier As A Black Box 1 Chapter 2 Basic Physics of Semiconductors 2.1 Semiconductor materials and their properties 2.2 PN-junction diodes 2.3 Reverse Breakdown 2 Semiconductor Physics Semiconductor devices serve as heart of microelectronics. PN junction is the most fundamental semiconductor device. CH2 Basic Physics of Semiconductors 3 Charge Carriers in Semiconductor To understand PN junction’s IV characteristics, it is important to understand charge carriers’ behavior in solids, how to modify carrier densities, and different mechanisms of charge flow. CH2 Basic Physics of Semiconductors 4 Periodic Table This abridged table contains elements with three to five valence electrons, with Si being the most important. CH2 Basic Physics of Semiconductors 5 Silicon Si has four valence electrons. Therefore, it can form covalent bonds with four of its neighbors. When temperature goes up, electrons in the covalent bond can become free. CH2 Basic Physics of Semiconductors 6 Electron-Hole Pair Interaction With free electrons breaking off covalent bonds, holes are generated. Holes can be filled by absorbing other free electrons, so effectively there is a flow of charge carriers. CH2 Basic Physics of Semiconductors 7 Free Electron Density at a Given Temperature E n 5.21015T 3/ 2 exp g electrons/ cm3 i 2kT 0 10 3 ni (T 300 K) 1.0810 electrons/ cm 0 15 3 ni (T 600 K) 1.5410 electrons/ cm Eg, or bandgap energy determines how much effort is needed to break off an electron from its covalent bond. -

Chapter 7: AC Transistor Amplifiers

Chapter 7: Transistors, part 2 Chapter 7: AC Transistor Amplifiers The transistor amplifiers that we studied in the last chapter have some serious problems for use in AC signals. Their most serious shortcoming is that there is a “dead region” where small signals do not turn on the transistor. So, if your signal is smaller than 0.6 V, or if it is negative, the transistor does not conduct and the amplifier does not work. Design goals for an AC amplifier Before moving on to making a better AC amplifier, let’s define some useful terms. We define the output range to be the range of possible output voltages. We refer to the maximum and minimum output voltages as the rail voltages and the output swing is the difference between the rail voltages. The input range is the range of input voltages that produce outputs which are not at either rail voltage. Our goal in designing an AC amplifier is to get an input range and output range which is symmetric around zero and ensure that there is not a dead region. To do this we need make sure that the transistor is in conduction for all of our input range. How does this work? We do it by adding an offset voltage to the input to make sure the voltage presented to the transistor’s base with no input signal, the resting or quiescent voltage , is well above ground. In lab 6, the function generator provided the offset, in this chapter we will show how to design an amplifier which provides its own offset. -

Junction Field Effect Transistor (JFET)

Junction Field Effect Transistor (JFET) The single channel junction field-effect transistor (JFET) is probably the simplest transistor available. As shown in the schematics below (Figure 6.13 in your text) for the n-channel JFET (left) and the p-channel JFET (right), these devices are simply an area of doped silicon with two diffusions of the opposite doping. Please be aware that the schematics presented are for illustrative purposes only and are simplified versions of the actual device. Note that the material that serves as the foundation of the device defines the channel type. Like the BJT, the JFET is a three terminal device. Although there are physically two gate diffusions, they are tied together and act as a single gate terminal. The other two contacts, the drain and source, are placed at either end of the channel region. The JFET is a symmetric device (the source and drain may be interchanged), however it is useful in circuit design to designate the terminals as shown in the circuit symbols above. The operation of the JFET is based on controlling the bias on the pn junction between gate and channel (note that a single pn junction is discussed since the two gate contacts are tied together in parallel – what happens at one gate-channel pn junction is happening on the other). If a voltage is applied between the drain and source, current will flow (the conventional direction for current flow is from the terminal designated to be the gate to that which is designated as the source). The device is therefore in a normally on state. -

The P-N Junction (The Diode)

Lecture 18 The P-N Junction (The Diode). Today: 1. Joining p- and n-doped semiconductors. 2. Depletion and built-in voltage. 3. Current-voltage characteristics of the p-n junction. Questions you should be able to answer by the end of today’s lecture: 1. What happens when we join p-type and n-type semiconductors? 2. What is the width of the depletion region? How does it relate to the dopant concentration? 3. What is built-in voltage? How to calculate it based on dopant concentrations? How to calculate it based on Fermi levels of semiconductors forming the junction? 4. What happens when we apply voltage to the p-n junction? What is forward and reverse bias? 5. What is the current-voltage characteristic for the p-n junction diode? Why is it different from a resistor? 1 From previous lecture we remember: What happens when you join p-doped and n-doped pieces of semiconductor together? When materials are put in contact the carriers flow under driving force of diffusion until chemical potential on both sides equilibrates, which would mean that the position of the Fermi level must be the same in both p and n sides. This results in band bending: - + - + + - - Holes diffuse + Electrons diffuse The electrons will diffuse into p-type material where they will recombine with holes (fill in holes). And holes will diffuse into the n-type materials where they will recombine with electrons. 2 This means that eventually in vicinity of the junction all free carriers will be depleted leaving stripped ions behind, which would produce an electric field across the junction: The electric field results from the deviation from charge neutrality in the vicinity of the junction. -

A New Paradigm in High-Speed and High-Efficiency Silicon Photodiodes

382 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 65, NO. 2, FEBRUARY 2018 A New Paradigm in High-Speed and High-Efficiency Silicon Photodiodes for Communication—Part II: Device and VLSI Integration Challenges for Low-Dimensional Structures Hilal Cansizoglu , Member, IEEE, Aly F. Elrefaie, Fellow, IEEE, Cesar Bartolo-Perez, Toshishige Yamada, Senior Member, IEEE, Yang Gao, Ahmed S. Mayet, Mehmet F. Cansizoglu, Ekaterina Ponizovskaya Devine, Shih-Yuan Wang, Life Fellow, IEEE,and M. Saif Islam, Senior Member, IEEE (Invited Review Paper) Abstract— The ability to monolithically integrate high- Index Terms— CMOS integration, extended-reach links, speed photodetectors (PDs) with silicon (Si) can contribute high speed, high-efficiency photodetectors (PDs), high- to drastic reduction in cost. Such PDs are envisioned to performance computing, light detection and ranging, micro- be integral parts of high-speed optical interconnects in /nanostructures, single-photon detection, surface states, the future intrachip, chip-to-chip, board-to-board, rack-to- very-large-scale integration (VLSI) and ultralarge-scale inte- rack, and intra-/interdata center links. Si-based PDs are of gration (ULSI). special interest since they present the potential for mono- lithic integration with CMOS and BiCMOS very-large-scale integration and ultralarge-scale integration electronics. I. INTRODUCTION In the second part of this review, we present the efforts HE rise of distributed computing, cloud storage, social pursued by the researchers in engineering and integrating Si, SiGe alloys, and Ge PDs to CMOS and BiCMOS electron- Tmedia, and affordable hand-held devices currently allow ics and compare the performance of recently demonstrated extreme ease of transferring a plethora of data including CMOS-compatible ultrafast surface-illuminated Si PD with videos, pictures, and texts, all over the world. -

Notes for Lab 1 (Bipolar (Junction) Transistor Lab)

ECE 327: Electronic Devices and Circuits Laboratory I Notes for Lab 1 (Bipolar (Junction) Transistor Lab) 1. Introduce bipolar junction transistors • “Transistor man” (from The Art of Electronics (2nd edition) by Horowitz and Hill) – Transistors are not “switches” – Base–emitter diode current sets collector–emitter resistance – Transistors are “dynamic resistors” (i.e., “transfer resistor”) – Act like closed switch in “saturation” mode – Act like open switch in “cutoff” mode – Act like current amplifier in “active” mode • Active-mode BJT model – Collector resistance is dynamically set so that collector current is β times base current – β is assumed to be very high (β ≈ 100–200 in this laboratory) – Under most conditions, base current is negligible, so collector and emitter current are equal – β ≈ hfe ≈ hFE – Good designs only depend on β being large – The active-mode model: ∗ Assumptions: · Must have vEC > 0.2 V (otherwise, in saturation) · Must have very low input impedance compared to βRE ∗ Consequences: · iB ≈ 0 · vE = vB ± 0.7 V · iC ≈ iE – Typically, use base and emitter voltages to find emitter current. Finish analysis by setting collector current equal to emitter current. • Symbols – Arrow represents base–emitter diode (i.e., emitter always has arrow) – npn transistor: Base–emitter diode is “not pointing in” – pnp transistor: Emitter–base diode “points in proudly” – See part pin-outs for easy wiring key • “Common” configurations: hold one terminal constant, vary a second, and use the third as output – common-collector ties collector -

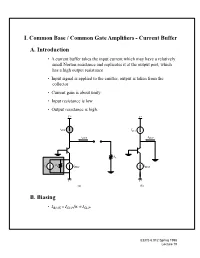

I. Common Base / Common Gate Amplifiers

I. Common Base / Common Gate Amplifiers - Current Buffer A. Introduction • A current buffer takes the input current which may have a relatively small Norton resistance and replicates it at the output port, which has a high output resistance • Input signal is applied to the emitter, output is taken from the collector • Current gain is about unity • Input resistance is low • Output resistance is high. V+ V+ i SUP ISUP iOUT IOUT RL R is S IBIAS IBIAS V− V− (a) (b) B. Biasing = /α ≈ • IBIAS ISUP ISUP EECS 6.012 Spring 1998 Lecture 19 II. Small Signal Two Port Parameters A. Common Base Current Gain Ai • Small-signal circuit; apply test current and measure the short circuit output current ib iout + = β v r gmv oib r − o ve roc it • Analysis -- see Chapter 8, pp. 507-509. • Result: –β ---------------o ≅ Ai = β – 1 1 + o • Intuition: iout = ic = (- ie- ib ) = -it - ib and ib is small EECS 6.012 Spring 1998 Lecture 19 B. Common Base Input Resistance Ri • Apply test current, with load resistor RL present at the output + v r gmv r − o roc RL + vt i − t • See pages 509-510 and note that the transconductance generator dominates which yields 1 Ri = ------ gm µ • A typical transconductance is around 4 mS, with IC = 100 A • Typical input resistance is 250 Ω -- very small, as desired for a current amplifier • Ri can be designed arbitrarily small, at the price of current (power dissipation) EECS 6.012 Spring 1998 Lecture 19 C. Common-Base Output Resistance Ro • Apply test current with source resistance of input current source in place • Note roc as is in parallel with rest of circuit g v m ro + vt it r − oc − v r RS + • Analysis is on pp. -

ECE 255, MOSFET Basic Configurations

ECE 255, MOSFET Basic Configurations 8 March 2018 In this lecture, we will go back to Section 7.3, and the basic configurations of MOSFET amplifiers will be studied similar to that of BJT. Previously, it has been shown that with the transistor DC biased at the appropriate point (Q point or operating point), linear relations can be derived between the small voltage signal and current signal. We will continue this analysis with MOSFETs, starting with the common-source amplifier. 1 Common-Source (CS) Amplifier The common-source (CS) amplifier for MOSFET is the analogue of the common- emitter amplifier for BJT. Its popularity arises from its high gain, and that by cascading a number of them, larger amplification of the signal can be achieved. 1.1 Chararacteristic Parameters of the CS Amplifier Figure 1(a) shows the small-signal model for the common-source amplifier. Here, RD is considered part of the amplifier and is the resistance that one measures between the drain and the ground. The small-signal model can be replaced by its hybrid-π model as shown in Figure 1(b). Then the current induced in the output port is i = −gmvgs as indicated by the current source. Thus vo = −gmvgsRD (1.1) By inspection, one sees that Rin = 1; vi = vsig; vgs = vi (1.2) Thus the open-circuit voltage gain is vo Avo = = −gmRD (1.3) vi Printed on March 14, 2018 at 10 : 48: W.C. Chew and S.K. Gupta. 1 One can replace a linear circuit driven by a source by its Th´evenin equivalence. -

Precision Current Sources and Sinks Using Voltage References

Application Report SNOAA46–June 2020 Precision Current Sources and Sinks Using Voltage References Marcoo Zamora ABSTRACT Current sources and sinks are common circuits for many applications such as LED drivers and sensor biasing. Popular current references like the LM134 and REF200 are designed to make this choice easier by requiring minimal external components to cover a broad range of applications. However, sometimes the requirements of the project may demand a little more than what these devices can provide or set constraints that make them inconvenient to implement. For these cases, with a voltage reference like the TL431 and a few external components, one can create a simple current bias with high performance that is flexible to fit meet the application requirements. Current sources and sinks have been covered extensively in other Texas Instruments application notes such as SBOA046 and SLYC147, but this application note will cover other common current sources that haven't been previously discussed. Contents 1 Precision Voltage References.............................................................................................. 1 2 Current Sink with Voltage References .................................................................................... 2 3 Current Source with Voltage References................................................................................. 4 4 References ................................................................................................................... 6 List of Figures 1 Current -

Basic DC Motor Circuits

Basic DC Motor Circuits Living with the Lab Gerald Recktenwald Portland State University [email protected] DC Motor Learning Objectives • Explain the role of a snubber diode • Describe how PWM controls DC motor speed • Implement a transistor circuit and Arduino program for PWM control of the DC motor • Use a potentiometer as input to a program that controls fan speed LWTL: DC Motor 2 What is a snubber diode and why should I care? Simplest DC Motor Circuit Connect the motor to a DC power supply Switch open Switch closed +5V +5V I LWTL: DC Motor 4 Current continues after switch is opened Opening the switch does not immediately stop current in the motor windings. +5V – Inductive behavior of the I motor causes current to + continue to flow when the switch is opened suddenly. Charge builds up on what was the negative terminal of the motor. LWTL: DC Motor 5 Reverse current Charge build-up can cause damage +5V Reverse current surge – through the voltage supply I + Arc across the switch and discharge to ground LWTL: DC Motor 6 Motor Model Simple model of a DC motor: ❖ Windings have inductance and resistance ❖ Inductor stores electrical energy in the windings ❖ We need to provide a way to safely dissipate electrical energy when the switch is opened +5V +5V I LWTL: DC Motor 7 Flyback diode or snubber diode Adding a diode in parallel with the motor provides a path for dissipation of stored energy when the switch is opened +5V – The flyback diode allows charge to dissipate + without arcing across the switch, or without flowing back to ground through the +5V voltage supply. -

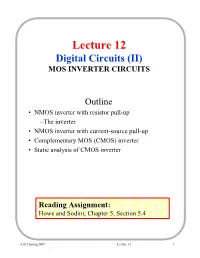

Lecture 12 Digital Circuits (II) MOS INVERTER CIRCUITS

Lecture 12 Digital Circuits (II) MOS INVERTER CIRCUITS Outline • NMOS inverter with resistor pull-up –The inverter • NMOS inverter with current-source pull-up • Complementary MOS (CMOS) inverter • Static analysis of CMOS inverter Reading Assignment: Howe and Sodini; Chapter 5, Section 5.4 6.012 Spring 2007 Lecture 12 1 1. NMOS inverter with resistor pull-up: Dynamics •CL pull-down limited by current through transistor – [shall study this issue in detail with CMOS] •CL pull-up limited by resistor (tPLH ≈ RCL) • Pull-up slowest VDD VDD R R VOUT: VOUT: HI LO LO HI V : VIN: IN C LO HI CL HI LO L pull-down pull-up 6.012 Spring 2007 Lecture 12 2 1. NMOS inverter with resistor pull-up: Inverter design issues Noise margins ↑⇒|Av| ↑⇒ •R ↑⇒|RCL| ↑⇒ slow switching •gm ↑⇒|W| ↑⇒ big transistor – (slow switching at input) Trade-off between speed and noise margin. During pull-up we need: • High current for fast switching • But also high incremental resistance for high noise margin. ⇒ use current source as pull-up 6.012 Spring 2007 Lecture 12 3 2. NMOS inverter with current-source pull-up I—V characteristics of current source: iSUP + 1 ISUP r i oc vSUP SUP _ vSUP Equivalent circuit models : iSUP + ISUP r r vSUP oc oc _ large-signal model small-signal model • High current throughout voltage range vSUP > 0 •iSUP = 0 for vSUP ≤ 0 •iSUP = ISUP + vSUP/ roc for vSUP > 0 • High small-signal resistance roc. 6.012 Spring 2007 Lecture 12 4 NMOS inverter with current-source pull-up Static Characteristics VDD iSUP VOUT VIN CL Inverter characteristics : iD = V 4 3 VIN VGS I + DD SUP roc 2 1 = vOUT vDS VDD (a) VOUT 1 2 3 4 VIN (b) High roc ⇒ high noise margins 6.012 Spring 2007 Lecture 12 5 PMOS as current-source pull-up I—V characteristics of PMOS: + S + VSG _ VSD G B − _ + IDp 5 V + D − V + G − V − D − ID(VSG,VSD) (a) = VSG 3.5 V 300 V = V + V = V − 1 V 250 (triode SD SG Tp SG region) V = 3 V 200 SG − IDp (µA) (saturation region) 150 = VSG 25 100 = 0, 0.5, VSG 1 V (cutoff region) V = 2 V 50 SG = VSG 1.5 V 12345 VSD (V) (b) Note: enhancement-mode PMOS has VTp <0.