An Algorithm for the Synthesis of NAND Logic Networks Using a Diagrammatic Approach

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Episode 5.02 – NAND Logic

Episode 5.02 – NAND Logic Welcome to the Geek Author series on Computer Organization and Design Fundamentals. I’m David Tarnoff, and in this series, we are working our way through the topics of Computer Organization, Computer Architecture, Digital Design, and Embedded System Design. If you’re interested in the inner workings of a computer, then you’re in the right place. The only background you’ll need for this series is an understanding of integer math, and if possible, a little experience with a programming language such as Java. And one more thing. Our topics involve a bit of figuring, so it might help to keep a pencil and paper handy. In our last episode, we covered three attributes of the sum-of-product expression including its general format and the benefits derived from it, a method to generate a truth table from a given sum-of- products expression, and lastly, a simple procedure we can use to create the proper sum-of-products expression from a given truth table. In this episode, we’re going to look at a fourth attribute. While this last trait may appear to be no more than an interesting exercise in Boolean algebra, it turns out that it offers several benefits when we implement our SOP expressions with digital circuitry. In Episode 4.08 – DeMorgan’s Theorem, we showed how an inverter can be distributed across the inputs of an AND or an OR gate by flipping the operation. In other words, we can distribute an inverter from the output of an AND gate across all the gate’s inputs as long as we change the gate operation to an OR. -

A Logic Synthesis Toolbox for Reducing the Multiplicative Complexity in Logic Networks

A Logic Synthesis Toolbox for Reducing the Multiplicative Complexity in Logic Networks Eleonora Testa∗, Mathias Soekeny, Heinz Riener∗, Luca Amaruz and Giovanni De Micheli∗ ∗Integrated Systems Laboratory, EPFL, Lausanne, Switzerland yMicrosoft, Switzerland zSynopsys Inc., Design Group, Sunnyvale, California, USA Abstract—Logic synthesis is a fundamental step in the real- correlates to the resistance of the function against algebraic ization of modern integrated circuits. It has traditionally been attacks [10], while the multiplicative complexity of a logic employed for the optimization of CMOS-based designs, as well network implementing that function only provides an upper as for emerging technologies and quantum computing. Recently, bound. Consequently, minimizing the multiplicative complexity it found application in minimizing the number of AND gates in of a network is important to assess the real multiplicative cryptography benchmarks represented as xor-and graphs (XAGs). complexity of the function, and therefore its vulnerability. The number of AND gates in an XAG, which is called the logic net- work’s multiplicative complexity, plays a critical role in various Second, the number of AND gates plays an important role cryptography and security protocols such as fully homomorphic in high-level cryptography protocols such as zero-knowledge encryption (FHE) and secure multi-party computation (MPC). protocols, fully homomorphic encryption (FHE), and secure Further, the number of AND gates is also important to assess multi-party computation (MPC) [11], [12], [6]. For example, the the degree of vulnerability of a Boolean function, and influences size of the signature in post-quantum zero-knowledge signatures the cost of techniques to protect against side-channel attacks. -

ECSE-4760 Real-Time Applications in Control & Communications

Rensselaer Polytechnic Institute ECSE-4760 Real-Time Applications in Control & Communications EXPERIMENTS IN DIGITAL LOGIC DESIGN Number of Sessions – 4 INTRODUCTION Over the past few decades the digital world has come into its own. Even though engineering has gone into specialization, it is necessary to understand digital circuits to be able to communicate with others. This experiment attempts to teach a simple method of designing digital circuits. Due to the quick pace of the lab, it is highly recommended that you read one of the references. This will enable you to proceed quickly through the preliminary problems so you will have more time for the design problems. The following is an outline of the experiment. Following each section will be a set of questions that should be answered to show an understanding of the material presented. Any difficulties should be referred to a reference or your instructor. You should use the DesignWorks (LogicWorks or any other you may have) logic circuit simulator on the Macintosh after most sections to cement together all the preceding sections. BACKGROUND THEORY Boolean Algebra Switching Algebra Combinational Logic Minimization Flip-Flops and Registers Counters Synthesis of Synchronous Circuits EXPERIMENTAL PROCEDURE Questions and Problems Simulator Operation & FPGA Implementation REFERENCES It is required that you show all circuits, as built, in your write-up. Please include equations too. The first part of the procedure section contains all the questions and problems to be answered and the second part describes the use of DesignWorks. Note: all references to DesignWorks (on Macintosh computers) throughout this procedure may be replaced with LogicWorks on the lab Windows PCs. -

Digital Logic Design

Digital Logic Design Chapter 3 Gate-Level Minimization Nasser M. Sabah Outline of Chapter 3 2 Introduction The Map Method Four-Variable Map Five-Variable Map Product of Sums Simplification NAND & NOR Implementation Other Two-Level Implementations Exclusive-OR Function Introduction 3 Gate-level minimization refers to the design task of finding an optimal gate-level implementation of Boolean functions describing a digital circuit. The Map Method 4 The complexity of the digital logic gates The complexity of the algebraic expression Logic minimization Algebraic approaches: lack specific rules The Karnaugh map A simple straight forward procedure A pictorial form of a truth table A diagram made up of squares Each square represents one minterm of the function that is to be minimized. Review of Boolean Function 5 Boolean function Sum of minterms Sum of products (or product of sum) in the simplest form A minimum number of terms A minimum number of literals The simplified expression may not be unique Two-Variable Map 6 A two-variable map Four minterms x' = row 0; x = row 1 y' = column 0; y = column 1 A truth table in square diagram Figure 3.1 Two-variable Map xy m3 xym 1 m 2 m 3 xyxy'' xy Representation of functions in the map Three-Variable Map 7 A three-variable map Eight minterms The Gray code sequence Any two adjacent squares in the map differ by only on variable. Primed in one square and unprimed in the other. e.g., m5 and m7 can be simplified. m57 m xy'(') z xyz xz y y xz Three-variable Map Three-Variable -

Lab 1: Study of Gates & Flip-Flops

Lab 1: Study of Gates & Flip-flops Aim To familiarize with circuit implementations using ICs and test the behavior of different logic gates and Flip-flops. Hardware Requirement a. Equipments - Digital IC Trainer Kit b. Discrete Components - 74LS00 Quad 2-Input NAND gate 74LS02 Quad 2-Input NOR gate 74LS04 Hex 1-Input NOT gate 74LS08 Quad 2-Input AND gate 74LS10 Triple 3-Input NAND gate 74LS11 Triple 3-Input AND gate 74LS32 Quad 2-Input OR gate 74LS86 Quad 2-Input XOR 74LS73 JK-Flip flop 74LS74 D Flip flop Background Digital logic devices are the circuits that electronically perform logic operations on binary variables. The binary information is represented by high and low voltage levels, which the device processes electronically. The devices that perform the simplest of the logic operations (such as AND, OR, NAND, etc.) are called gates. For example, an AND gate electronically computes the AND of the voltage encoded binary signals appearing at its inputs and presents the voltage encoded result at its output. The digital logic circuits used in this laboratory are contained in integrated circuit (IC) packages, with generally 14 or 16 pins for electrical connections. Each IC is labeled (usually with an 74LSxx number) to identify the logic it performs. The logic diagrams and pin connections for these IC’s are described in the TTL Data Book by Texas Instruments1. The transistor-transistor logic(TTL) IC’s used in this laboratory require a 5.0 volt power supply for operation. TTL inputs require a voltage greater than 2 volts to represent a binary 1 and a voltage less than 0.8 volts to represent a binary 0. -

Challenges and Solutions for Large-Scale Integration of Emerging

CHALLENGES AND SOLUTIONS FOR LARGE-SCALE INTEGRATION OF EMERGING TECHNOLOGIES A Dissertation IN Electrical and Computer Engineering and Physics Presented to the Faculty of the University of Missouri–Kansas City in partial fulfillment of the requirements for the degree DOCTOR OF PHILOSOPHY by Md Arif Iqbal B.Sc., Khulna University of Engineering and Technology, Khulna, Bangladesh, 2010 Kansas City, Missouri 2021 © 2021 MD ARIF IQBAL ALL RIGHTS RESERVED CHALLENGES AND SOLUTIONS FOR LARGE-SCALE INTEGRATION OF EMERGING TECHNOLOGIES Md Arif Iqbal, Candidate for the Doctor of Philosophy Degree University of Missouri–Kansas City, 2021 ABSTRACT The semiconductor revolution so far has been primarily driven by the ability to shrink devices and interconnects proportionally (Moore's law) while achieving incremental benefits. In sub-10nm nodes, device scaling reaches its fundamental limits, and the interconnect bottleneck is dominating power and performance. As the traditional way of CMOS scaling comes to an end, it is essential to find an alternative to continue this progress. However, an alternative technology for general-purpose computing remains elusive; currently pursued research directions face adoption challenges in all aspects from materials, devices to architecture, thermal management, integration, and manufacturing. Crosstalk Computing, a novel emerging computing technique, addresses some of the challenges and proposes a new paradigm for circuit design, scaling, and security. However, like other emerging technologies, Crosstalk Computing also faces challenges like designing large-scale circuits using existing CAD tools, scalability, evaluation and benchmarking of large-scale designs, experimentation through commercial foundry processes to compete/co- exist with CMOS for digital logic implementations. This dissertation addresses these issues by providing a methodology for circuit synthesis customizing the existing EDA tool flow, evaluating and benchmarking against state- of-the-art CMOS for large-scale circuits designed at 7nm from MCNC benchmark suits. -

Realization of Morphing Logic Gates in a Repressilator with Quorum Sensing Feedback

Realization of Morphing Logic Gates in a Repressilator with Quorum Sensing Feedback Vidit Agarwal, Shivpal Singh Kang and Sudeshna Sinha Indian Institute of Science Education and Research (IISER) Mohali, Knowledge City, SAS Nagar, Sector 81, Manauli PO 140 306, Punjab, India Abstract We demonstrate how a genetic ring oscillator network with quorum sensing feedback can operate as a robust logic gate. Specifically we show how a range of logic functions, namely AND/NAND, OR/NOR and XOR/XNOR, can be realized by the system, thus yielding a versatile unit that can morph between different logic operations. We further demonstrate the capacity of this system to yield complementary logic operations in parallel. Our results then indicate the computing potential of this biological system, and may lead to bio-inspired computing devices. arXiv:1310.8267v1 [physics.bio-ph] 30 Oct 2013 1 I. INTRODUCTION The operation of any computing device is necessarily a physical process, and this funda- mentally determines the possibilities and limitations of the computing machine. A common thread in the history of computers is the exploitation and manipulation of different natural phenomena to obtain newer forms of computing paradigms [1]. For instance, chaos comput- ing [2], neurobiologically inspired computing, quantum computing[3], and DNA computing[4] all aim to utilize, at the basic level, some of the computational capabilities inherent in natural systems. In particular, larger understanding of biological systems has triggered the interest- ing question: what new directions do bio-systems offer for understanding and implementing computations? The broad idea then, is to create machines that benefit from natural phenomena and utilize patterns inherent in systems to encode inputs and subsequently obtain a desired output. -

Majority Logic Synthesis Luca Amarù, Eleonora Testa, Miguel Couceiro, Odysseas Zografos, Giovanni De Micheli, Mathias Soeken

Majority logic synthesis Luca Amarù, Eleonora Testa, Miguel Couceiro, Odysseas Zografos, Giovanni de Micheli, Mathias Soeken To cite this version: Luca Amarù, Eleonora Testa, Miguel Couceiro, Odysseas Zografos, Giovanni de Micheli, et al.. Major- ity logic synthesis. ICCAD 2018 - IEEE/ACM International Conference on Computer-Aided Design, Nov 2018, San Diego, United States. 10.1145/3240765.3267501. hal-01925946 HAL Id: hal-01925946 https://hal.inria.fr/hal-01925946 Submitted on 2 Dec 2018 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. Majority logic synthesis (Embedded tutorial) Luca Amarù1 Eleonora Testa2 Miguel Couceiro3 Odysseas Zografos4 Giovanni De Micheli2 Mathias Soeken2 1Synopsys Inc., USA 2 EPFL, Switzerland 3Université de Lorraine, France 4imec, Belgium Abstract—The majority function hxyzi evaluates to true, if at s least two of its Boolean inputs evaluate to true. The majority function has frequently been studied as a central primitive in logic synthesis applications for many decades. Knuth refers to cout the majority function in the last volume of his seminal The Art of Computer Programming as “probably the most impor- tant ternary operation in the entire universe.” Majority logic sythesis has recently regained signficant interest in the design automation community due to nanoemerging technologies which a b cin operate based on the majority function. -

Universal Gate - NOR Digital Electronics 2.2 Intro to NAND & NOR Logic

Universal Gate - NOR Digital Electronics 2.2 Intro to NAND & NOR Logic Universal Gate – NOR This presentation will demonstrate… • The basic function of the NOR gate. • How an NOR gate can be using to replace an AND gate, an OR gate or an INVERTER gate. • How a logic circuit implemented with AOI logic gates Universal Gate – NOR could be re-implemented using only NOR gates • That using a single gate type, in this case NOR, will reduce the number of integrated circuits (IC) required to implement a logic circuit. Digital Electronics AOI Logic NOR Logic 2 More ICs = More $$ Less ICs = Less $$ NOR Gate NOR Gate as an Inverter Gate X X X (Before Bubble) X Z X Y X Y X Z X Y X Y Z X Z 0 0 1 0 1 Equivalent to Inverter 0 1 0 1 0 1 0 0 1 1 0 3 4 Project Lead The Way, Inc. Copyright 2009 1 Universal Gate - NOR Digital Electronics 2.2 Intro to NAND & NOR Logic NOR Gate as an OR Gate NOR Gate as an AND Gate X X Y Y X X Z X Y X Y Y Z X Y X Y X Y Y NOR Gate “Inverter” “Inverters” NOR Gate X Y Z X Y Z 0 0 0 0 0 0 0 1 1 0 1 0 Equivalent to OR Gate Equivalent to AND Gate 1 0 1 1 0 0 1 1 1 1 1 1 5 6 NOR Gate Equivalent of AOI Gates Process for NOR Implementation 1. -

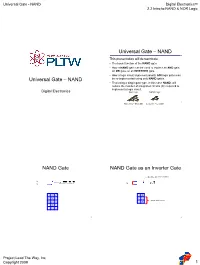

Universal Gate - NAND Digital Electronics 2.2 Intro to NAND & NOR Logic

Universal Gate - NAND Digital Electronics 2.2 Intro to NAND & NOR Logic Universal Gate – NAND This presentation will demonstrate • The basic function of the NAND gate. • How a NAND gate can be used to replace an AND gate, an OR gate, or an INVERTER gate. • How a logic circuit implemented with AOI logic gates can Universal Gate – NAND be re-implemented using only NAND gates. • That using a single gate type, in this case NAND, will reduce the number of integrated circuits (IC) required to implement a logic circuit. Digital Electronics AOI Logic NAND Logic 2 More ICs = More $$ Less ICs = Less $$ NAND Gate NAND Gate as an Inverter Gate X X X (Before Bubble) X Z X Y X Y X Z X Y X Y Z X Z 0 0 1 0 1 Equivalent to Inverter 0 1 1 1 0 1 0 1 1 1 0 3 4 Project Lead The Way, Inc Copyright 2009 1 Universal Gate - NAND Digital Electronics 2.2 Intro to NAND & NOR Logic NAND Gate as an AND Gate NAND Gate as an OR Gate X X Y Y X X Z X Y X Y Y Z X Y X Y X Y Y NAND Gate Inverter Inverters NAND Gate X Y Z X Y Z 0 0 0 0 0 0 0 1 0 0 1 1 Equivalent to AND Gate Equivalent to OR Gate 1 0 0 1 0 1 1 1 1 1 1 1 5 6 NAND Gate Equivalent to AOI Gates Process for NAND Implementation 1. -

New Approaches for Memristive Logic Computations

Portland State University PDXScholar Dissertations and Theses Dissertations and Theses 6-6-2018 New Approaches for Memristive Logic Computations Muayad Jaafar Aljafar Portland State University Let us know how access to this document benefits ouy . Follow this and additional works at: https://pdxscholar.library.pdx.edu/open_access_etds Part of the Electrical and Computer Engineering Commons Recommended Citation Aljafar, Muayad Jaafar, "New Approaches for Memristive Logic Computations" (2018). Dissertations and Theses. Paper 4372. 10.15760/etd.6256 This Dissertation is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. For more information, please contact [email protected]. New Approaches for Memristive Logic Computations by Muayad Jaafar Aljafar A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering Dissertation Committee: Marek A. Perkowski, Chair John M. Acken Xiaoyu Song Steven Bleiler Portland State University 2018 © 2018 Muayad Jaafar Aljafar Abstract Over the past five decades, exponential advances in device integration in microelectronics for memory and computation applications have been observed. These advances are closely related to miniaturization in integrated circuit technologies. However, this miniaturization is reaching the physical limit (i.e., the end of Moore’s Law). This miniaturization is also causing a dramatic problem of heat dissipation in integrated circuits. Additionally, approaching the physical limit of semiconductor devices in fabrication process increases the delay of moving data between computing and memory units hence decreasing the performance. The market requirements for faster computers with lower power consumption can be addressed by new emerging technologies such as memristors. -

Design of a High Reliability Self Diagnosing Computer Using Bit Slice Microprocessors

North-Holland 325 Microprocessing and Microprogramming 22 (1 988) 325-331 Design of a High Reliability Self Diagnosing Computer Using Bit Slice Microprocessors S. Sanyal and P.V.S. Rao 2. Design Options Computer Systems & Communications Group, Tata Institute of FundamentalResearch, Bombay-400005, India 2.1 Functional Design This paper describes a processor built to meet the require- ments for a highly reliable and ruggedised digital computer. To achieve the desirable level of reliability and Innovative techniques were used to achieve high performance speed, several design options were considered: without using very high reliability components or redundancy at the circuit level. The processor therefore was designed us- (a) In a standard design using very high reliability ing moderately reliable components (mil B standard) with mi- components (MIL A Standard), the cost factor is croprogrammed control logic and powerful built-in microdi- prohibitive. Also a standard design using MIL A agnostic capabilities. It was successfully used for two major applications: a digital switching system and a data acquisition standard components still presupposes continuous and processing system for a weather radar. functioning of the components. The probability of failure is reduced, but the time required for repair Keywords: Reliability, Microprogramming, Microdiagnostics. does not decrease. 1. Introduction (b) Using moderately reliable components (MIL B Standard) in a design which provides for automatic A need arose for the development of a rugged digit- fault identification permits quick replacement of the al computer to form the nucleus of complex online faulty submodule. A high Mean Time Between systems required for two major applications: a gen- Failures and a low Mean Time to Repair can both eral purpose medium-size digital switching system be achieved.