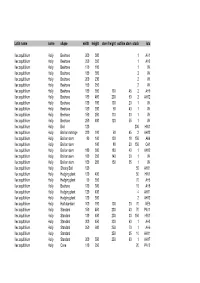

Pin Information for the Arria® GX EP1AGX50C/D Device

Version 1.4

Bank Number

- VREF Group Pin Name/Function

- Optional Function(s)

- Configuration

Function

- x8/x9 Mode

- x16/x18 Mode

- x36 Mode

VCCD_PLL7 VCCA_PLL7 GNDA_PLL7 GNDA_PLL7

K25 J26 K26 J25 C34 C33 J28 K27 E34 D34 J30 J29 F32 F31 K30 K29 R30 F34 F33 L26 L25 G33 G32 M26 M25 H32 H31 K28 L28 G34 H34 L29

- B2

- VREFB2N0

VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0

- FPLL7CLKp

- INPUT

B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2

- FPLL7CLKn

- INPUT

- IO

- DIFFIO_TX41p

DIFFIO_TX41n DIFFIO_RX40p DIFFIO_RX40n DIFFIO_TX40p DIFFIO_TX40n DIFFIO_RX39p DIFFIO_RX39n DIFFIO_TX39p DIFFIO_TX39n VREFB2N0

IO IO IO IO IO IO IO IO IO

- VREFB2N0

- T21

- J18

IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO

DIFFIO_RX38p DIFFIO_RX38n DIFFIO_TX38p DIFFIO_TX38n DIFFIO_RX37p DIFFIO_RX37n DIFFIO_TX37p DIFFIO_TX37n DIFFIO_RX36p DIFFIO_RX36n DIFFIO_TX36p DIFFIO_TX36n DIFFIO_RX35p DIFFIO_RX35n DIFFIO_TX35p

C28 C27 H23 H22 D28 D27 F24

B20 B19 D19 D18 A17 B17 C20

PT-EP1AGX50C/D-1.4 Copyright © 2009 Altera Corp.

- Pin List

- Page 1 of 47

Pin Information for the Arria® GX EP1AGX50C/D Device

Version 1.4

Bank Number

- VREF Group Pin Name/Function

- Optional Function(s)

- Configuration

Function

- x8/x9 Mode

- x16/x18 Mode

- x36 Mode

- B2

- VREFB2N0

VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N1 VREFB2N2 VREFB2N2

- IO

- DIFFIO_TX35n

DIFFIO_RX34p DIFFIO_RX34n DIFFIO_TX34p DIFFIO_TX34n DIFFIO_RX33p DIFFIO_RX33n DIFFIO_TX33p DIFFIO_TX33n DIFFIO_RX32p DIFFIO_RX32n DIFFIO_TX32p DIFFIO_TX32n VREFB2N1

M29 J32

F23 F27 F26 G24 G23 E28 F28 E26 E25 G28 G27 K24 J23

C19 A19 A18 D20 E20 A21 A20 F20 F19 B22 A22 G19 G18 H19 C22 C21 F18 F17 D22 D21 G17 G16 E22 F22 H16 J16

B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2

IO

- IO

- J31

- IO

- M28

M27 J34

IO IO

- IO

- J33

- IO

- N27

N26 K33 K32 N25 N24 M30 L32 L31 N23 P23 L34 K34 N29 N28 M32 M31 P29 P28 M34 M33 R29 R28 N31 N30

IO IO IO IO IO VREFB2N1 IO

M23

- J27

- DIFFIO_RX31p

DIFFIO_RX31n DIFFIO_TX31p DIFFIO_TX31n DIFFIO_RX30p DIFFIO_RX30n DIFFIO_TX30p DIFFIO_TX30n DIFFIO_RX29p DIFFIO_RX29n DIFFIO_TX29p DIFFIO_TX29n DIFFIO_RX28p DIFFIO_RX28n DIFFIO_TX28p DIFFIO_TX28n DIFFIO_RX27p DIFFIO_RX27n

- IO

- J26

- IO

- K22

K21 H28 J28

IO IO IO

- IO

- K23

L23 L26 L25 G26 G25 K28 K27 M22 M21 M27 M26

IO IO IO IO IO

- IO

- F21

G21 K15 K14 G20 H20

IO IO IO IO IO

PT-EP1AGX50C/D-1.4 Copyright © 2009 Altera Corp.

- Pin List

- Page 2 of 47

Pin Information for the Arria® GX EP1AGX50C/D Device

Version 1.4

Bank Number

- VREF Group Pin Name/Function

- Optional Function(s)

- Configuration

Function

- x8/x9 Mode

- x16/x18 Mode

- x36 Mode

- B2

- VREFB2N2

VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2 VREFB2N2

- IO

- DIFFIO_TX27p

DIFFIO_TX27n DIFFIO_RX26p DIFFIO_RX26n DIFFIO_TX26p DIFFIO_TX26n DIFFIO_RX25p DIFFIO_RX25n DIFFIO_TX25p DIFFIO_TX25n DIFFIO_RX24p DIFFIO_RX24n DIFFIO_TX24p DIFFIO_TX24n VREFB2N2

R23 T23 N33 N32 T29 T28 P32 P31 U24 U23 N34 P34 U31 U30 K31 R32 R31 U29 U28 R34 R33 W29 V29 T32 T31 U27 V28 T34 U34 U32 U33 R27

- J25

- J17

B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2

- IO

- J24

- K16

G22 H22 L16 L15 J22

- IO

- L28

M28 H26 H25 N28 P28 K26 K25 N26 N25 M25 M24 F25 P27 P26 P25 P24 R28 T28 M20 N20 T27 T26 R21 R20 R25 R26 T24 T25 N22

IO IO IO IO

- IO

- J21

- IO

- M14

N14 J20

IO IO

- IO

- J19

- IO

- M16

M15 E19 K22 K21 K20 K19 L22 L21 N16 N15 L20 L19 P16 P15 M21 M22 M19 M20 K17

IO VREFB2N2

- IO

- DIFFIO_RX23p

DIFFIO_RX23n DIFFIO_TX23p DIFFIO_TX23n DIFFIO_RX22p DIFFIO_RX22n DIFFIO_TX22p DIFFIO_TX22n DIFFIO_RX21p DIFFIO_RX21n DIFFIO_TX21p DIFFIO_TX21n CLK0n/DIFFIO_RX_C0n CLK0p/DIFFIO_RX_C0p INPUT

IO IO IO IO IO IO IO IO IO IO IO IO IO CLK1n CLK1p VCCD_PLL1

INPUT

PT-EP1AGX50C/D-1.4 Copyright © 2009 Altera Corp.

- Pin List

- Page 3 of 47

Pin Information for the Arria® GX EP1AGX50C/D Device

Version 1.4

Bank Number

- VREF Group Pin Name/Function

- Optional Function(s)

- Configuration

Function

- x8/x9 Mode

- x16/x18 Mode

- x36 Mode

VCCA_PLL1 GNDA_PLL1 GNDA_PLL1 GNDA_PLL2 GNDA_PLL2 VCCA_PLL2 VCCD_PLL2

- T25

- N23

P23 P22 R23 R22 T23

K18 L17 L18 M17 M18 N18 N17 N22 N21 N20 N19 P22 P21 T15 T14 P20 P19 T16 U16 U19 R22 T22 P17 R16 T21 T20 V17 W17 U21 U20 U18 U17

T26 R26 W26 V26 V25 W27 W34 V34

T22

- B1

- VREFB1N0

VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N0

- IO

- CLK2p/DIFFIO_RX_C1p

CLK2n/DIFFIO_RX_C1n INPUT

U28 U27 U26 U25 V28 W28 T19

B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1

IO

- CLK3p

- V32

- CLK3n

- INPUT

- V31

- IO

- DIFFIO_RX20p

DIFFIO_RX20n DIFFIO_TX20p DIFFIO_TX20n DIFFIO_RX19p DIFFIO_RX19n DIFFIO_TX19p DIFFIO_TX19n VREFB1N0

W31 W30 V23

IO IO

- IO

- W23

W33 W32 Y24

U19 Y28 AA28 U20 V20 AD23 W27 W26 Y25 Y24 Y27 Y26 U24 U23 V26 V25 AA26 AA25

IO IO IO

- IO

- Y23

- VREFB1N0

- AE31

- Y32

- IO

IO IO IO IO IO IO IO IO IO IO IO

DIFFIO_RX18p DIFFIO_RX18n DIFFIO_TX18p DIFFIO_TX18n DIFFIO_RX17p DIFFIO_RX17n DIFFIO_TX17p DIFFIO_TX17n DIFFIO_RX16p DIFFIO_RX16n DIFFIO_TX16p DIFFIO_TX16n

Y31 W28 Y29 Y34 Y33 Y28 Y27 AA32 AA31 AA29 AA28

PT-EP1AGX50C/D-1.4 Copyright © 2009 Altera Corp.

- Pin List

- Page 4 of 47

Pin Information for the Arria® GX EP1AGX50C/D Device

Version 1.4

Bank Number

- VREF Group Pin Name/Function

- Optional Function(s)

- Configuration

Function

- x8/x9 Mode

- x16/x18 Mode

- x36 Mode

- B1

- VREFB1N0

VREFB1N0 VREFB1N0 VREFB1N0 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1 VREFB1N1

- IO

- DIFFIO_RX15p

DIFFIO_RX15n DIFFIO_TX15p DIFFIO_TX15n DIFFIO_RX14p DIFFIO_RX14n DIFFIO_TX14p DIFFIO_TX14n DIFFIO_RX13p DIFFIO_RX13n DIFFIO_TX13p DIFFIO_TX13n DIFFIO_RX12p DIFFIO_RX12n DIFFIO_TX12p DIFFIO_TX12n VREFB1N1

AB31 AB30 AA23 AB23 AB33 AB32 AA26 AA25 AA34 AB34 AB29 AB28 AC32 AC31 AB24 AC24 AC30 AC34 AC33 AB26 AB25 AD32 AD31 AC27 AB27 AE33 AE32 AD26 AD25 AD34 AE34 AC29

AB28 AB27 V23

U22

B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1

- IO

- V22

- IO

- R17

- IO

- V22

- T17

- IO

- AC28

AD28 W21

W22 W21 W19 W18 Y22

IO IO

- IO

- Y21

- IO

- AD26

AD25 AC25 AC24 W25

- IO

- Y21

- IO

- Y19

- IO

- Y18

- IO

- AA22

AB22 V20

- IO

- W24

- IO

- AB22

AB21 Y23

- IO

- V19

VREFB1N1 IO

R20

DIFFIO_RX11p DIFFIO_RX11n DIFFIO_TX11p DIFFIO_TX11n DIFFIO_RX10p DIFFIO_RX10n DIFFIO_TX10p DIFFIO_TX10n DIFFIO_RX9p DIFFIO_RX9n DIFFIO_TX9p DIFFIO_TX9n DIFFIO_RX8p DIFFIO_RX8n DIFFIO_TX8p

AC27 AC26 AE26 AE25 AB26 AB25 AB24 AB23 AE28 AE27 AC23 AC22 AF28 AF27 AA23

AB21 AB20 R19

IO IO

- IO

- T19

- IO

- AB19

AB18 AB17 AA17 AA20 AA19 AA16 Y17

IO IO IO IO IO IO IO

- IO

- W20

- Y20

- IO

- IO

- AB16

PT-EP1AGX50C/D-1.4 Copyright © 2009 Altera Corp.

- Pin List

- Page 5 of 47

Pin Information for the Arria® GX EP1AGX50C/D Device

Version 1.4

Bank Number

- VREF Group Pin Name/Function

- Optional Function(s)

- Configuration

Function

- x8/x9 Mode

- x16/x18 Mode

- x36 Mode

- B1

- VREFB1N1

VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2 VREFB1N2

- IO

- DIFFIO_TX8n

DIFFIO_RX7p DIFFIO_RX7n DIFFIO_TX7p DIFFIO_TX7n DIFFIO_RX6p DIFFIO_RX6n DIFFIO_TX6p DIFFIO_TX6n DIFFIO_RX5p DIFFIO_RX5n DIFFIO_TX5p DIFFIO_TX5n DIFFIO_RX4p DIFFIO_RX4n DIFFIO_TX4p DIFFIO_TX4n VREFB1N2

AC28 AF32 AF31 AD29 AD28 AF34 AF33 AE30 AE29 AG32 AG31 AE28 AE27 AG34 AH34 AF30 AF29 Y30

- AA22

- AB15

B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1 B1

IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO

- VREFB1N2

- W23

- P18

- IO

- DIFFIO_RX3p

DIFFIO_RX3n DIFFIO_TX3p DIFFIO_TX3n DIFFIO_RX2p DIFFIO_RX2n DIFFIO_TX2p DIFFIO_TX2n DIFFIO_RX1p DIFFIO_RX1n DIFFIO_TX1p DIFFIO_TX1n INPUT

AH33 AH32 AF28 AF27 AJ34 AJ33 AG29 AG28 AJ32 AJ31 AH31 AH30 AM33 AM34

IO IO IO IO IO IO IO IO IO IO IO FPLL8CLKn

- FPLL8CLKp

- INPUT

PT-EP1AGX50C/D-1.4 Copyright © 2009 Altera Corp.

- Pin List

- Page 6 of 47

Pin Information for the Arria® GX EP1AGX50C/D Device

Version 1.4

Bank Number

- VREF Group Pin Name/Function

- Optional Function(s)

- Configuration

Function

- x8/x9 Mode

- x16/x18 Mode

- x36 Mode

- B1

- VREFB1N2

VREFB1N2

- IO

- DIFFIO_TX0p

DIFFIO_TX0n

AH29 AH28 AF25 AE26 AF26 AE25 AL31 AM32 AE24 AM31 AL30 AF24 AL29 AH27 AH26 AG26 AG25 AH24 AH25 AM30 AN31 AK28 AN32 AP32 AP30 AP31 AE23 AF23 AP29 AN29 AM29 AP28

- B1

- IO

GNDA_PLL8 GNDA_PLL8 VCCA_PLL8 VCCD_PLL8

B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8

VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0

- TDI

- TDI

- V19

W19 V17 W17 V16 W18

AA14

- Y16

- TMS

- TMS

- TCK

- TCK

- AB13

AB14 Y15

- TRST

- TRST

nCONFIG VCCSEL nCONFIG

- VCCSEL

- AB12

IO

- IO

- CS

- AE24

AC21 AE22 AE21

Y14

- IO

- CLKUSR

nWS

AA11 AA13 AB11

IO

- IO

- nRS

IO IO

- IO

- DQ17B

- AF26

AF25 AD22 AG26 AH25 AH26 AG25 AD20

DQ8B DQ8B

DQ3B

- DQ3B

- IO

- DQ3B

- DQ1B

- DQ1B

- VREFB8N0

- VREFB8N0

DQ17B

W16 W15

IO IO IO IO IO IO IO IO IO IO

DQ8B DQ8B DQ8B

DQ3B DQ3B DQ3B

DQ3B DQ3B DQ3B

DQ1B DQ1B DQ1B

- DQ17B

- DQ1B

- DQ1B

- DQ17B

DQS17B

- DQ16B

- AE20

W16

- DQ8B

- DQ3B

DQ3B DQ3B DQ3B

DQ1B DQ1B DQ1B DQ1B

DQ16B DQ16B

DQ8B DQ8B

PT-EP1AGX50C/D-1.4 Copyright © 2009 Altera Corp.

- Pin List

- Page 7 of 47

Pin Information for the Arria® GX EP1AGX50C/D Device

Version 1.4

Bank Number

- VREF Group Pin Name/Function

- Optional Function(s)

- Configuration

Function

- x8/x9 Mode

- x16/x18 Mode

- x36 Mode

- B8

- VREFB8N0

VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N0 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1 VREFB8N1

- IO

- DQ16B

- AM28

AN28 AC23 AJ27 AL28 AJ28 AM27 AP27 AL27 AF22 AG22 AN26 AL26 AJ26 AK26 AP26 AM26 AC22 AJ24 AL25 AK25 AJ25 AN25 AP25 AM25 AB21 AM24 AL24 AJ23 AK23 AP24 AL23

- AC20

- DQ8B

- DQ3B

- DQ1B

B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8 B8

- IO

- DQS16B

- DQS8B

IO

- IO

- DQ15B

- AH24

AF23 AF24 AF22 AH23 AG23

DQ7B DQ7B DQ7B DQ7B DQ7B

- DQ3B

- DQ3B

- DQ1B

DQ1B DQ1B DQ1B DQ1B

DQ1B DQ1B DQ1B DQ1B DQ1B

IO

- IO

- DQ15B

DQ15B DQ15B DQS15B

DQ3B DQ3B DQ3B DQS3B

DQ3B DQ3B DQ3B DQS3B

IO IO IO IO IO

- IO

- DQ14B

- AE19

AB19 AC19

- DQ7B

- DQ3B

DQ3B DQ3B DQ3B DQ3B

DQ1B DQ1B DQ1B DQ1B DQ1B

IO

- IO

- DQ14B

DQ14B DQ14B DQS14B

DQ7B DQ7B DQ7B DQS7B

IO IO IO IO

- IO

- DQ13B

- AG22

AF20 AD19 AH22 AH21 AF21 AG20

W14 V16

DQ6B DQ6B

DQ2B DQ2B

DQ1B

- IO

- DQ2B

VREFB8N1 IO

VREFB8N1

- DQ13B

- DQ6B

DQ6B DQ6B

DQ2B DQ2B DQ2B

DQ2B DQ2B DQ2B

DQ1B DQ1B DQ1B DQS1B

DQ1B DQ1B DQ1B DQS1B

- IO

- DQ13B

- IO

- DQ13B

- IO

- DQS13B

IO

- IO

- DQ12B

- AE18

W15

- DQ6B

- DQ2B

DQ2B DQ2B DQ2B DQ2B

DQ1B DQ1B DQ1B DQ1B DQ1B

IO

- IO

- DQ12B

DQ12B DQ12B DQS12B

DQ6B DQ6B DQ6B DQS6B

IO

- IO

- AC18

IO