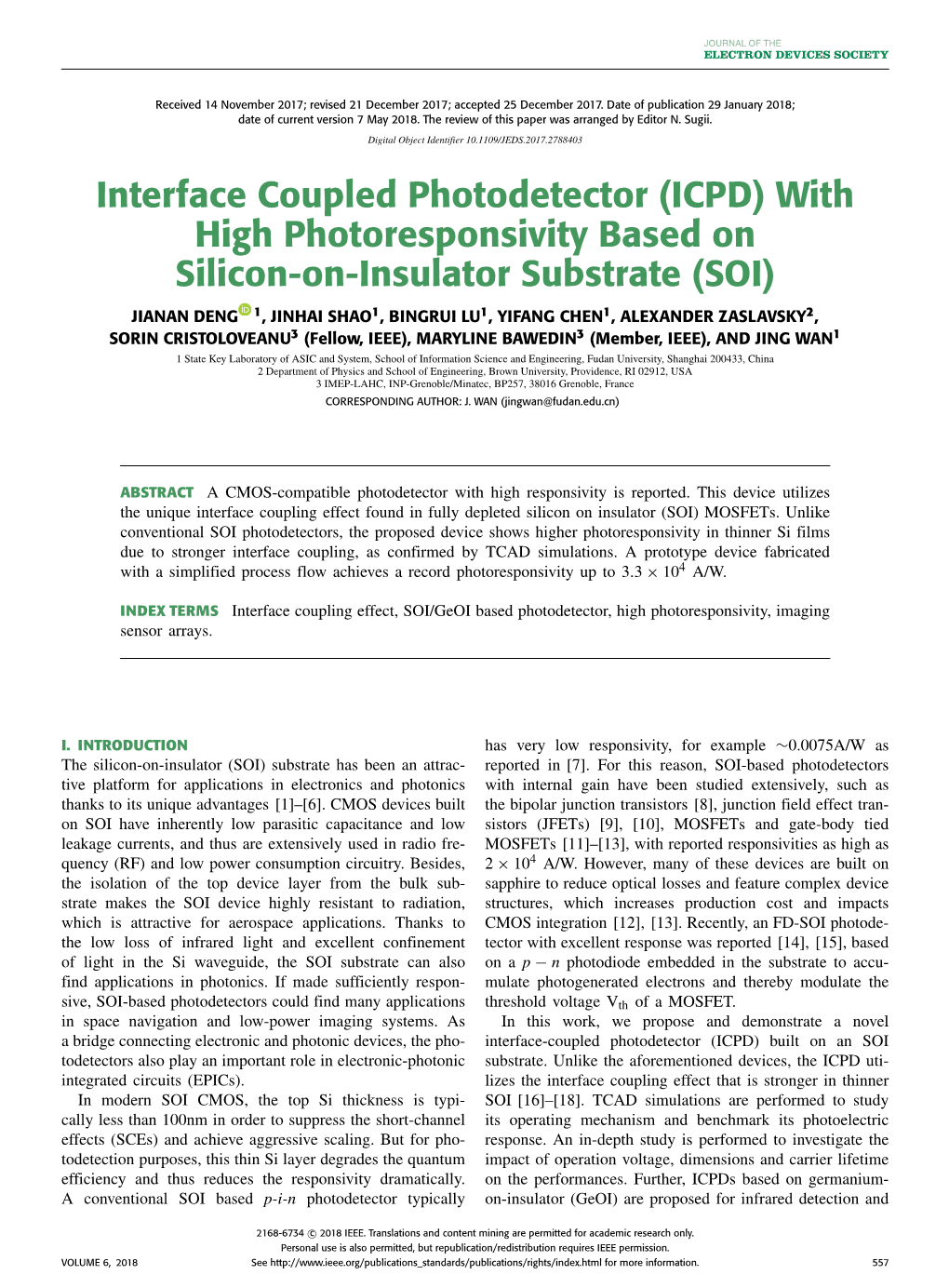

Interface Coupled Photodetector (ICPD) with High Photoresponsivity Based on Silicon-On-Insulator Substrate (SOI)

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Fabrication of Group IV Semiconductors on Insulator for Monolithic 3D Integration

Fabrication of Group IV Semiconductors on Insulator for Monolithic 3D Integration Ali Asadollahi Doctoral Thesis in Information and Communication Technology School of Electrical Engineering and Computer Science KTH Royal Institute of Technology Stockholm, Sweden 2017 KTH School of Electrical Engineering and Computer TRITA-EECS-AVL-2018:1 Science ISBN: 978-91-7729-658-4 SE-164 40 Stockholm SWEDEN Akademisk avhandling som med tillstånd av Kungliga Tekniska högskolan framlägges till offentlig granskning för avläggande av teknologie doktorsexamen fredagen den 16 februari 2018 klockan 10:00 i Ka-Sal C (Sal Sven-Olof Öhrvik), Electrum, Kungliga Tekniska högskolan, Kistagången 16, Kista. ©Ali Asadollahi, December 2017 Tryck: Universitetsservice US-AB, Stockholm, 2017 ii To My Parents “All the different nations in the world, despite their differences of appearance and language and the way of life, still have one thing in common, and that is what's inside in all of us. If we X-rayed the insides of different human beings, we wouldn't be able to tell from those X-rays what the person's language or background or race is.” Abbas Kiarostami iv Abstract The conventional 2D geometrical scaling of transistors is now facing many challenges in order to continue the performance enhancement while decreasing power consumption. The decrease in the device power consumption is related to the scaling of the power supply voltage (Vdd) and interconnects wiring length. In addition, monolithic three dimensional (M3D) integration in the form of vertically stacked devices, is a possible solution to increase the device density and reduce interconnect wiring length. Integrating strained germanium on insulator (sGeOI) pMOSFETs monolithically with strained silicon/silicon-germanium on insulator (sSOI/sSiGeOI) nMOSFETs can increase the device performance and packing density. -

Photodiode and LIGHT EMITTING DIODE

Photodiode and LIGHT EMITTING DIODE Presentation by JASWANT KUMAR ROLL NO.-12 rd IT(3 SEM.) 1 About LEDs (1/2) • A light emitting diode (LED) is essentially a PN junction opto- semiconductor that emits a monochromatic (single color) light when operated in a forward biased direction. • LEDs convert electrical energy into light energy. LED SYMBOL 2 ABOUT LEDS (2/2) • The most important part of a light emitting diode (LED) is the semi-conductor chip located in the center of the bulb as shown at the right. • The chip has two regions separated by a junction. • The junction acts as a barrier to the flow of electrons between the p and the n regions. 3 LED CIRCUIT • In electronics, the basic LED circuit is an electric power circuit used to power a light-emitting diode or LED. The simplest such circuit consists of a voltage source and two components connect in series: a current-limiting resistor (sometimes called the ballast resistor), and an LED. Optionally, a switch may be introduced to open and close the circuit. The switch may be replaced with another component or circuit to form a continuity tester. 4 HOW DOES A LED WORK? • Each time an electron recombines with a positive charge, electric potential energy is converted into electromagnetic energy. • For each recombination of a negative and a positive charge, a quantum of electromagnetic energy is emitted in the form of a photon of light with a frequency characteristic of the semi- conductor material. 5 Mechanism behind photon emission in LEDs? MechanismMechanism isis “injection“injection Electroluminescence”.Electroluminescence”. -

DESIGN and EVALUATION of CONTROLS for DRIFT, VIDEO GAIN, and COLOR BALANCE in SPACEBORNE FACSIMILE CAMERAS by Stephen J. Katrber

NASA TECHNICAL NOTE @ NASA Tli D-73.3 m % & m U.S.A. m (NASA-TN-D-7333) DESIGN AND EVALUATION OP CONTROLS FOR DRIFT, VIDEO GAIN, AND COLOR BALANCE IN SPACEBORNE FACSIMILE CAMERAS (NASA) 33 p HC $3.00 CSCL 14E Unclas 4 81/10 23462 Z DESIGN AND EVALUATION OF CONTROLS FOR DRIFT, VIDEO GAIN, AND COLOR BALANCE IN SPACEBORNE FACSIMILE CAMERAS by Stephen J. Katrberg, W. Lane Kelly IV, QR~Q~F~&$.MH?AlMS Carroll W. Rowland, and Ernest E. Burcher GQdhU.* . .b"'3H8 Langley Research Center Humpton, Vu. 23665 NATIONAL AERONAUTICS AND SPACE ADMINISTRATION WASHINGTON, D. C. DECEMBER 1973 1. Report No. a. Government Accasrion No. 3. Recipient's Catalog No. NASA TN D-7333 4. Title and Subtitle 5. Report Date DESIGN AND EVALUATION OF CONTROLS FOR DRIFT, December 1973 VIDEO GAIN, AND COLOR BALANCE IN SPACEBORNE 6. Performing Organization Code FACSIMILE CAMERAS 7. Author(s1 8. Performing Organization Rwrt No. Stephen J. Katzberg, W. Lane Kelly IV, Carroll W. Rowland, L-8845 and Ernest E. Burcher 10. Work Unit No. g. Rrforming Organintion Name and Addrerr 502-03-52-04 NASA Langley Research Center 11. Contract or Grant No. Hampton, Va. 23665 13. Type of Repon and Period Covered 12. Sponsoring Agency Name and Addresr Technical Note National Aeronautics and Space Administration 14. Sponsoring Agency Code Washington, D.C. 20546 15:' Subplementary Notes 16. AbsuaR The facsimile camera is an optical-mechanical scanning device which has become an attractive candidate as an imaging system for planetary landers and rovers. This paper presents electronic techniques which permit the acquisition and reconstruction of high-quality images with this device, even under varying lighting conditions. -

Integrated High-Speed, High-Sensitivity Photodiodes and Optoelectronic Integrated Circuits

Sensors and Materials, Vol. 13, No. 4 (2001) 189-206 MYUTokyo S &M0442 Integrated High-Speed, High-Sensitivity Photodiodes and Optoelectronic Integrated Circuits Horst Zimmermann Institut fiirElektrische Mess- und Schaltungstechnik, Technische Universitat Wien, Gusshausstrasse, A-1040 Wien, Austria (Received February 28, 2000; accepted February3, 2001) Key words: integrated circuits, integrated optoelectronics, optical receivers, optoelectronic de vices, PIN photodiode, double photodiode, silicon A review of the properties of photodiodes available through the use of standard silicon technologies is presented and some examples of how to improve monolithically integrated photodiodes are shown. The application of these photodiodes in optoelectronic integrated circuits (OEICs) is described. An innovative double photodiode requiring no process modificationsin complementary metal-oxide sem!conductor (CMOS) and bipolar CMOS (BiCMOS) technologies achieves a bandwidth in excess of 360 MHzand data rates exceeding 622 Mb/s. Furthermore, a new PIN photodiode requiring only one additional mask for the integration in a CMOS process is capable of handling a data rate of 1.1 Gb/s. Antireflection coating improves the quantum efficiencyof integrated photodiodes to values of more than 90%. Integrated optical receivers for data communication achieve a high bandwidth and a high sensitivity. Furthermore, an OEIC for application in optical storage systems is introduced. Author's e-mail address: [email protected] 189 l 90 Sensors and Materials, Vol. 13, No. 4 (2001) 1. Introduction Photons with an energy larger than the band gap generate electron-hole pairs in semiconductors. This photogeneration G obeys an exponential law: aP,0 G( x) = -- exp( -ax), Ahv (1) where xis the penetration depth coordinate, P0 is the nonreflectedportion of the incident optical power, A is the light-sensitive area of a photodiode, hv is the energy of the photon, and a is the wavelength-dependent absorption coefficient. -

Leds As Single-Photon Avalanche Photodiodes by Jonathan Newport, American University

LEDs as Single-Photon Avalanche Photodiodes by Jonathan Newport, American University Lab Objectives: Use a photon detector to illustrate properties of random counting experiments. Use limiting probability distributions to perform statistical analysis on a physical system. Plot histograms. Condition a detector’s signal for further electronic processing. Use a breadboard, power supply and oscilloscope to construct a circuit and make measurements. Learn about semiconductor device physics. Reading: Taylor 3.2 – The Square-Root Rule for a Counting Experiment pp. 48-49 Taylor 5.1-5.3 – Histograms and the Normal Distribution pp. 121-135 Taylor Ch. 11 – The Poisson Distribution pp. 245-254 Taylor Problem 5.6 – The Exponential Distribution p. 155 Experiment #1: Lighting an LED A Light-Emitting Diode is a non-linear circuit element that can produce a controlled amount of light. The AND113R datasheet shows that the luminous intensity is proportional to the current flowing through the LED. As illustrated in the IV curve shown below, the current flowing through the diode is in turn proportional to the voltage across the diode. Diodes behave like a one-way valve for current. When the voltage on the Anode is more positive than the voltage on the Cathode, then the diode is said to be in Forward Bias. As the voltage across the diode increases, the current through the diode increases dramatically. The heat generated by this current can easily destroy the device. It is therefore wise to install a current-limiting resistor in series with the diode to prevent thermal runaway. When the voltage on the Cathode is more positive than the voltage on the Anode, the diode is said to be in Reverse Bias. -

Three-Dimensional Integrated Circuit Design: EDA, Design And

Integrated Circuits and Systems Series Editor Anantha Chandrakasan, Massachusetts Institute of Technology Cambridge, Massachusetts For other titles published in this series, go to http://www.springer.com/series/7236 Yuan Xie · Jason Cong · Sachin Sapatnekar Editors Three-Dimensional Integrated Circuit Design EDA, Design and Microarchitectures 123 Editors Yuan Xie Jason Cong Department of Computer Science and Department of Computer Science Engineering University of California, Los Angeles Pennsylvania State University [email protected] [email protected] Sachin Sapatnekar Department of Electrical and Computer Engineering University of Minnesota [email protected] ISBN 978-1-4419-0783-7 e-ISBN 978-1-4419-0784-4 DOI 10.1007/978-1-4419-0784-4 Springer New York Dordrecht Heidelberg London Library of Congress Control Number: 2009939282 © Springer Science+Business Media, LLC 2010 All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden. The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights. Printed on acid-free paper Springer is part of Springer Science+Business Media (www.springer.com) Foreword We live in a time of great change. -

State-Of-The-Art and Future of Silicon on Insulator Technologies, Materials, and Devices Sorin Cristoloveanu *

Microelectronics Reliability 40 (2000) 771±777 www.elsevier.com/locate/microrel State-of-the-art and future of silicon on insulator technologies, materials, and devices Sorin Cristoloveanu * Laboratoire de Physique des Composants a Semiconducteurs (UA±CNRS & INPG), ENSERG, B.P. 257, 38016 Grenoble Cedex 1, France Abstract The context of SOI technologies is brie¯y presented in terms of wafer fabrication, con®guration/performance of typical SOI devices, and operation mechanisms in partially and fully depleted MOSFETs. The future of SOI is ten- tatively explored, by discussing the further scalability of SOI transistors as well as the innovating architectures proposed for the ultimate generations of SOI transistors. Ó 2000 Elsevier Science Ltd. All rights reserved. 1. Introduction 2. Synthesis of SOI wafers Silicon on insulator (SOI) technology, originally de- In the last 20 years, a variety of SOI structures have veloped for the niche of radiation-hard circuits, has ex- been conceived with the aim of separating, using a perienced three decades of continuous improvement in buried oxide (BOX), the active device volume from the material quality, device physics, and processing. Re- Si substrate. cently, SOI has joined the microelectronics roadmap: Silicon-on-sapphire (SOS, Fig. 1a1) is fabricated by SOI circuits are indeed attractive because of their epitaxial growth of a Si ®lm on Al2O3. The electrical enhanced performance (higher speed, lower power- properties may suer from lateral stress, in-depth inho- voltage) and scalability. mogeneity of the ®lm, and defective transition layer at The aim of this article is to provide a synthetic view the interface [1,2]. -

Floating-Gate Transistor Photodetector

University of Nebraska - Lincoln DigitalCommons@University of Nebraska - Lincoln Mechanical & Materials Engineering Faculty Mechanical & Materials Engineering, Publications Department of 10-10-2017 Floating-Gate Transistor Photodetector Jinsong Huang University of Nebraska-Lincoln, [email protected] Yongbo Yuan Lincoln, NE Follow this and additional works at: https://digitalcommons.unl.edu/mechengfacpub Part of the Mechanics of Materials Commons, Nanoscience and Nanotechnology Commons, Other Engineering Science and Materials Commons, and the Other Mechanical Engineering Commons Huang, Jinsong and Yuan, Yongbo, "Floating-Gate Transistor Photodetector" (2017). Mechanical & Materials Engineering Faculty Publications. 393. https://digitalcommons.unl.edu/mechengfacpub/393 This Article is brought to you for free and open access by the Mechanical & Materials Engineering, Department of at DigitalCommons@University of Nebraska - Lincoln. It has been accepted for inclusion in Mechanical & Materials Engineering Faculty Publications by an authorized administrator of DigitalCommons@University of Nebraska - Lincoln. THULHUILUWUTTURUS009786857B2 (12 ) United States Patent ( 10 ) Patent No. : US 9 ,786 , 857 B2 Huang et al. ( 45 ) Date of Patent : Oct . 10 , 2017 ( 54 ) FLOATING -GATE TRANSISTOR ( 58 ) Field of Classification Search PHOTODETECTOR CPC .. .. .. HO1L 31/ 1136 ; HO1L 51/ 0052 ; HOLL 51/ 428 ; YO2E 10 / 549 (71 ) Applicant : NUtech Ventures, Lincoln , NE (US ) See application file for complete search history . ( 72 ) Inventors : Jinsong Huang , Lincoln , NE (US ) ; ( 56 ) References Cited Yongbo Yuan , Lincoln , NE (US ) U . S . PATENT DOCUMENTS ( 73 ) Assignee : NUtech Ventures, Lincoln , NE (US ) 2007/ 0063304 A1 * 3 / 2007 Matsumoto .. B82Y 10 / 00 257 /462 ( * ) Notice : Subject to any disclaimer, the term of this 2010 /0155707 A1* 6 /2010 Anthopoulos .. B82Y 10 /00 patent is extended or adjusted under 35 257 /40 U . -

Bipolar Junction Transistor As a Detector for Measuring in Diagnostic X-Ray Beams

2013 International Nuclear Atlantic Conference - INAC 2013 Recife, PE, Brazil, November 24-29, 2013 ASSOCIAÇÃO BRASILEIRA DE ENERGIA NUCLEAR - ABEN ISBN: 978-85-99141-05-2 BIPOLAR JUNCTION TRANSISTOR AS A DETECTOR FOR MEASURING IN DIAGNOSTIC X-RAY BEAMS Francisco A. Cavalcanti1,2, David S. Monte1,2, Aline N. Alves1,2, Fábio R. Barros2, Marcus A. P. Santos2, and Luiz A. P. Santos1,2 1 Departamento de Energia Nuclear Universidade Federal de Pernambuco Av. Prof. Luiz Freire, 1000 50740-540 Recife, PE [email protected] 2 Centro Regional de Ciências Nucleares do Nordeste (CRCN-NE / CNEN) Av. Prof. Luiz Freire, 1 50740-540 Recife, PE [email protected] ABSTRACT Photodiode and phototransistor are the most frequently used devices for measuring ionizing radiation in medical applications. The cited devices have the operating principle well known, however the bipolar junction transistor (BJT) is not a typical device used as a detector for measuring some physical quantities for diagnostic radiation. In fact, a photodiode, for example, has an area about 10 mm square and a BJT has an area which can be more than 10 thousands times smaller. The purpose of this paper is to bring a new technique to estimate some physical quantities or parameters in diagnostic radiation; for example, peak kilovoltage (kVp), deep dose measurements. The methodology for each type of evaluation depends on the energy range of the radiation and the physical quantity or parameter to be measured. Actually, some characteristics of the incident radiation under the device can be correlated with the readout signal, which is a function of the electrical currents in the electrodes of the BJT: Collector, Base and Emitter. -

Designing Photodiode Amplifier Circuits with Opa128

® DESIGNING PHOTODIODE AMPLIFIER CIRCUITS WITH OPA128 The OPA128 ultra-low bias current operational amplifier RS achieves its 75fA maximum bias current without compro- mise. Using standard design techniques, serious perfor- I R C mance trade-offs were required which sacrificed overall P J J amplifier performance in order to reach femtoamp (fA = 10–15 A) bias currents. IP = photocurrent RJ = shunt resistance of diode junction CJ = junction capacitance UNIQUE DESIGN MINIMIZES R = series resistance PERFORMANCE TRADE-OFFS S FIGURE 1. Photodiode Equivalent Circuit. Small-geometry FETs have low bias current, of course, but FET size reduction reduces transconductance and increases noise dramatically, placing a serious restriction on perfor- Responsivity ≈ 109V/W 5pF mance when low bias current is achieved simply by making Bandwidth: DC to ≈ 30Hz input FETs extremely small. Unfortunately, larger geom- Offset Voltage ≈ ±485µV etries suffer from high gate-to-substrate isolation diode leak- HP 109Ω age (which is the major contribution to BIFET® amplifier 5082-4204 input bias current). Replacing the reverse-biased gate-to-substrate isolation di- 2 6 OPA128LM ode structure of BlFETs with dielectric isolation removes 3 this large leakage current component which, together with a 8 noise-free cascode circuit, special FET geometry, and ad- 109Ω vanced wafer processing, allows far higher Difet ® perfor- mance compared to BIFETs. FIGURE 2. High-Sensitivity Photodiode Amplifier. HOW TO IMPROVE PHOTODIODE AMPLIFIER PERFORMANCE An important electro-optical application of FET op amps is √ for photodiode amplifiers. The unequaled performance of eOUT = 4k TBR the OPA128 is well-suited for very high sensitivity detector k: Boltzman’s constant = 1.38 x 10–23 J/K ° designs. -

Mos2 Based Photodetectors: a Review

sensors Review MoS2 Based Photodetectors: A Review Alberto Taffelli *, Sandra Dirè , Alberto Quaranta and Lucio Pancheri Department of Industrial Engineering, University of Trento, Via Sommarive 9, 38123 Trento, Italy; [email protected] (S.D.); [email protected] (A.Q.); [email protected] (L.P.) * Correspondence: [email protected] Abstract: Photodetectors based on transition metal dichalcogenides (TMDs) have been widely reported in the literature and molybdenum disulfide (MoS2) has been the most extensively explored for photodetection applications. The properties of MoS2, such as direct band gap transition in low dimensional structures, strong light–matter interaction and good carrier mobility, combined with the possibility of fabricating thin MoS2 films, have attracted interest for this material in the field of optoelectronics. In this work, MoS2-based photodetectors are reviewed in terms of their main performance metrics, namely responsivity, detectivity, response time and dark current. Although neat MoS2-based detectors already show remarkable characteristics in the visible spectral range, MoS2 can be advantageously coupled with other materials to further improve the detector performance Nanoparticles (NPs) and quantum dots (QDs) have been exploited in combination with MoS2 to boost the response of the devices in the near ultraviolet (NUV) and infrared (IR) spectral range. Moreover, heterostructures with different materials (e.g., other TMDs, Graphene) can speed up the response of the photodetectors through the creation of built-in electric fields and the faster transport of charge carriers. Finally, in order to enhance the stability of the devices, perovskites have been exploited both as passivation layers and as electron reservoirs. Keywords: MoS2; TMD; photodetector; heterostructure; thin film Citation: Taffelli, A.; Dirè, S.; Quaranta, A.; Pancheri, L. -

Organic Light-Emitting and Photodetector Devices for Flexible

REVIEW PAPER IEICE Electronics Express, Vol.14, No.20, 1–16 Organic light-emitting and photodetector devices for flexible optical link and sensor devices: Fundamentals and future prospects in printed optoelectronic devices for high-speed modulation Hirotake Kajiia) Graduate School of Engineering, Osaka University, 2–1 Yamada-oka, Suita, Osaka 565–0871, Japan a) [email protected] Abstract: This paper describes the application of organic photonic devices including organic light-emitting and photodetector devices to integrated photonic devices for the realization of flexible optical link and sensor devices. Fundamentals and future prospects in printed optoelectronic devices for high-speed modulation are discussed and reviewed. Keywords: organic light-emitting diodes, organic photodetectors, organic light-emitting transistor, high speed, printed electrodes, sensor Classification: Electron devices, circuits and modules References [1] M. A. Baldo, et al.: “Very high-efficiency green organic light emitting devices based on electro-phosphorescence,” Appl. Phys. Lett. 75 (1999) 4 (DOI: 10. 1063/1.124258). [2] H. Uoyama, et al.: “Highly efficient organic light-emitting diodes from delayed fluorescence,” Nature 492 (2012) 234 (DOI: 10.1038/nature11687). [3] Y. Ohmori, et al.: “Realization of polymeric optical integrated devices utilizing organic light emitting diodes and photo detectors fabricated on a polymeric waveguide,” IEEE J. Sel. Top. Quantum Electron. 10 (2004) 70 (DOI: 10.1109/ JSTQE.2004.824106). [4] H. Kajii, et al.: “Organic light-emitting diode fabricated on a polymer substrate for optical links,” Thin Solid Films 438–439 (2003) 334 (DOI: 10.1016/S0040- 6090(03)00753-3). [5] H. Kajii, et al.: “Transient properties of organic electroluminescent diode using 8-Hydroxyquinoline aluminum doped with rubrene as an electro-optical conversion device for polymeric integrated devices,” Jpn.