PHU97NQ03LT N-Channel Trenchmos Logic Level FET

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Oriented Conferences Four Solutions

Delivering Solutions and Technology to the World’s Design Engineering Community Four Solutions- Oriented Conferences • System-on-Chip Design Conference • IP World Forum • High-Performance System Design Conference • Wireless and Optical Broadband Design Conference Special Technology Focus Areas January 29 – February 1, 2001 • Internet and Information Exhibits: January 30–31, 2001 Appliance Design Santa Clara Convention Center • Embedded Design Santa Clara, California • RF, Optical, and Analog Design NEW! • IEC Executive Forum International Engineering Register by January 5 and Consortium save $100 – and be entered to win www.iec.org a Palm Pilot! Practical Design Solutions Practical design-engineering solutions presented by practicing engineers—The DesignCon reputation of excellence has been built largely by the practical nature of its sessions. Design engineers hand selected by our team of professionals provide you with the best electronic design and silicon-solutions information available in the industry. DesignCon provides attendees with DesignCon has an established reputation for the high design solutions from peers and professionals. quality of its papers and its expert-level speakers from Silicon Valley and around the world. Each year more than 100 industry pioneers bring to light the design-engineering solutions that are on the leading edge of technology. This elite group of design engineers presents unique case studies, technology innovations, practical techniques, design tips, and application overviews. Who Should Attend Any professionals who need to stay on top of current information regarding design-engineering theories, The most complete educational experience techniques, and application strategies should attend this in the industry conference. DesignCon attracts engineers and allied The four conference options of DesignCon 2001 provide a professionals from all levels and disciplines. -

BUK9609-55A N-Channel Trenchmos Logic Level FET

Important notice Dear Customer, On 7 February 2017 the former NXP Standard Product business became a new company with the tradename Nexperia. Nexperia is an industry leading supplier of Discrete, Logic and PowerMOS semiconductors with its focus on the automotive, industrial, computing, consumer and wearable application markets In data sheets and application notes which still contain NXP or Philips Semiconductors references, use the references to Nexperia, as shown below. Instead of http://www.nxp.com, http://www.philips.com/ or http://www.semiconductors.philips.com/, use http://www.nexperia.com Instead of [email protected] or [email protected], use [email protected] (email) Replace the copyright notice at the bottom of each page or elsewhere in the document, depending on the version, as shown below: - © NXP N.V. (year). All rights reserved or © Koninklijke Philips Electronics N.V. (year). All rights reserved Should be replaced with: - © Nexperia B.V. (year). All rights reserved. If you have any questions related to the data sheet, please contact our nearest sales office via e-mail or telephone (details via [email protected]). Thank you for your cooperation and understanding, Kind regards, Team Nexperia BUK9609-55A D2PAK N-channel TrenchMOS logic level FET Rev. 02 — 3 February 2011 Product data sheet 1. Product profile 1.1 General description Logic level N-channel enhancement mode Field-Effect Transistor (FET) in a plastic package using TrenchMOS technology. This product has been designed and qualified to the appropriate AEC standard for use in automotive critical applications. 1.2 Features and benefits AEC Q101 compliant Suitable for logic level gate drive Low conduction losses due to low sources on-state resistance Suitable for thermally demanding environments due to 175 °C rating 1.3 Applications 12 V and 24 V loads Motors, lamps and solenoids Automotive and general purpose power switching 1.4 Quick reference data Table 1. -

KE02 Sub-Family Data Sheet

NXP Semiconductors Document Number MKE02P64M40SF0 Data Sheet: Technical Data Rev. 6, 12/2019 MKE02P64M40SF0 KE02 Sub-Family Data Sheet Supports the following: MKE02Z16VLC4(R), MKE02Z32VLC4(R), MKE02Z64VLC4(R), MKE02Z16VLD4(R), MKE02Z32VLD4(R), MKE02Z64VLD4(R), MKE02Z32VLH4(R), MKE02Z64VLH4(R), MKE02Z32VQH4(R), MKE02Z64VQH4(R), MKE02Z16VFM4(R), MKE02Z32VFM4(R), and MKE02Z64VFM4(R) Key features • System peripherals – Power management module (PMC) with three power • Operating characteristics modes: Run, Wait, Stop – Voltage range: 2.7 to 5.5 V – Low-voltage detection (LVD) with reset or interrupt, – Flash write voltage range: 2.7 to 5.5 V selectable trip points – Temperature range (ambient): -40 to 105°C – Watchdog with independent clock source (WDOG) • Performance – Programmable cyclic redundancy check module – Up to 40 MHz Arm® Cortex-M0+ core and up to 20 (CRC) MHz bus clock – Serial wire debug interface (SWD) – Single cycle 32-bit x 32-bit multiplier – Bit manipulation engine (BME) – Single cycle I/O access port • Security and integrity modules • Memories and memory interfaces – 64-bit unique identification (ID) number per chip – Up to 64 KB flash • Human-machine interface – Up to 256 B EEPROM – Up to 57 general-purpose input/output (GPIO) – Up to 4 KB RAM – Two up to 8-bit keyboard interrupt modules (KBI) • Clocks – External interrupt (IRQ) – Oscillator (OSC) - supports 32.768 kHz crystal or 4 • Analog modules MHz to 20 MHz crystal or ceramic resonator; choice – One up to 16-channel 12-bit SAR ADC, operation in of low power or high gain oscillators Stop mode, optional hardware trigger (ADC) – Internal clock source (ICS) - internal FLL with – Two analog comparators containing a 6-bit DAC internal or external reference, 31.25 kHz pre- and programmable reference input (ACMP) trimmed internal reference for 32 MHz system clock (able to be trimmed for up to 40 MHz system clock) – Internal 1 kHz low-power oscillator (LPO) NXP reserves the right to change the production detail specifications as may be required to permit improvements in the design of its products. -

Important Notice Dear Customer, on 7 February 2017 The

Important notice Dear Customer, On 7 February 2017 the former NXP Standard Product business became a new company with the tradename Nexperia. Nexperia is an industry leading supplier of Discrete, Logic and PowerMOS semiconductors with its focus on the automotive, industrial, computing, consumer and wearable application markets In data sheets and application notes which still contain NXP or Philips Semiconductors references, use the references to Nexperia, as shown below. Instead of http://www.nxp.com, http://www.philips.com/ or http://www.semiconductors.philips.com/, use http://www.nexperia.com Instead of [email protected] or [email protected], use [email protected] (email) Replace the copyright notice at the bottom of each page or elsewhere in the document, depending on the version, as shown below: - © NXP N.V. (year). All rights reserved or © Koninklijke Philips Electronics N.V. (year). All rights reserved Should be replaced with: - © Nexperia B.V. (year). All rights reserved. If you have any questions related to the data sheet, please contact our nearest sales office via e-mail or telephone (details via [email protected]). Thank you for your cooperation and understanding, Kind regards, Team Nexperia PMN27XPE 20 V, single P-channel Trench MOSFET 20 September 2012 Product data sheet 1. Product profile 1.1 General description P-channel enhancement mode Field-Effect Transistor (FET) in a small SOT457 (SC-74) Surface-Mounted Device (SMD) plastic package using Trench MOSFET technology. 1.2 Features and benefits • Fast switching • Trench MOSFET technology • 2 kV ESD protection 1.3 Applications • Relay driver • High-speed line driver • High-side loadswitch • Switching circuits 1.4 Quick reference data Table 1. -

I.MX RT1160 Crossover Processors Data Sheet for Consumer Products

NXP Semiconductors Document Number:IMXRT1160CEC Data Sheet: Technical Data Rev. 0, 04/2021 MIMXRT1166DVM6A MIMXRT1165DVM6A i.MX RT1160 Crossover Processors Data Sheet for Consumer Products Package Information Plastic Package 289-pin MAPBGA, 14 x 14 mm, 0.8 mm pitch Ordering Information See Table 1 on page 6 1. i.MX RT1160 introduction . 1 1 i.MX RT1160 introduction 1.1. Features . 2 1.2. Ordering information . 6 The i.MX RT1160 is a new high-end processor of i.MX 1.3. Package marking information . 9 RT family, which features NXP’s advanced 2. Architectural overview . 10 2.1. Block diagram . 10 implementation of a high performance Arm 3. Modules list . 11 Cortex®-M7 core operating at speeds up to 600 MHz 3.1. Special signal considerations . 20 ® 3.2. Recommended connections for unused analog and a power efficient Cortex -M4 core up to 240 MHz. interfaces . 21 4. Electrical characteristics . 23 The i.MX RT1160 processor has 1 MB on-chip RAM in 4.1. Chip-level conditions . 23 total, including a 768 KB RAM which can be flexibly 4.2. System power and clocks . 32 configured as TCM (512 KB RAM shared with M7 TCM 4.3. I/O parameters . 42 4.4. System modules . 50 and 256 KB RAM shared with M4 TCM) or 4.5. External memory interface . 54 general-purpose on-chip RAM. The i.MX RT1160 4.6. Display and graphics . 64 4.7. Audio . 70 integrates advanced power management module with 4.8. Analog . 72 DCDC and LDO regulators that reduce complexity of 4.9. -

6800/68000 Cmos

Click Here to Request a Large Quantity Quote 6800/68000 CMOS Jameco Manufacturer Manufacturer Description Package Product Type Organization Family Application Price 1 Part # Part # 130366 Major Brands 00130366 420 PIECE DIODE REFILL PACKAGE $29.95 130374 Major Brands 00130374 560 Piece Transistor Kit Refill Package $54.95 130391 Major Brands 00130391 420 Piece 74LS Logic Series Refill Package $214.95 130403 Major Brands 00130403 300 PIECE CD4000 SERIES REFILL PACKAGE $74.95 130411 Major Brands 00130411 480 PIECE LINEAR SERIES REFILL PACKAGE $164.95 1542961 Vishay 1.5KE16CA TVS Diode 22.5V Clamp 66.7A Ipp Through Hole 1500W DO-201 $0.49 1.5KE 2303247 Major Brands 1.5KE8.2C TVS Diode 12.1V Clamp 125.6A Ipp DO-201 DO-201 $0.59 35924 Major Brands 1N1188 Diode 1N1188 400 VOLT 35 AMP SILICON RECTIFIER DO-5 Stud Rectifier $3.95 2197610 Kest Parts 1N1190A Diode 1N1190A Power Silicon Rectifier 40 Amp 600V DO-5 DO-5 Stud Rectifier $4.95 2197628 Kest Parts 1N1190RA Diode 1N1190RA 40A 600V Power Silicon Rectifier DO-5 Stud Rectifier $4.95 2287679 Major Brands 1N1202A 200V 12A Rectifier Stud Mount DO-203 DO-203 Stud Rectifier $1.95 35941 Major Brands 1N270 Diode 1N270 Germanium 1 Volt @ 200Ma DO-7 General $1.19 Purpose 2220533 Major Brands 1N34A Diode 1N34A General Purpose Germanium DO-7 General $1.95 Purpose 35975 Major Brands 1N4001 Diode 1N4001 50 Volt 1 Amp General Purpose Rectifier DO-41 Standard $0.09 76961 Major Brands 1N4002 Diode 1N4002 100 Volt 1A DO-41 package DO-41 Standard $0.09 76970 Major Brands 1N4003 Diode 1N4003 Rectifier 200 Volt -

152F580552eb358625881dd680

Products Catalog Index PART NO. MANUFACTURER DESCRIPTION URL PRICE Q65112A2615 OSRAM OPTO Q65112A2615 http://www.searchdatasheet.com/Q65112A2615-datasheet.html QUOTE SEMICONDUCTORS XR33053ID-F EXAR Transceiver 1Mbps 3.3V/5V http://www.searchdatasheet.com/XR33053ID-F-datasheet.html QUOTE 14-Pin SOIC N Tube Q65111A7362 OSRAM OPTO LED Uni-Color White 2-Pin http://www.searchdatasheet.com/Q65111A7362-datasheet.html QUOTE SEMICONDUCTORS SMD T/R EL-17-21UYC/S530-A2/TR8 EVERLIGHT EL-17-21UYC/S530-A2/TR8 http://www.searchdatasheet.com/EL-17-21UYC%2FS530-A2%2FTR8-datasheet.html QUOTE ELECTRONICS Q65112A2616 OSRAM OPTO Q65112A2616 http://www.searchdatasheet.com/Q65112A2616-datasheet.html QUOTE SEMICONDUCTORS Q65111A9950 OSRAM OPTO Q65111A9950 http://www.searchdatasheet.com/Q65111A9950-datasheet.html QUOTE SEMICONDUCTORS Q65112A2629 OSRAM OPTO Q65112A2629 http://www.searchdatasheet.com/Q65112A2629-datasheet.html QUOTE SEMICONDUCTORS Q65112A0819 OSRAM OPTO LED Uni-Color White 2-Pin http://www.searchdatasheet.com/Q65112A0819-datasheet.html QUOTE SEMICONDUCTORS CSMD EP Q65111A9208 OSRAM OPTO Q65111A9208 http://www.searchdatasheet.com/Q65111A9208-datasheet.html QUOTE SEMICONDUCTORS Q65111A8966 OSRAM OPTO Q65111A8966 http://www.searchdatasheet.com/Q65111A8966-datasheet.html QUOTE SEMICONDUCTORS RLR20C1201GMRE6 VISHAY Res Metal Film 1.2K Ohm http://www.searchdatasheet.com/RLR20C1201GMRE6-datasheet.html QUOTE 2% 0.5W(1/2W) ±100ppm/C 1% Epoxy AXL T/R EVMB Connect One Evaluation Master Kit with http://www.searchdatasheet.com/EVMB-datasheet.html QUOTE Semiconductors -

AN5079, Qoriq P1 Series to T1 Series Migration Guide

NXP Semiconductors Document Number: AN5079 Application Note Rev. 0, 07/2017 QorIQ P1 Series to T1 Series Migration Guide Contents 1 About this document 1 About this document............................................... 1 This document provides a summary of the significant 2 Introduction.............................. .............................. 1 differences between QorIQ P1 series and T1 series devices. 3 Feature-set comparison................... ........................2 The QorIQ P1 series devices discussed in this document are P1010, P1020, and P1022. These are compared with QorIQ T1 4 PowerPC e500v2 vs e5500 core..............................4 series devices including T1024, T1014, T1023, T1013, T1040, 5 Ethernet controller...................................................8 T1020, T1042, and T1022. Use this document as a recommended resource for migrating products from P1 series 6 POR sequence....................................................... 14 to T1 series devices. 7 DDR memory controller................ .......................17 8 Local bus - eLBC vs IFC...................................... 18 9 USB.......................................................................20 2 Introduction 10 eSDHC...................................................................21 QorIQ P1 series devices combine single or dual e500v2 Power 11 Related documentation..........................................22 Architecture® core offering excellent combinations of 12 Revision history.................................................... 22 protocol -

Case M.8125 - JAC / NEXPERIA

EUROPEAN COMMISSION DG Competition Case M.8125 - JAC / NEXPERIA Only the English text is available and authentic. REGULATION (EC) No 139/2004 MERGER PROCEDURE Article 6(1)(b) NON-OPPOSITION Date: 12/10/2016 In electronic form on the EUR-Lex website under document number 32016M8125 EUROPEAN COMMISSION Brussels, 12.10.2016 C(2016) 6677 final PUBLIC VERSION SIMPLIFIED MERGER PROCEDURE To the notifying parties Dear Sirs, Subject: Case M.8125 - JAC / NEXPERIA Commission decision pursuant to Article 6(1)(b) of Council Regulation (EC) No 139/20041 and Article 57 of the Agreement on the European Economic Area2 1. On 13 September 2016, the European Commission received notification of a proposed concentration pursuant to Article 4 of the Merger Regulation by which the undertaking Beijing Jianguang Asset Management Co., Ltd. ("JAC", People's Republic of China), controlled by the China Investment Corporation (“CIC”, People's Republic of China), acquires within the meaning of Article 3(1)(b) of the Merger Regulation control of the standard products business unit (“Nexperia”) of NXP Semiconductors NV (“NXP”, the Netherlands) by way of purchase of shares.3 2. The business activities of the undertakings concerned are: − JAC is an investment management company which focuses its investments on mergers and acquisitions in the semiconductor industry. It is active in developing, manufacturing, and selling RF power transistors and bipolar based (power) diodes, thyristors and transistors. Its parent company, CIC, is a sovereign wealth fund of the People’s Republic of China, specialized in foreign exchange holdings. − Nexperia is active in the manufacturing and sale of semiconductors, in particular several types of logic integrated circuits ("ICs"), small signal transistors and diodes. -

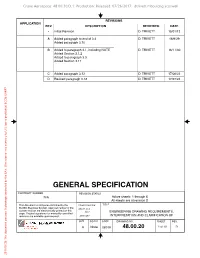

General Specification

Crane Aerospace: 48.00.20,D,1: Production: Released: 07/26/2017: dtrivett mboulang scaswell REVISIONS APPLICATION REV DESCRIPTION REVIEWED DATE - Initial Revision D. TRIVETT 15/01/12 A Added paragraph to end of 3.4 D. TRIVETT 16/9/29 Added paragraph 3.10 B Added to paragraph 3.1, including NOTE D. TRIVETT 16/11/30 Added Section 3.1.2 Added to paragraph 3.3 Added Section 3.11 C Added paragraph 3.12 D. TRIVETT 17/06/22 D Revised paragragh 3.12 D. TRIVETT 17/07/24 GENERAL SPECIFICATION CONTRACT NUMBER REVISION STATUS N/A Active sheets: 1 through 6 All sheets are at revision D This document is computer-controlled by the TOLERANCES ARE: TITLE ELDEC Business System. Approval names for the LINEAR .XX = current revision are electronically printed on this .XXX = ENGINEERING DRAWING REQUIREMENTS, page. Original signatures for manually-controlled revisions are available upon request. ANGULAR = INTERPRETATION AND CLARIFICATION OF SIZE SCALE CAGE DRAWING NO. SHEET REV. A None 08748 48.00.20 1 of 10 D 2017/07/26 This document contains Technology controlled by the EAR. Diversion or use contrary to U.S. law is prohibited. ECCN: EAR99 Crane Aerospace: 48.00.20,D,1: Production: Released: 07/26/2017: dtrivett mboulang scaswell 1 SCOPE This specification establishes general and specific guidelines to aid in the interpretation and application of engineering drawings defining components, materials, or assemblies, whether purchased from suppliers or fabricated at Crane Aerospace & Electronics facilities. 1.1 Applicability This document applies to engineering drawings controlled by the Lynnwood site of Crane Aerospace & Electronics (CRANE), also referred to as ELDEC Corporation. -

Nexperia USA Inc

N74F14D,623 Details PDF N74F14D,623 Part Number: N74F14D,623 Manufacturer: Nexperia USA Inc. Description: IC HEX INVERTER SCHM TRIG 14SOIC Lead Free Status / Lead free / RoHS Compliant RoHS Status: Data sheet: N74F14D,623.pdf INQUIRY Introduction Images are for reference only. See Product Specifications for product details. If you are interested to buy Nexperia N74F14D,623,Just Email us. [email protected] our sales team will reply you within 24 hours Specifications Voltage - Supply: 4.5 V ~ 5.5 V Supplier Device Package: 14-SO Series: 74F Packaging: Original-Reel® Package / Case: 14-SOIC (0.154", 3.90mm Width) Operating Temperature: 0°C ~ 70°C Number of Inputs: 6 Number of Circuits: 6 Mounting Type: Surface Mount Max Propagation Delay @ V, Max CL: 8.5ns @ 5V, 50pF Logic Type: Inverter Logic Level - Low: 0.8V Logic Level - High: 2V Features: Schmitt Trigger Current - Quiescent (Max): - Current - Output High, Low: 1mA, 20mA Email: [email protected] RELATED PARTS FOR N74F14D,623 Image Part Number Manufacturers Description View N74F14D,602 NXP USA Inc. IC HEX INVERTER/SCHM TRIG 14SOIC Inquiry N74F138D,602 NXP USA Inc. IC DECODER/DEMUX 3-8LINE 16SOIC Inquiry N74F157AD,623 NXP USA Inc. IC DATA SELECTOR/MUX 2IN 16SOIC Inquiry N74F154D PHILIPS Inquiry N74F153D,602 NXP USA Inc. IC MULTIPLEXER DUAL 4IN 16SOIC Inquiry N74F138N,602 NXP USA Inc. IC DECODER/DEMUX 3-8LINE 16DIP Inquiry N74F153N,602 NXP USA Inc. IC MULTIPLEXER DUAL 4IN 16DIP Inquiry N74F139N PHI Inquiry N74F153D SIGNETICS Inquiry N74F14D NXP in stock Inquiry N74F157AN,602 NXP USA Inc. IC DATA SELECTOR/MUX 2IN 16-DIP Inquiry N74F139N,602 NXP USA Inc. -

Nexperia Pnx8500

Home Entertainment Engine Nexperia pnx8500 Designed for use in mid- to high-end advanced set-top box (ASTB) and digital television (DTV) systems, the Nexperia™ pnx8500 Home Entertainment Engine deliv- ers comprehesive source decoder, interactive TV, Inter- net, telephony, and digital recording functions on a single chip.This highly flexible IC decodes all high-definition (HD) and standard-definition (SD) MPEG-2 source material. Outputting enhanced SD display, the pnx8500 is primarily targeted for STBs driving existing NTSC, PAL, and SECAM television sets as well as digital TVs and projectors. On a single, flexible IC, the pnx8500 provides a com- plete, future-proof solution for building tomorrow's advanced STB products. In addition to supporting basic and premium TV services, pnx8500-powered STBs can be easily enhanced to deliver advanced TV services such FEATURES as web-browsing, time-shift record/playback, interactive + Dual-CPU design includes a 200-MHz TriMedia VLIW core and video, streaming video and audio media, video telepho- a 150-MHz MIPS 3940 core ny, games, purchase transaction management, and more. + Demultiplexes, descrambles and PID filters multiple DVB or New standards for DTV, communications, or multime- DSS transport streams dia can be supported through software upgrades. + Supports input of two digital video streams (CCIR656, broad- FLEXIBLE, DUAL-CPU ARCHITECTURE cast quality) The pnx8500 dual-CPU architecture combines powerful + Simultaneous MPEG-2 decoding of three SD streams or one MIPS (R3940) and TriMedia (TM32) VLIW processor HD (MP@HL) stream cores that control a range of on-chip hardware components + DVB, MULTI2 and DSS descrambling, and ICAM verification through three system buses.