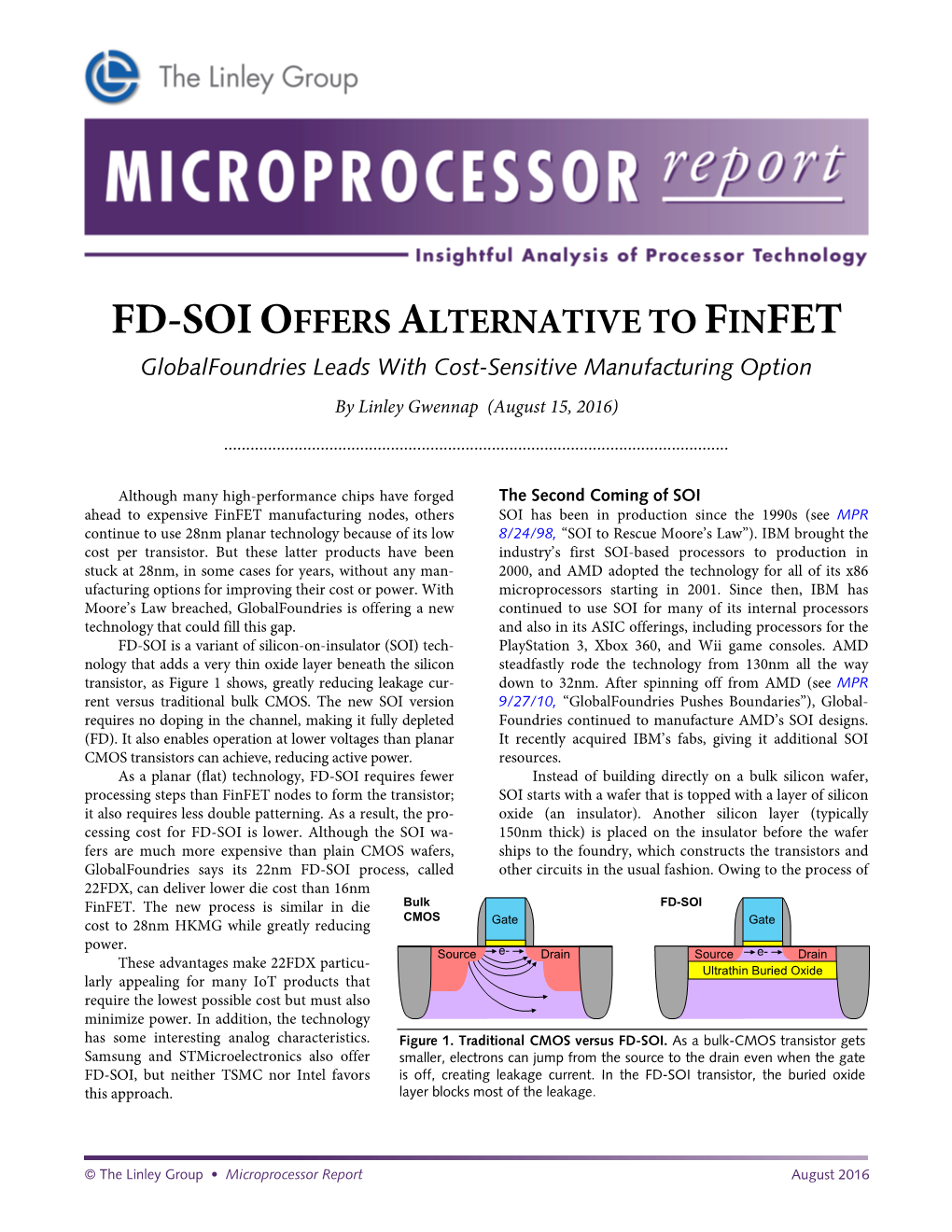

FD-SOI OFFERS ALTERNATIVE to FINFET Globalfoundries Leads with Cost-Sensitive Manufacturing Option

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Fabrication of Group IV Semiconductors on Insulator for Monolithic 3D Integration

Fabrication of Group IV Semiconductors on Insulator for Monolithic 3D Integration Ali Asadollahi Doctoral Thesis in Information and Communication Technology School of Electrical Engineering and Computer Science KTH Royal Institute of Technology Stockholm, Sweden 2017 KTH School of Electrical Engineering and Computer TRITA-EECS-AVL-2018:1 Science ISBN: 978-91-7729-658-4 SE-164 40 Stockholm SWEDEN Akademisk avhandling som med tillstånd av Kungliga Tekniska högskolan framlägges till offentlig granskning för avläggande av teknologie doktorsexamen fredagen den 16 februari 2018 klockan 10:00 i Ka-Sal C (Sal Sven-Olof Öhrvik), Electrum, Kungliga Tekniska högskolan, Kistagången 16, Kista. ©Ali Asadollahi, December 2017 Tryck: Universitetsservice US-AB, Stockholm, 2017 ii To My Parents “All the different nations in the world, despite their differences of appearance and language and the way of life, still have one thing in common, and that is what's inside in all of us. If we X-rayed the insides of different human beings, we wouldn't be able to tell from those X-rays what the person's language or background or race is.” Abbas Kiarostami iv Abstract The conventional 2D geometrical scaling of transistors is now facing many challenges in order to continue the performance enhancement while decreasing power consumption. The decrease in the device power consumption is related to the scaling of the power supply voltage (Vdd) and interconnects wiring length. In addition, monolithic three dimensional (M3D) integration in the form of vertically stacked devices, is a possible solution to increase the device density and reduce interconnect wiring length. Integrating strained germanium on insulator (sGeOI) pMOSFETs monolithically with strained silicon/silicon-germanium on insulator (sSOI/sSiGeOI) nMOSFETs can increase the device performance and packing density. -

Advanced Packaging Solutions

Advanced Packaging Solutions Highlights Providing silicon-scaling • Advanced packaging capabilities in solutions for tomorrow’s applications 2.5D, 3D, WLP and Silicon Photonics GLOBALFOUNDRIES post-fab services provide complementary and extended • Power, performance, cost and solutions with complete supply chain management including bump, probe, form-factor optimized solutions packaging and final test. The flexible supply chain model is tailored to your • Industry leader in smart interposers needs with services ranging from bump and probe only to a more comprehen- sive spectrum of services including package design, assembly and test. • In-house bump and wafer probe capabilities In addition to in-house bump and probe capabilities, we provide packaging • Advanced memory integration services in collaboration with a network of established OSAT partners, includ- with stacked memories ing 2D packages as well as 2.5D and 3D advanced package technologies. Test development and capabilities include RF, analog, embedded memory, • Ownership and process maturity for HVM and mmWave applications, with wide array of tester platforms for wafer sort operations. • Advanced silicon node CPI and qualification Packaging Requirements • RF system-in-package and Package types are selected based on performance requirements and optimized mmWave packaging capability for market segments including IoT, RF, Automotive, Mobile, High-end • Partnerships and strong relationships Computing, Networking and Storage. with leading-edge OSATs • Flexible supply chain and Mobile IoT RF Automotive Computing Networking Storage collaborative business models QFN FBGA WLCSP FOWLP SiP fcCSP FCBGA 2.5D 3D Si-PH Advanced Packaging Solutions Packaging Technologies TSV Si Interposer Availability GF Si nodes are qualified in a wide range of package Full Reticle 26x33mm2 technologies including 2D wirebond designs, flip Stitched Interposer >1300 mm2 chip, WLCSP and FOWLP configurations, as well 10:1 Aspect Ratio TSV 10um Dia./ 100um Depth as 2.5D, 3D and Si-Photonics. -

Three-Dimensional Integrated Circuit Design: EDA, Design And

Integrated Circuits and Systems Series Editor Anantha Chandrakasan, Massachusetts Institute of Technology Cambridge, Massachusetts For other titles published in this series, go to http://www.springer.com/series/7236 Yuan Xie · Jason Cong · Sachin Sapatnekar Editors Three-Dimensional Integrated Circuit Design EDA, Design and Microarchitectures 123 Editors Yuan Xie Jason Cong Department of Computer Science and Department of Computer Science Engineering University of California, Los Angeles Pennsylvania State University [email protected] [email protected] Sachin Sapatnekar Department of Electrical and Computer Engineering University of Minnesota [email protected] ISBN 978-1-4419-0783-7 e-ISBN 978-1-4419-0784-4 DOI 10.1007/978-1-4419-0784-4 Springer New York Dordrecht Heidelberg London Library of Congress Control Number: 2009939282 © Springer Science+Business Media, LLC 2010 All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden. The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights. Printed on acid-free paper Springer is part of Springer Science+Business Media (www.springer.com) Foreword We live in a time of great change. -

H1 2015-2016 Results

H1 2015-2016 Results November 2015 Safe Harbour Statement This presentation contains forward-looking statements made pursuant to the safe harbour provisions of the Private Securities litigation reform Act of 1995. By nature, forward looking statement represent the judgment regarding future events and are based on currently available information. Although the Company cannot guarantee their accuracy, actual results may differ materially from those the company anticipated due to a number of uncertainties, many of which the Company is not aware. For additional information concerning these and other important factors that may cause the Company’s actual results to differ materially from expectations and underlying assumptions, please refer to the reports filed by the Company with the Autorité des Marchés Financiers (AMF). Soitec – H1 2015-2016 Results – November 2015 2 Agenda 1 Highlights 2 H1 2015-2016 Financial results 3 Outlook 4 Q&A Appendix: Electronics core business Soitec – H1 2015-2016 Results – November 2015 3 H1 2015-2016 - Core Business highlights Communication and Power – Demand remains robust for RF-SOI products in mobile applications; SOI content continues to grow within smartphones due to increased complexity (number of bands and performance) – Bernin 200mm-diameter wafer capacity is almost sold out for CY 2016 – Simgui (Chinese foundry) produced its first 200mm wafers in October 2015 and is now starting customers qualifications – Customers developing successfully 300mm wafers for RF - at least one major fabless and one foundry -

Multiprocessing Contents

Multiprocessing Contents 1 Multiprocessing 1 1.1 Pre-history .............................................. 1 1.2 Key topics ............................................... 1 1.2.1 Processor symmetry ...................................... 1 1.2.2 Instruction and data streams ................................. 1 1.2.3 Processor coupling ...................................... 2 1.2.4 Multiprocessor Communication Architecture ......................... 2 1.3 Flynn’s taxonomy ........................................... 2 1.3.1 SISD multiprocessing ..................................... 2 1.3.2 SIMD multiprocessing .................................... 2 1.3.3 MISD multiprocessing .................................... 3 1.3.4 MIMD multiprocessing .................................... 3 1.4 See also ................................................ 3 1.5 References ............................................... 3 2 Computer multitasking 5 2.1 Multiprogramming .......................................... 5 2.2 Cooperative multitasking ....................................... 6 2.3 Preemptive multitasking ....................................... 6 2.4 Real time ............................................... 7 2.5 Multithreading ............................................ 7 2.6 Memory protection .......................................... 7 2.7 Memory swapping .......................................... 7 2.8 Programming ............................................. 7 2.9 See also ................................................ 8 2.10 References ............................................. -

State-Of-The-Art and Future of Silicon on Insulator Technologies, Materials, and Devices Sorin Cristoloveanu *

Microelectronics Reliability 40 (2000) 771±777 www.elsevier.com/locate/microrel State-of-the-art and future of silicon on insulator technologies, materials, and devices Sorin Cristoloveanu * Laboratoire de Physique des Composants a Semiconducteurs (UA±CNRS & INPG), ENSERG, B.P. 257, 38016 Grenoble Cedex 1, France Abstract The context of SOI technologies is brie¯y presented in terms of wafer fabrication, con®guration/performance of typical SOI devices, and operation mechanisms in partially and fully depleted MOSFETs. The future of SOI is ten- tatively explored, by discussing the further scalability of SOI transistors as well as the innovating architectures proposed for the ultimate generations of SOI transistors. Ó 2000 Elsevier Science Ltd. All rights reserved. 1. Introduction 2. Synthesis of SOI wafers Silicon on insulator (SOI) technology, originally de- In the last 20 years, a variety of SOI structures have veloped for the niche of radiation-hard circuits, has ex- been conceived with the aim of separating, using a perienced three decades of continuous improvement in buried oxide (BOX), the active device volume from the material quality, device physics, and processing. Re- Si substrate. cently, SOI has joined the microelectronics roadmap: Silicon-on-sapphire (SOS, Fig. 1a1) is fabricated by SOI circuits are indeed attractive because of their epitaxial growth of a Si ®lm on Al2O3. The electrical enhanced performance (higher speed, lower power- properties may suer from lateral stress, in-depth inho- voltage) and scalability. mogeneity of the ®lm, and defective transition layer at The aim of this article is to provide a synthetic view the interface [1,2]. -

HEP Computing Trends

HEP Computing Trends Andrew Washbrook University of Edinburgh ATLAS Software & Computing Tutorials 19th January 2015 UTFSM, Chile Introduction • I will cover future computing trends for High Energy Physics with a leaning towards the ATLAS experiment • Some examples of non-LHC experiments where appropriate • This is a broad subject area (distributed computing, storage, I/O) so here I will focus on the readiness of HEP experiments to changing trends in computing architectures • Also some shameless promotion of work I have been involved in.. Many thanks to all the people providing me with material for this talk! LHC Context Run 2 • Increase in centre of mass energy 13TeV • Increase in pile up from ~20 to ~50 • Increase in Trigger rate up to 1 KHz RAW to ESD • More computing resources required to Reconstruction reconstruct events Time High Luminosity LHC • HL-LHC starts after LS3 (~2022) • Aim to provide 300[-1 per year • Pileup of 150 expected • 200 PB/year of extra storage HL-LHC Timeline CPU Evolution • Die shrink getting smaller • Research down to 5nm depending on lithography and materials • Clock speed improvement has slowed • More cores per socket • Server at the Grid computing centre has at least 16 cores, typically more • Extrapolation from 2013 predicts 25% server performance improvement per year Processor scaling trends 1e+06 Transistors ● Clock Power ● Performance ● Performance/W ● ● ● ● ● ● ●●● ● ● ● ●●● ● ● ●●● ●● ●●●●● ● ● ●●●●● ●●●●●●●●● ●●●● ● ● ●●●● ●●●●●●●● ●●●●●● ● ●● ● ● ●● ● ●●●● ●●●●●●●●●●●● ● ● ● ●● ●●●● ●●●●●●●●●●●●●●●●● -

Spring 2017 Industry Study Industry Report Electronics

Spring 2017 Industry Study Industry Report Electronics The Dwight D. Eisenhower School for National Security and Resource Strategy National Defense University Fort McNair, Washington, DC 20319-5062 i ELECTRONICS 2017 ABSTRACT: While currently assessed as mature and healthy, the global semiconductor industry is facing a strategic inflection point. This inflection will shape a future for the industry that is significantly different than the past. Although outlook for that future remains favorable, numerous challenges place that future at risk. Challenges found in Chinese competition, skilled workforce shortages, commercial semiconductor market shifts, unique DoD electronics needs, and ongoing requirements for rapid innovation threaten the stability of the market, the U.S. competitive advantage, and U.S. economic and national security. Future success in the industry hinges upon policies which address these challenges and enable U.S. companies to embrace future opportunities. LTC Khalid Alothman, Saudi Arabian Army CDR Terri L. Gabriel, U.S. Navy LTC Kevin F. Hanrahan, U.S. Army COL Jeffrey Howell, U.S. Army Mr. Benjamin Lam, U.S. Dept. of State Mr. Steven Mapes, Office of the Secretary of Defense Lt Col Adrian Meyer, Air National Guard COL Michael Samson, Philippine Army Col James E. Smith, U.S. Air Force Mr. Keith Smithson, Dept. of Energy COL William Smoot, U.S. Army Mr. Sim Walker, Dept. of the Army Lt Col Aaron Weiner, U.S. Air Force Ms. Denise L. Williams, Office of the Secretary of Defense Dr. Stephen Basile, Faculty Mr. Michael Dixon, Department of State, Faculty Col Thomas A. Santoro, Jr., U.S. Air Force, Faculty ii Industry Study Outreach and Field Studies On Campus Presenters BAE Systems, Inc., Arlington, VA Bureau of East Asian and Pacific Affairs, U.S. -

Heading Towards Big Data Building a Better Data Warehouse for More Data, More Speed, and More Users

Heading Towards Big Data Building A Better Data Warehouse For More Data, More Speed, And More Users Raymond Gardiner Goss [email protected] Kousikan Veeramuthu [email protected] Manufacturing Technology GLOBALFOUNDRIES Malta, NY, USA Abstract—As a new company, GLOBALFOUNDRIES is determine the caller’s income level and specify to which agent aggressively agile and looking at ways to not just mimic existing to route the call or the switch would timeout. When switches semiconductor manufacturing data management but to leverage were overwhelmed with data, they would drop packets and new technologies and advances in data management without algorithms had to infer states based on most probable current sacrificing performance or scalability. Being a global technology state. Other industries, such as social media, are challenged company that relies on the understanding of data, it is important to centralize the visibility and control of this information, bringing more by unstructured data and need tools to help turn text it to the engineers and customers as they need it. messages and photos into useful information for search engines and marketing purposes. The challenge in the semiconductor Currently, the factories are employing the best practices and world is with the size of the data. Speed becomes a secondary data architectures combined with business intelligence analysis problem because so many sources are needed to be joined and reporting tools. However, the expected growth in data over together in a timely manner. Large recipes, complex output the next several years and the need to deliver more complex data integration for analysis will easily stress the traditional tools from the test floor combined now with more Interface-A trace beyond the limits of the traditional data infrastructure. -

SPECIAL REPORT SOI Wafer Technology for CMOS Ics

SPECIAL REPORT SOI Wafer Technology for CMOS ICs Robert Simonton President, Simonton Associates Introduction: SOI (Silicon On Insulator) wafers have been used commercially as starting substrates for several decades in selected discrete and integrated circuit (IC) semiconductor device applications, particularly for use in extreme operating environments for military and space applications. The first SOI devices were developed for early satellite and space exploration systems in the 1960s. The key advantage of SOI wafers in these traditional applications was their resistance to ionization by radiation (e.g., solar wind radiation in space) and the robust voltage isolation of the IC. Most of the early SOI devices were fabricated with SOS (Silicon-On-Sapphire) wafers. The unique feature of today’s SOI wafers is that they have a buried silicon oxide (Buried OXide, or BOX) layer extending across the entire wafer, just below a surface layer of device-quality single-crystal silicon. The active elements (e.g., transistors in a CMOS IC) of semiconductor devices are fabricated in the single-crystal silicon surface layer over the BOX. The BOX layer provides robust vertical isolation from the substrate. Standard LOCOS (LOCal Oxidation of Silicon) or STI (Shallow Trench Isolation) processes are employed to provide lateral isolation from adjacent devices. At the present time, most SOI wafers are fabricated by use of one of two basic approaches. SOI wafers may be fabricated with the SIMOXTM (Separation by IMplanted OXygen) process, which employs high dose ion implantation of oxygen and high temperature annealing to form the BOX layer in a bulk wafer [1,2,3]. -

Boa Motion to Dismiss

Case 21-10036-CSS Doc 211-4 Filed 02/15/21 Page 425 of 891 Disposition of the Stapled Securities Gain on sale of Stapled Securities by a Non-U.S. Stapled Securityholder will not be subject to U.S. federal income taxation unless (i) the Non-U.S. Stapled Securityholder’s investment in the Stapled Securities is effectively connected with its conduct of a trade or business in the United States (and, if provided by an applicable income tax treaty, is attributable to a permanent establishment or fixed base the Non-U.S. Stapled Securityholder maintains in the United States) and a properly completed Form W-8ECI has not been provided, (ii) the Non-U.S. Stapled Securityholder is present in the United State for 183 days or more in the taxable year of the sale and other specified conditions are met, or (iii) the Non-U.S. Stapled Securityholder is subject to U.S. federal income tax pursuant to the provisions of the U.S. tax law applicable to U.S. expatriates. If gain on the sale of Stapled Securities would be subject to U.S. federal income taxation, the Stapled Securityholder would generally recognise any gain or loss equal to the difference between the amount realised and the Stapled Securityholder’s adjusted basis in its Stapled Securities that are sold or exchanged. This gain or loss would be capital gain or loss, and would be long-term capital gain or loss if the Stapled Securityholder’s holding period in its Stapled Securities exceeds one year. In addition, a corporate Non-U.S. -

22Nm Ultra-Thin Body and Buried Oxide FDSOI RF Noise Performance

RMo1B-5 22nm Ultra-Thin Body and Buried Oxide FDSOI RF Noise Performance Ousmane M. Kane#1, Luca Lucci$, Pascal Scheiblin$, Sylvie Lepilliet*, François Danneville* #CEA Leti, Lille University, France $CEA Leti, France *CNRS, Université Lille, ISEN, Université Valenciennes, UMR 8520 - IEMN, Lille, France [email protected] Abstract—The drastic downscaling of the transistor size along lower Cgg capacitance and a higher transconductance, resulting with advances in material sciences allowed the development of low from enhanced stress response [4]. Each NMOS device was power CMOS technologies with competitive RF figure of merits accompanied by a dedicated open and short structure for de- suitable for millimeter applications. In this context, this paper embedding at lower metal reference plane and all of these presents the RF and noise characterization (up to 110 GHz) of an transistors were characterized. But, a selected device, whose advanced 22 nm UTBB FDSOI technology developed by Globalfoundries. In addition to the excellent DC performance, the dimensions are reported in Table 1, was chosen for this paper. technology presents promising RF characteristics. Indeed, a Table 1. Device geometry maximum transconductance of 1.78 S/mm and a Fmax of 435 GHz are achieved. The technology also offers a state-of-the-art Gate length Unit gate finger Number of gate Total gate width minimum noise figure (NFmin) of 0.45 dB at 20 GHz (with an (Lg) [nm] width (Wf) [µm] fingers (Nf) (Wtot) [µm] associated Gain of 13 dB) for a drain current of 185 mA/mm. 18 0.3 192 57.60 Keywords— CMOS, FDSOI, noise measurement, millimeter wave.