82P2828 Datasheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

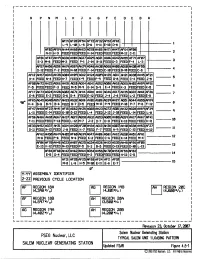

Salem Generating Station, Units 1 & 2, Revision 29 to Updated Final Safety Analysis Report, Chapter 4, Figures 4.5-1 to 4.5

r------------------------------------------- 1 I p M J B I R N L K H G F E D c A I I I I I Af'Jq AF20 AF54 AF72 32 AF52 AF18 I L-q L-10 L-15 D-6 -11 E-10 D-8 l I AF03 Af't;qAH44 AH60 AH63 AG70 AH65 AH7l AH47 AFS4 AF08 I N-ll H-3 FEED FEED FEED H-14 FEED FEED FEED M-12 C-11 2 I AF67 AH4q AH04 AG27 AG2<i' AG21 AG16 AG42 AF71 AF07 AF01 AG36 AH!5!5 3 I E-3 M-6 FEED M-3 FEED P-1 J-14 B-11 FEED D-3 FEED F-4 L-3 I AF67 AH5S AG56 Atflq AGsq AH2<1' AG48 AH30 AG68 AH08 AG60 AH30 AF55 I D-12 FEED F-2 FEED N-11 FEED F-14 FEED C-11 FEED B-11 FEED C-8 4 I AF12 AH57 AG43 AH38 AHtiJq AG12 AH24 AGfR AH25 AGil AG31 AH45 AF21 AGlM AH21 5 I H~4 FEED N-4 FEED H-7 FEED K~q FEED F-q FEED G-8 FEED C-4 FEED J-15 I AF50 AH72 AH22 AGS6 AH15 AGll.lAG64 AG41 AG52 AG88 AH18 AG65 AHIJ2 AH5q AF51 I F-5 FEED FEED F-3 FEED M-5 r+q G-14 o-q E-4 FEED K-3 FEED FEED K-5 6 I f:Fl7 AH73 AG24 AH28 AG82 AG71 AH14 AG18 AHil AG46 AG17 AH35 AG22 AH61 AF26 7 I E-8 FEED E-2 FEED G-6 G-4 FEED E-12 FEED J-4 J-6 FEED L-2 FEED E-5 I Af&q I qeo AF65 AG45 AtM0 AG57 AH33 AG32 AG16 AH01 AGI6 AG3<1' AH27 AG51 AG44 AG55 K-4 B-8 e-q B-6 FEED B-7 P-5 FEEC M-11 P-q FEED P-11 P-7 P-8 F-12 8 I AF47 AH68 AF23 AH41 AF1!5 AG62 AH26 AG03 AH23 AH32 AG28 AHsq AF3<1' q I L-U FEED E-14 FEED G-10 G-12 FEED L-4 FEED FEED L-14 FEED L-8 I ~~ AF66 AH66 AH10 AG67 AH37 AGJq AG68 AG3l AG63 AG05 AH08 AG5q AH17 AH67 AF41 I F-11 FEED FEED F-13 FEED L-12 M-7 J-2 D-7 D-11 FEED K-13 FEED FEED K-11 10 I AE33 AH!52 AG37 AH31 AG14 AH20 AF20 AH34 AG13 AH36 AG07 AH40 AG38 AH!53 AF27 I G-ll FEED N-12 FEED J-8 FEED K-7 FEED -

The Transport Trend of Thailand and Malaysia

Executive Summary Report The Potential Assessment and Readiness of Transport Infrastructure and Services in Thailand for ASEAN Economic Community (AEC) Content Page 1. Introduction 1.1 Rationales 1 1.2 Objectives of Study 1 1.3 Scopes of Study 2 1.4 Methodology of Study 4 2. Current Status of Thailand Transport System in Line with Transport Agreement of ASEAN Community 2.1 Master Plan and Agreement on Transport System in ASEAN 5 2.2 Major Transport Systems for ASEAN Economic Community 7 2.2.1 ASEAN Highway Network 7 2.2.2 Major Railway Network for ASEAN Economic Community 9 2.2.3 Main Land Border Passes for ASEAN Economic Community 10 2.2.4 Main Ports for ASEAN Economic Community 11 2.2.5 Main Airports for ASEAN Economic Community 12 2.3 Efficiency of Current Transport System for ASEAN Economic Community 12 3. Performance of Thailand Economy and Transport Trend after the Beginning of ASEAN Economic Community 3.1 Factors Affecting Cross-Border Trade and Transit 14 3.2 Economic Development for Production Base Thriving in Thailand 15 3.2.1 The analysis of International Economic and Trade of Thailand and ASEAN 15 3.2.2 Major Production Bases and Commodity Flow of Prospect Products 16 3.2.3 Selection of Potential Industries to be the Common Production Bases of Thailand 17 and ASEAN 3.2.4 Current Situation of Targeted Industries 18 3.2.5 Linkage of Targeted Industries at Border Areas, Important Production Bases, 19 and Inner Domestic Areas TransConsult Co., Ltd. King Mongkut’s University of Technology Thonburi 2T Consulting and Management Co., Ltd. -

Oneida County Legislative District 1 Date: April 1, 2014

CARTER RD D D 5 R R 6 B T 3 L L I E P L P S A T K E U C E T 5 C 6 K R D D U W O 3 M R W O D E O R S E R A K T R L Y T N C E E A A S E U D H G R I C Y T O I E O E D E R ID R A R A T R N N R F D C R D E W E O R N S E G S N D R H R E T D T E E S E A L D H S E E R I R T O S T U R I 10 D R M S N W I S R A G E A C N L H R T Y Verona D R AC11 AC12 AC13 AC14 AC15 E AC16 AC17 AC18 H AC19 R C R W H T L D R E I IL D L D D R L S E VERONA 4 R E B R M U N L R D I E T A K C K H A C O O U R S 6 R TA R N D TE 2 D R T OU R LO TE W E 31 Y EL T L U D R D R D O E R R L L B N R O E S T G E N T W E D I B A R L T O D S R NS E D T A D S A M M R R R T H 4 WESTMORELAND 3 R E C E N R RO A E N R E U FR TE N D U G Y T H B R 31 D D R S I I L D E R Y 5 YD R L R 6 L BO R D 5 L R N 3 I I 6 E SPR R H A 3 ING RD M M G E D S 3 R M E L I E T O E W N U T R EL I F U L I O RD E S L R O PR I-90 R D R ING STAT D E RD I- E R T E 90 OU T T A D AD11 AD12 AD13 E AD14 T A AD15 AD16 AD17 AD18 AD19 31 S T R S I-90 I-90 H 0 T I-9 L I OW D E R M S LL S PR VERONA 3 L ING H RD IL 0 OUS H I-90 I-9 E RD FOSTE D R CORN N ERS RD A T S S N D I R A E I-90 R M O Y I-90 O IL DA 5 M D D R 36 I-90 I-90 R E S A T -90 MIT G I C HEL S E U L R WN L R D O I O D T NE N R I D R I-90 I R RD S K SK KINNE R N 0 E N T RD -9 T 5 E I I E 0 L A 6 R L 9 S A J I- P 3 D D T T S R WESTMORELAND 4 D S E Y R E A LL R E W T N E C NL D T H O O E U H C L T F I R O R I L L M E O I R O L L X M W U D IL HIL E L T R R O M 0 T I-9 A E D E O R IN AE11 AE12 AE1R 3 T AE14 D AE15 AE16 L AE17 AE18 AE19 R D S R 3 N C D 1 E EN OW TE -

C.106 BCZ 3.81/../180 Technical Data Product Data Accessories BCZ 3.81

Connectors in 3.81 mm pitch Series BC/SC 3.81 BCZ 3.81/../180 Product data BCZ 3.81/../180 IEC: 320 V / 17.5 A / 0.2 - 1.5 mm² UL: 300 V / 10 A / AWG 28 - 16 For additional articles and information, refer to catalog.weidmueller.com OMNIMATE Signal OMNIMATE PCB Connectors Note: • Additional colours on request • Gold-plated contact surfaces on request • Rated current related to rated cross-section and min. No. of poles. • Wire end ferrule without plastic collar to DIN 46228/1 • Wire end ferrule with plastic collar to DIN 46228/4 Female plug with screw connection. Wire outlet • P on drg. = pitch 180° (wire is straight on to the direction of • Rated data refer only to the component itself. Clearance and plugging). creepage distances to other components are to be designed • Available in closed version, with screw flange in accordance with the relevant application standards. Dimensioned drawing C (F) and lock and release-lever (LR). Weidmüller’s 3.81-mm-pitch (0.15 inch) plug-in connectors are compatible with the L1 + P 16,1 layouts of standard connectors and offer 0.634" space for labelling and coding. 11,1 0.437" P 9 0.354" L1 Technical data Accessories Ordering data In compliance with IEC 60664-1 / IEC 61984 Note: Refer to the Accessories chapter for additional accessories. Solder pin length Clamping range, max. mm² 0.08...1.5 Hood Order No. Colour orange black Solid core H05(07) V-U mm² 0.2...1.5 BCZ 3.81 AH03 1005280000 Pitch 3.81 mm Stranded H07 V-R BCZ 3.81 AH04 1005290000 Pol. -

1St IRF Asia Regional Congress & Exhibition

1st IRF Asia Regional Congress & Exhibition Bali, Indonesia November 17–19 , 2014 For Professionals. By Professionals. "Building the Trans-Asia Highway" Bali’s Mandara toll road Executive Summary International Road Federation Better Roads. Better World. 1 International Road Federation | Washington, D.C. ogether with the Ministry of Public Works Indonesia, we chose the theme “Building the Trans-Asia Highway” to bring new emphasis to a visionary project Tthat traces its roots back to 1959. This Congress brought the region’s stakeholders together to identify new and innovative resources to bridge the current financing gap, while also sharing case studies, best practices and new technologies that can all contribute to making the Trans-Asia Highway a reality. This Congress was a direct result of the IRF’s strategic vision to become the world’s leading industry knowledge platform to help countries everywhere progress towards safer, cleaner, more resilient and better connected transportation systems. The Congress was also a reflection of Indonesia’s rising global stature. Already the largest economy in Southeast Asia, Indonesia aims to be one of world’s leading economies, an achievement that will require the continued development of not just its own transportation network, but also that of its neighbors. Thank you for joining us in Bali for this landmark regional event. H.E. Eng. Abdullah A. Al-Mogbel IRF Chairman Minister of Transport, Kingdom of Saudi Arabia Indonesia Hosts the Region’s Premier Transportation Meeting Indonesia was the proud host to the 1st IRF Asia Regional Congress & Exhibition, a regional gathering of more than 700 transportation professionals from 52 countries — including Ministers, senior national and local government officials, academics, civil society organizations and industry leaders. -

Characterization and Transferability of Microsatellite Markers of the Cultivated Peanut (Arachis Hypogaea)

BMC Plant Biology BioMed Central Research article Open Access Characterization and transferability of microsatellite markers of the cultivated peanut (Arachis hypogaea) Marcos A Gimenes*1,2, Andrea A Hoshino1, Andrea VG Barbosa1, Dario A Palmieri1 and Catalina R Lopes1 Address: 1Laboratório de Biotecnologia e Genética Molecular (BIOGEM), Departamento de Genética, Instituto de Biociências, Universidade Estadual Paulista (UNESP), Botucatu, SP, Brazil and 2Instituto Agronômico de Campinas – RGV, Caixa Postal 28, Campinas, SP, Brazil Email: Marcos A Gimenes* - [email protected]; Andrea A Hoshino - [email protected]; Andrea VG Barbosa - [email protected]; Dario A Palmieri - [email protected]; Catalina R Lopes - [email protected] * Corresponding author Published: 27 February 2007 Received: 3 March 2006 Accepted: 27 February 2007 BMC Plant Biology 2007, 7:9 doi:10.1186/1471-2229-7-9 This article is available from: http://www.biomedcentral.com/1471-2229/7/9 © 2007 Gimenes et al; licensee BioMed Central Ltd. This is an Open Access article distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/2.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited. Abstract Background: The genus Arachis includes Arachis hypogaea (cultivated peanut) and wild species that are used in peanut breeding or as forage. Molecular markers have been employed in several studies of this genus, but microsatellite markers have only been used in few investigations. Microsatellites are very informative and are useful to assess genetic variability, analyze mating systems and in genetic mapping. The objectives of this study were to develop A. -

Asian Highway Handbook United Nations

ECONOMIC AND SOCIAL COMMISSION FOR ASIA AND THE PACIFIC ASIAN HIGHWAY HANDBOOK UNITED NATIONS New York, 2003 ST/ESCAP/2303 The Asian Highway Handbook was prepared under the direction of the Transport and Tourism Division of the United Nations Economic and Social Commission for Asia and the Pacific. The team of staff members of the Transport and Tourism Division who prepared the Handbook comprised: Fuyo Jenny Yamamoto, Tetsuo Miyairi, Madan B. Regmi, John R. Moon and Barry Cable. Inputs for the tourism- related parts were provided by an external consultant: Imtiaz Muqbil. The designations employed and the presentation of the material in this publication do not imply the expression of any opinion whatsoever on the part of the Secretariat of the United Nations concerning the legal status of any country, territory, city or area or of its authorities, or concerning the delimitation of its frontiers or boundaries. This publication has been issued without formal editing. CONTENTS I. INTRODUCTION TO THE ASIAN HIGHWAY………………. 1 1. Concept of the Asian Highway Network……………………………… 1 2. Identifying the Network………………………………………………. 2 3. Current status of the Asian Highway………………………………….. 3 4. Formalization of the Asian Highway Network……………………….. 7 5. Promotion of the Asian Highway……………………………………... 9 6. A Vision of the Future………………………………………………… 10 II. ASIAN HIGHWAY ROUTES IN MEMBER COUNTRIES…... 16 1. Afghanistan……………………………………………………………. 16 2. Armenia……………………………………………………………….. 19 3. Azerbaijan……………………………………………………………... 21 4. Bangladesh……………………………………………………………. 23 5. Bhutan…………………………………………………………………. 27 6. Cambodia……………………………………………………………… 29 7. China…………………………………………………………………... 32 8. Democratic People’s Republic of Korea……………………………… 36 9. Georgia………………………………………………………………... 38 10. India…………………………………………………………………… 41 11. Indonesia………………………………………………………………. 45 12. Islamic Republic of Iran………………………………………………. 49 13 Japan………………………………………………………………….. -

Identification of Rfk-1, a Meiotic Driver Undergoing RNA Editing in Neurospora

HIGHLIGHTED ARTICLE | INVESTIGATION Identification of rfk-1, a Meiotic Driver Undergoing RNA Editing in Neurospora Nicholas A. Rhoades,* Austin M. Harvey,*,1 Dilini A. Samarajeewa,*,1 Jesper Svedberg,† Aykhan Yusifov,* Anna Abusharekh,* Pennapa Manitchotpisit,* Daren W. Brown,‡ Kevin J. Sharp,* David G. Rehard,§,** Joshua Peters,* Xavier Ostolaza-Maldonado,* Jackson Stephenson,* Patrick K. T. Shiu,§ Hanna Johannesson,† and Thomas M. Hammond*,2 *School of Biological Sciences, Illinois State University, Normal, Illinois 61790, †Department of Organismal Biology, Uppsala University, Norbyvägen 18D, 752 36 Uppsala, Sweden, ‡Mycotoxin Prevention and Applied Microbiology, National Center for Agricultural Utilization Research, U.S. Department of Agriculture, Agricultural Research Service, Peoria, Illinois 61604, §Division of Biological Sciences, University of Missouri, Columbia, Missouri 65211, and **Department of Biology, University of Iowa, Iowa 52242 ABSTRACT Sk-2 is a meiotic drive element that was discovered in wild populations of Neurospora fungi over 40 years ago. While early studies quickly determined that Sk-2 transmits itself through sexual reproduction in a biased manner via spore killing, the genetic factors responsible for this phenomenon have remained mostly unknown. Here, we identify and characterize rfk-1, a gene required for Sk-2-based spore killing. The rfk-1 gene contains four exons, three introns, and two stop codons, the first of which undergoes RNA editing to a tryptophan codon during sexual development. Translation of an unedited rfk-1 transcript in vegetative tissue is expected to produce a 102-amino acid protein, whereas translation of an edited rfk-1 transcript in sexual tissue is expected to produce a protein with 130 amino acids. These findings indicate that unedited and edited rfk-1 transcripts exist and that these transcripts could have different roles with respect to the mechanism of meiotic drive by spore killing. -

Europe Price List

2019 Europe Price List EUROPE PRICE LIST 2019 Terms and Conditions of Sale Conditions générales de vente Condizioni generali di vendita Allgemeine Verkaufsbedingungen By placing an order, the customer Toutes les commandes passées Tutti gli ordini effettuati com- Mit Aufgabe einer Bestellung er- fully accepts the following Terms impliquent que l’acheteur accep- portano la piena accettazione, kennt der Kunde die folgenden and Conditions of Sale: te intégralement les Conditions da parte dell’acquirente, delle Allgemeinen Verkaufsbedingun- générales de vente suivantes : seguenti Condizioni Generali di gen in vollem Umfang an: 0. Validity Vendita: Price list valid from 18/02/2019. 0. Validité 0. Gültigkeit Tarif valable à partir de 18/02/2019. 0. Validità Die Preisliste gilt ab dem 1. Prices Listino valido dal 18/02/2019. 18/02/2019. The prices applied will be those 1. Prix valid on the date of reception of Les tarifs en vigueur s’appliquent 1. Prezzi 1. Preise the order (RRP, VAT not included). à la date de réception de la com- Verranno applicate le tariffe Es werden die Preise berechnet, All prices featured in the price list mande (prix PVPR, TVA non com- vigenti alla data di ricezione die am Tag des Auftrageingangs include the WEEE eco-fee. prise). Tous les prix indiqués dans dell’ordine (prezzi di vendita al gelten (UVP ohne Mehrwerts- la liste des tarifs comprennent pubblico consigliati, IVA esclusa). teuer). Alle angegebenen Preise 2. Delivery times l’éco-participation DEEE. Tutti i prezzi indicati nel listino sind einschließlich WEEE Gebühr. Delivery times will be confirmed at prezzi sono con contributo ECO- the moment of placing the order 2. -

The Effect of Road Upgrading to Overland Trade in Asian Highway Network Ziyodullo PARPIEV ∗ Jamshid SODIKOV **

Eurasian Journal of Business and Economics 2008, 1 (2), 85-101. The Effect of Road Upgrading to Overland Trade in Asian Highway Network Ziyodullo PARPIEV ∗ Jamshid SODIKOV ** Abstract This paper investigates an impact of road upgrading and improvement on overland trade in 18 out of 32 Asian Highway Network member countries. A regression based cost model was developed. The results indicate that approximately 6.5 billion US dollars is required to upgrade and improve surface condition of the selected roads with total length of 15,842 km. The gravity model approach was adopted to quantitatively evaluate overland trade expansion assuming pessimistic and optimistic scenarios: improvements in road quality indices up to 50 and up to 75, respectively. The results suggests that in the first scenario total intra-regional trade will increase by about 20 percent or 48.7 billion US dollars annually, while second scenario predicts that trade will increase by about 35 percent or 89.5 billion US dollars annually. Keywords: Asian Highway Network, road transport, gravity model. Jel Classification: F12, F15, F17. ∗ Advisor-Economist, UNDP Uzbekistan Country Office, Email: [email protected] ** Chief Engineer, Road Research Institute, Tashkent, Uzbekistan The views expressed in this paper are those of the author(s) and do not necessarily represent those of organizations the authors are associated with. Ziyodullo PARPIEV & Jamshid SODIKOV 1. Introduction In 1992, the United Nations Economic and Social Commission for Asia and the Pacific (ESCAP) endorsed the Asian Land Transport Infrastructure Development (ALTID) project comprising of the Asian Highway and the Trans-Asian Railway network. The formalization of the Asian Highway, through the Intergovernmental Agreement on Asian Highway Network (AHN), was adopted in November 2003. -

Growing Together Articulates a Number of Proposals That Can Help the Region Exploit Its Huge Untapped Potential for Regional Economic Integration

i Photo by Warren Field ii FOREWORD For the global economy, these are difficult times. The world is emerging from a crisis whose aftershocks continue to resonate – trapping some of the richest economies in recession and shaking the foundations of one of the world’s major currencies. Here at ESCAP, there are historical echoes. What is now the Economic and Social Commission for Asia and the Pacific was founded more than 60 years ago – also in the aftermath of a global crisis. The countries of Asia and the Pacific established their new Commission partly to assist them in rebuilding their economies as they came out of the yoke of colonialism and the Second World War. The newly established ECAFE, as ESCAP was called then, held a ministerial conference on regional economic cooperation in 1963 that resolved to set up the Asian Development Bank with the aim of assisting the countries in the region in rebuilding their economies. Fifty years later, the Asia-Pacific region is again at a crossroads, on this occasion seeking ways and means to sustain its dynamism in a dramatically changed global context in the aftermath of a global financial and economic crisis. An important change is the fact that, burdened by huge debts and global imbalances, the advanced economies of the West are no longer able to play the role of engines of growth for the Asia-Pacific region that they played in the past. Hence, the Asia-Pacific region has to look for new engines of growth. The secretariat of ESCAP has argued over the past few years that regional developmental challenges, such as poverty and wide disparities in social and physical infrastructure, can be turned into opportunities for sustaining growth in the future. -

Multi-Hazard Mitigation Plan 2020 Update

LUMMI NATION MULTI-HAZARD MITIGATION PLAN 2020 UPDATE Prepared For: Lummi Indian Business Council (LIBC) Funded By: U.S. Environmental Protection Agency Performance Partnership Grant (Grant No. BG-01J57901-0) Prepared By: Water Resources Division Lummi Natural Resources Department Contributors: Kara Kuhlman CFM, Water Resources Manager Andy Ross, LG, LHg, CFM, Water Resources Specialist III/Hydrologist Gerald Gabrisch GISP, GIS Manager Adopted by the Lummi Indian Business Council: September 15, 2020 Approved by the Federal Emergency Management Agency: October 1, 2020 This project has been funded wholly or in part by the United States Environmental Protection Agency under Assistance Agreement BG-01J57901-0 to the Lummi Nation. The contents of this document do not necessarily reflect the views and policies of the Environmental Protection Agency, nor does mention of trade names or commercial products constitute endorsement or recommendation for use. TABLE OF CONTENTS 1. Introduction ......................................................................................................................... 9 1.1. Goals and Objectives .....................................................................................................10 1.2. Sections .........................................................................................................................11 2. Planning Process ...............................................................................................................13 2.1. Plan Preparation ............................................................................................................13