Chapter 4: Programmable Logic Devices

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Monolithic Integration of a Novel Microfluidic Device with Silicon Light Emitting Diode-Antifuse and Photodetector

ESSDERC 2002 Monolithic Integration of a Novel Microfluidic Device with Silicon Light Emitting Diode-Antifuse and Photodetector P. LeMinh, J. Holleman, J.W.Berenschot,N.R.Tas,A.vandenBerg MESA+ Research Institute, University of Twente, the Netherlands E-mail [email protected] Abstract developing an CMOS compatible etching recipe using Tetra Methyl Ammonium Hydroxide (TMAH). Light emitting diode antifuse has been integrated into In the next sections of the paper, fabrication process, a microfluidic device that is realized with extended some critical technological design parameters, electrical standard CMOS technological steps. The device and optical properties, few results on first applications comprises of a microchannel sandwiched between a will be described respectively. photodiode detector and a nanometer-scale diode antifuse light emitter. Within this contribution, the 2. Device realization device fabrication process, working principle and properties will be discussed. Change in the interference The realization of the device (figure 1) is a 10-mask fringe of the antifuse spectra has been measured due to process. The starting material is a 3-in silicon n-type the filling of the channel. Preliminary applications are wafer with standard doping. First of all, junction electroosmotic flow speed measurement, detection of photodiode areas were fabricated by implantation of absorptivity of liquids in the channel… boron. So as not to make any step height difference at the junction between n-type and p-type region, thick resist 1. Introduction was used as masking layer for the implantation. This is important to the evenness of the channel. The shape of Silicon is well-known as an electronic and mechanical the channel was then produced by shaping a layer of material but hardly ever used as an active optoelectronic 500nm thick LPCVD polysilicon deposited on top of the element, due to its inefficient radiative recombination first silicon rich nitride (SiRN) layer. -

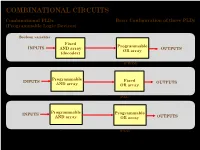

COMBINATIONAL CIRCUITS Combinational Plds Basic Configuration of Three Plds (Programmable Logic Devices)

COMBINATIONAL CIRCUITS Combinational PLDs Basic Configuration of three PLDs (Programmable Logic Devices) Boolean variables Fixed Programmable INPUTS AND array OUTPUTS OR array (decoder) Programmable Read-Only Memory (PROM) Programmable INPUTS Fixed OUTPUTS AND array OR array Programmable Array Logic (PAL) Programmable INPUTS Programmable AND array OR array OUTPUTS (Field) Programmable Logic Array (PLA) 1 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Two-level AND-OR Arrays (Programmable Logic Devices) F (C,B, A) = CBA + CB A A AND B + V B C A C B F C F AND F + V 1 B OR C Multiple functions Simplified equivalent circuit for two-level AND-OR array 2 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Field-programmable AND and OR Arrays (Programmable Logic Devices) Field-programmable logic elements are devices that contain uncommitted AND/OR arrays that are (programmed) configured by the designer. + V + V A A F (C,B, A) F (C,B, A) = CBA B B C C Unprogrammed AND array Fuse can be "blown" by passing a high current through it. 3 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Field-programmable AND and OR Arrays (Programmable Logic Devices) F (P1 ,P2 ,P3 ) = P1 + P3 P1 P1 P2 P2 P3 P3 F F (P1 ,P2 ,P3 ) Unprogrammed OR array Programmed OR array P1 P2 P3 P1 + P3 4 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Output Polarity Options (Programmable Logic Devices) I1 Ik Active high Active low Complementary outputs Programmable polarity P P 1 m + V 5 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Bidirectional Pins and Feed back Lines (Programmable Logic Devices) I1 Ik Feedback IOm Three-state driver 6 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs PLA (Programmable Logic Array) (Programmable Logic Devices) If we use ROM to implement the Boolean function we will waste the silicon area. -

Configurable RISC-V Softcore Processor for FPGA Implementation

1 Configurable RISC-V softcore processor for FPGA implementation Joao˜ Filipe Monteiro Rodrigues, Instituto Superior Tecnico,´ Universidade de Lisboa Abstract—Over the past years, the processor market has and development of several programming tools. The RISC-V been dominated by proprietary architectures that implement Foundation controls the RISC-V evolution, and its members instruction sets that require licensing and the payment of fees to are responsible for promoting the adoption of RISC-V and receive permission so they can be used. ARM is an example of one of those companies that sell its microarchitectures to participating in the development of the new ISA. In the list of the manufactures so they can implement them into their own members are big companies like Google, NVIDIA, Western products, and it does not allow the use of its instruction set Digital, Samsung, or Qualcomm. (ISA) in other implementations without licensing. The RISC-V The main goal of this work is the development of a RISC- instruction set appeared proposing the hardware and software V softcore processor to be implemented in an FPGA, using development without costs, through the creation of an open- source ISA. This way, it is possible that any project that im- a non-RISC-V core as the base of this architecture. The plements the RISC-V ISA can be made available open-source or proposed solution is focused on solving the problems and even implemented in commercial products. However, the RISC- limitations identified in the other RISC-V cores that were V solutions that have been developed do not present the needed analyzed in this thesis, especially in terms of the adaptability requirements so they can be included in projects, especially the and flexibility, allowing future modifications according to the research projects, because they offer poor documentation, and their performances are not suitable. -

Development of a Programmable Array Logic

i DEVELOPMENT OF A PROGRAMMABLE ARRAY LOGIC PROGRAMMER USING A HOME COMPUTER by GERT DANIEL JORDAAN Dissertation submitted in compliance with the requirements for the MASTER'S DIPLOMA in TECHNOLOGY in the Department of Electronics at the TECHNIKON O. F . S . OCTOBER, 1988. Supervisor: Prof. F.W. Bruwer Co-supervisor: Mr. B. de Witt © Central University of Technology, Free State ACKNOWLEDGEMENTS I would like to thank the following persons without whose help this project could hardly have been completed: The supervisor, prof. F.W. Bruwer, and co-supervisor, mr. 8. de Witt, for help and guidance during the course of the project. Mr. H.F. Coetzer for technical as well as philolog ical assistance. It is really appreciated that time could be found in his very full schedule, for this assistance. Dr. C.A.J. van Rensburg for his per_onal interest in the research project and for continuous encouragement and help. Dr. J. van der Mer-we for his assistance - in particular with respect to the registration and other administrative aspects of the project. / Miss M. du Toit who was largely responsible for the word processing. For the guidance provided by my parents and the opportuni- ties which they afforded me. My children, Tania, Johan, Madelie and Lourens,. whose main contribution was to have to forego much of my attention and time for such a long period. Last, but not least, my wife, Christa, for her encouragement and understanding. © Central University of Technology,ii Free State CONTENTS PAGE Cilapter 1 1 Intr--oduc tion 1.1 Recent Trends in Electronics 1 1.2 Problem Investigated 1 1.3 Development of PAL Programmer 3 1.3.1 Generation of Fuse Map 3 1.3.2 Programming of Programmable Array Logic 3 Devices 1 . -

Intel Quartus Prime Pro Edition User Guide: Partial Reconfiguration Send Feedback

Intel® Quartus® Prime Pro Edition User Guide Partial Reconfiguration Updated for Intel® Quartus® Prime Design Suite: 19.3 Subscribe UG-20136 | 2019.11.18 Send Feedback Latest document on the web: PDF | HTML Contents Contents 1. Creating a Partial Reconfiguration Design.......................................................................4 1.1. Partial Reconfiguration Terminology..........................................................................5 1.2. Partial Reconfiguration Process Sequence..................................................................6 1.3. Internal Host Partial Reconfiguration........................................................................ 7 1.4. External Host Partial Reconfiguration........................................................................ 9 1.5. Partial Reconfiguration Design Considerations............................................................9 1.5.1. Partial Reconfiguration Design Guidelines.................................................... 11 1.5.2. PR File Management.................................................................................12 1.5.3. Evaluating PR Region Initial Conditions....................................................... 16 1.5.4. Creating Wrapper Logic for PR Regions........................................................16 1.5.5. Creating Freeze Logic for PR Regions.......................................................... 17 1.5.6. Resetting the PR Region Registers.............................................................. 18 1.5.7. Promoting -

ECE 546 Lecture -20 Power Distribution Networks

ECE 546 Lecture ‐20 Power Distribution Networks Spring 2020 Jose E. Schutt-Aine Electrical & Computer Engineering University of Illinois [email protected] ECE 546 – Jose Schutt‐Aine 1 IC on Package ECE 546 – Jose Schutt‐Aine 2 IC on Package ECE 546 – Jose Schutt‐Aine 3 Power-Supply Noise - Power-supply-level fluctuations - Delta-I noise - Simultaneous switching noise (SSN) - Ground bounce VOH Ideal Actual VOL Vout Vout Time 4 ECE 546 – Jose Schutt‐Aine 4 Voltage Fluctuations • Voltage fluctuations can cause the following Reduction in voltage across power supply terminals. May prevent devices from switching Increase in voltage across power supply terminalsreliability problems Leakage of the voltage fluctuation into transistors Timing errors, power supply noise, delta‐I noise, simultaneous switching noise (SSN) ECE 546 – Jose Schutt‐Aine 5 Power-Supply-Level Fluctuations • Total capacitive load associated with an IC increases as minimum feature size shrinks • Average current needed to charge capacitance increases • Rate of change of current (dI/dt) also increases • Total chip current may change by large amounts within short periods of time • Fluctuation at the power supply level due to self inductance in distribution lines ECE 546 – Jose Schutt‐Aine 6 Reducing Power-Supply-Level Fluctuations Minimize dI/dt noise • Decoupling capacitors • Multiple power & ground pins • Taylored driver turn-on characteristics Decoupling capacitors • Large capacitor charges up during steady state • Assumes role of power supply during current switching • Leads -

CHAPTER 3: Combinational Logic Design with Plds

CHAPTER 3: Combinational Logic Design with PLDs LSI chips that can be programmed to perform a specific function have largely supplanted discrete SSI and MSI chips in board-level designs. A programmable logic device (PLD), is an LSI chip that contains a “regular” circuit structure, but that allows the designer to customize it for a specific application. PLDs sold in the market is not customized with specific functions. Instead, it is programmed by the purchaser to perform a function required by a particular application. PLD-based board-level designs often cost less than SSI/MSI designs for a number of reasons. Since PLDs provide more functionality per chip, the total chip and printed- circuit-board (PCB) area are less. Manufacturing costs are reduced in other ways too. A PLD-based board manufacturer needs to keep samples of few, “generic” PLD types, instead of many different MSI part types. This reduces overall inventory requirements and simplifies handling. PLD-type structures also appear as logic elements embedded in LSI chips, where chip count and board areas are not an issue. Despite the fact that a PLD may “waste” a certain number of gates, a PLD structure can actually reduce circuit cost because its “regular” physical structure may use less chip area than a “random logic” circuit. More importantly, the logic function performed by the PLD structure can often be “tweaked” in successive chip revisions by changing just one or a few metal mask layers that define signal connections in the array, instead of requiring a wholesale addition of gates and gate inputs and subsequent re-layout of a “random logic” design. -

PPBI for OTP Fpgas Final Report

ESA UNCLASSIFIED – For Official Use estec European Space Research and Technology Centre Keplerlaan 1 2201 AZ Noordwijk The Netherlands Tel. (31) 71 5656565 Fax (31) 71 5656040 www.esa.int PPBI for OTP FPGAs Final Report Prepared by: Ken Hernan Reference: ESCC WG 01/13 Issue: 1 Revision: 9 Date of Issue: 23rd May 2014 Status: Final Document Type: WG Report ESA UNCLASSIFIED – For Official Use ESA UNCLASSIFIED – For Official Use Table of contents: 1 INTRODUCTION ...................................................................................................................................................... 5 1.1 SCOPE OF THE DOCUMENT ..................................................................................................................................... 5 1.2 APPLICABLE AND REFERENCE DOCUMENTS ........................................................................................................... 5 1.2.1 Reference Documents (RDs) .......................................................................................................................... 5 1.3 ACRONYMS AND ABBREVIATIONS .......................................................................................................................... 6 2 EXECUTIVE SUMMARY ........................................................................................................................................ 9 3 WOKRING GROUP ACTIVITIES ........................................................................................................................ 15 4 BACKGROUND -

Semiconductor Devices

H01L CPC COOPERATIVE PATENT CLASSIFICATION H ELECTRICITY (NOTE omitted) H01 BASIC ELECTRIC ELEMENTS (NOTES omitted) H01L SEMICONDUCTOR DEVICES; ELECTRIC SOLID STATE DEVICES NOT OTHERWISE PROVIDED FOR (use of semiconductor devices for measuring G01; resistors in general H01C; magnets, inductors, transformers H01F; capacitors in general H01G; electrolytic devices H01G 9/00; batteries, accumulators H01M; waveguides, resonators, or lines of the waveguide type H01P; line connectors, current collectors H01R; stimulated-emission devices H01S; electromechanical resonators H03H; loudspeakers, microphones, gramophone pick-ups or like acoustic electromechanical transducers H04R; electric light sources in general H05B; printed circuits, hybrid circuits, casings or constructional details of electrical apparatus, manufacture of assemblages of electrical components H05K; use of semiconductor devices in circuits having a particular application, see the subclass for the application) NOTES 1. This subclass covers: • electric solid state devices which are not covered by any other subclass and details thereof, and includes: semiconductor devices adapted for rectifying, amplifying, oscillating or switching; semiconductor devices sensitive to radiation; electric solid state devices using thermoelectric, superconductive, piezo-electric, electrostrictive, magnetostrictive, galvano- magnetic or bulk negative resistance effects and integrated circuit devices; • photoresistors, magnetic field dependent resistors, field effect resistors, capacitors with potential-jump -

Introduction to ASIC Design

’14EC770 : ASIC DESIGN’ An Introduction Application - Specific Integrated Circuit Dr.K.Kalyani AP, ECE, TCE. 1 VLSI COMPANIES IN INDIA • Motorola India – IC design center • Texas Instruments – IC design center in Bangalore • VLSI India – ASIC design and FPGA services • VLSI Software – Design of electronic design automation tools • Microchip Technology – Offers VLSI CMOS semiconductor components for embedded systems • Delsoft – Electronic design automation, digital video technology and VLSI design services • Horizon Semiconductors – ASIC, VLSI and IC design training • Bit Mapper – Design, development & training • Calorex Institute of Technology – Courses in VLSI chip design, DSP and Verilog HDL • ControlNet India – VLSI design, network monitoring products and services • E Infochips – ASIC chip design, embedded systems and software development • EDAIndia – Resource on VLSI design centres and tutorials • Cypress Semiconductor – US semiconductor major Cypress has set up a VLSI development center in Bangalore • VDAT 2000 – Info on VLSI design and test workshops 2 VLSI COMPANIES IN INDIA • Sandeepani – VLSI design training courses • Sanyo LSI Technology – Semiconductor design centre of Sanyo Electronics • Semiconductor Complex – Manufacturer of microelectronics equipment like VLSIs & VLSI based systems & sub systems • Sequence Design – Provider of electronic design automation tools • Trident Techlabs – Power systems analysis software and electrical machine design services • VEDA IIT – Offers courses & training in VLSI design & development • Zensonet Technologies – VLSI IC design firm eg3.com – Useful links for the design engineer • Analog Devices India Product Development Center – Designs DSPs in Bangalore • CG-CoreEl Programmable Solutions – Design services in telecommunications, networking and DSP 3 Physical Design, CAD Tools. • SiCore Systems Pvt. Ltd. 161, Greams Road, ... • Silicon Automation Systems (India) Pvt. Ltd. ( SASI) ... • Tata Elxsi Ltd. -

Recent Advancement in the Memristor Memory Development Ravikumar K

International Journal of Innovative Technology and Exploring Engineering (IJITEE) ISSN: 2278-3075, Volume-9 Issue-7, May 2020 Recent Advancement in the Memristor Memory Development Ravikumar K. I, Sukumar R voltages as referred to in [19]) and d) manufacturing methods Abstract: Meritor is a newly-created tool and because of its compliant with CMOS relative to other NVM systems. nanometer scale and different electrical properties it has received Relative to other MRM (Resistive random access memory) much interest from advanced electronics designers since it was there are specific advantages. The RRAM is combined with discovered. The memory capacity of a memrist is one of the most significant features. In this paper, about 50 papers on designing the SRAM cell in past works such as [20–23], but each of memristor, optimization rules for reducing power, area for configuration either contributes to substantial deterioration of storing the data into memristor and implemented the full adders the fundamental SRAM reading process or absorbs a huge using memristor using the Pspice simulator. The paper ultimately amount of energy for the storage / restoration of data to / from addresses the complex study lapses and obstacles in constructing RRAM as described further in depth in section 4. In our paper the memorial that will enable scholars and thinkers lead to more analysis. we give a new NV-SRAM 8T1R that is similar to a standard Keywords: memristor, optimization. SRAM 6 T device with reading power, delay and noise tolerance. In turn, since only one RRAM cell is required for I. INTRODUCTION the off-time storage of SRAM data, energy used for processing RRAM data is reduced by more than 60% relative The resistive memory of the Crossbar has recently gained to the lowest energy density of previous RRAM NV-SRAM tremendous publicity owing to its amazing high density and designs. -

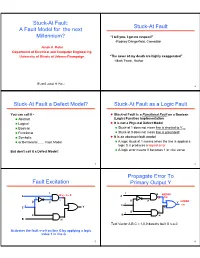

Stuck-At Fault As a Logic Fault

Stuck-At Fault: Stuck-At Fault A Fault Model for the next Millennium? “I tell you, I get no respect!” -Rodney Dangerfield, Comedian Janak H. Patel Department of Electrical and Computer Engineering University of Illinois at Urbana-Champaign “The news of my death are highly exaggerated” -Mark Twain, Author © 2005 Janak H. Patel 2 Stuck-At Fault a Defect Model? Stuck-At Fault as a Logic Fault You can call it - z Stuck-at Fault is a Functional Fault on a Boolean Abstract (Logic) Function Implementation Logical z It is not a Physical Defect Model Boolean Stuck-at 1 does not mean line is shorted to VDD Functional Stuck-at 0 does not mean line is grounded! Symbolic z It is an abstract fault model or Behavioral …... Fault Model A logic stuck-at 1 means when the line is applied a logic 0, it produces a logical error But don’t call it a Defect Model! A logic error means 0 becomes 1 or vice versa 3 4 Propagate Error To Fault Excitation Primary Output Y 1 1 G ERROR A G s - a - 0 A 0 1 x X 1/0 D 1 D F ERROR F 0 Y 0 C 1/0 C Y 0 0 0 E E B H B H Test Vector A,B,C = 1,0,0 detects fault G s-a-0 Activates the fault s-a-0 on line G by applying a logic value 1 in line G 5 6 Unmodeled Defect Detection Defect Sites z Internal to a Logic Gate or Cell Other Logic Transistor Defects – Stuck-On, Stuck-Open, Leakage, Shorts between treminals ERROR Defect G ERROR z External to a Gate or Cell Interconnect Defects – Shorts and Opens D 1 F 0 Y ERROR C 0 0 0 E B H G I 7 8 Defects in Physical Cells Fault Modeling z Physical z Electrical Physical Cells such as NAND, NOR, XNOR, AOI, OAI, MUX2, etc.