MOS Transistor

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

ECE 255, MOSFET Basic Configurations

ECE 255, MOSFET Basic Configurations 8 March 2018 In this lecture, we will go back to Section 7.3, and the basic configurations of MOSFET amplifiers will be studied similar to that of BJT. Previously, it has been shown that with the transistor DC biased at the appropriate point (Q point or operating point), linear relations can be derived between the small voltage signal and current signal. We will continue this analysis with MOSFETs, starting with the common-source amplifier. 1 Common-Source (CS) Amplifier The common-source (CS) amplifier for MOSFET is the analogue of the common- emitter amplifier for BJT. Its popularity arises from its high gain, and that by cascading a number of them, larger amplification of the signal can be achieved. 1.1 Chararacteristic Parameters of the CS Amplifier Figure 1(a) shows the small-signal model for the common-source amplifier. Here, RD is considered part of the amplifier and is the resistance that one measures between the drain and the ground. The small-signal model can be replaced by its hybrid-π model as shown in Figure 1(b). Then the current induced in the output port is i = −gmvgs as indicated by the current source. Thus vo = −gmvgsRD (1.1) By inspection, one sees that Rin = 1; vi = vsig; vgs = vi (1.2) Thus the open-circuit voltage gain is vo Avo = = −gmRD (1.3) vi Printed on March 14, 2018 at 10 : 48: W.C. Chew and S.K. Gupta. 1 One can replace a linear circuit driven by a source by its Th´evenin equivalence. -

An Integrated Semiconductor Device Enabling Non-Optical Genome Sequencing

ARTICLE doi:10.1038/nature10242 An integrated semiconductor device enabling non-optical genome sequencing Jonathan M. Rothberg1, Wolfgang Hinz1, Todd M. Rearick1, Jonathan Schultz1, William Mileski1, Mel Davey1, John H. Leamon1, Kim Johnson1, Mark J. Milgrew1, Matthew Edwards1, Jeremy Hoon1, Jan F. Simons1, David Marran1, Jason W. Myers1, John F. Davidson1, Annika Branting1, John R. Nobile1, Bernard P. Puc1, David Light1, Travis A. Clark1, Martin Huber1, Jeffrey T. Branciforte1, Isaac B. Stoner1, Simon E. Cawley1, Michael Lyons1, Yutao Fu1, Nils Homer1, Marina Sedova1, Xin Miao1, Brian Reed1, Jeffrey Sabina1, Erika Feierstein1, Michelle Schorn1, Mohammad Alanjary1, Eileen Dimalanta1, Devin Dressman1, Rachel Kasinskas1, Tanya Sokolsky1, Jacqueline A. Fidanza1, Eugeni Namsaraev1, Kevin J. McKernan1, Alan Williams1, G. Thomas Roth1 & James Bustillo1 The seminal importance of DNA sequencing to the life sciences, biotechnology and medicine has driven the search for more scalable and lower-cost solutions. Here we describe a DNA sequencing technology in which scalable, low-cost semiconductor manufacturing techniques are used to make an integrated circuit able to directly perform non-optical DNA sequencing of genomes. Sequence data are obtained by directly sensing the ions produced by template-directed DNA polymerase synthesis using all-natural nucleotides on this massively parallel semiconductor-sensing device or ion chip. The ion chip contains ion-sensitive, field-effect transistor-based sensors in perfect register with 1.2 million wells, which provide confinement and allow parallel, simultaneous detection of independent sequencing reactions. Use of the most widely used technology for constructing integrated circuits, the complementary metal-oxide semiconductor (CMOS) process, allows for low-cost, large-scale production and scaling of the device to higher densities and larger array sizes. -

Advanced MOSFET Structures and Processes for Sub-7 Nm CMOS Technologies

Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies By Peng Zheng A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences in the Graduate Division of the University of California, Berkeley Committee in charge: Professor Tsu-Jae King Liu, Chair Professor Laura Waller Professor Costas J. Spanos Professor Junqiao Wu Spring 2016 © Copyright 2016 Peng Zheng All rights reserved Abstract Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies by Peng Zheng Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences University of California, Berkeley Professor Tsu-Jae King Liu, Chair The remarkable proliferation of information and communication technology (ICT) – which has had dramatic economic and social impact in our society – has been enabled by the steady advancement of integrated circuit (IC) technology following Moore’s Law, which states that the number of components (transistors) on an IC “chip” doubles every two years. Increasing the number of transistors on a chip provides for lower manufacturing cost per component and improved system performance. The virtuous cycle of IC technology advancement (higher transistor density lower cost / better performance semiconductor market growth technology advancement higher transistor density etc.) has been sustained for 50 years. Semiconductor industry experts predict that the pace of increasing transistor density will slow down dramatically in the sub-20 nm (minimum half-pitch) regime. Innovations in transistor design and fabrication processes are needed to address this issue. The FinFET structure has been widely adopted at the 14/16 nm generation of CMOS technology. -

Vlsi Design Lecture Notes B.Tech (Iv Year – I Sem) (2018-19)

VLSI DESIGN LECTURE NOTES B.TECH (IV YEAR – I SEM) (2018-19) Prepared by Dr. V.M. Senthilkumar, Professor/ECE & Ms.M.Anusha, AP/ECE Department of Electronics and Communication Engineering MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY (Autonomous Institution – UGC, Govt. of India) Recognized under 2(f) and 12 (B) of UGC ACT 1956 (Affiliated to JNTUH, Hyderabad, Approved by AICTE - Accredited by NBA & NAAC – ‘A’ Grade - ISO 9001:2015 Certified) Maisammaguda, Dhulapally (Post Via. Kompally), Secunderabad – 500100, Telangana State, India Unit -1 IC Technologies, MOS & Bi CMOS Circuits Unit -1 IC Technologies, MOS & Bi CMOS Circuits UNIT-I IC Technologies Introduction Basic Electrical Properties of MOS and BiCMOS Circuits MOS I - V relationships DS DS PMOS MOS transistor Threshold Voltage - VT figure of NMOS merit-ω0 Transconductance-g , g ; CMOS m ds Pass transistor & NMOS Inverter, Various BiCMOS pull ups, CMOS Inverter Technologies analysis and design Bi-CMOS Inverters Unit -1 IC Technologies, MOS & Bi CMOS Circuits INTRODUCTION TO IC TECHNOLOGY The development of electronics endless with invention of vaccum tubes and associated electronic circuits. This activity termed as vaccum tube electronics, afterward the evolution of solid state devices and consequent development of integrated circuits are responsible for the present status of communication, computing and instrumentation. • The first vaccum tube diode was invented by john ambrase Fleming in 1904. • The vaccum triode was invented by lee de forest in 1906. Early developments of the Integrated Circuit (IC) go back to 1949. German engineer Werner Jacobi filed a patent for an IC like semiconductor amplifying device showing five transistors on a common substrate in a 2-stage amplifier arrangement. -

First-Order Circuits

CHAPTER SIX FIRST-ORDER CIRCUITS Chapters 2 to 5 have been devoted exclusively to circuits made of resistors and independent sources. The resistors may contain two or more terminals and may be linear or nonlinear, time-varying or time-invariant. We have shown that these resistive circuits are always governed by algebraic equations. In this chapter, we introduce two new circuit elements, namely, two- terminal capacitors and inductors. We will see that these elements differ from resistors in a fundamental way: They are lossless, and therefore energy is not dissipated but merely stored in these elements. A circuit is said to be dynamic if it includes some capacitor(s) or some inductor(s) or both. In general, dynamic circuits are governed by differential equations. In this initial chapter on dynamic circuits, we consider the simplest subclass described by only one first-order differential equation-hence the name first-order circuits. They include all circuits containing one 2-terminal capacitor (or inductor), plus resistors and independent sources. The important concepts of initial state, equilibrium state, and time constant allow us to find the solution of any first-order linear time-invariant circuit driven by dc sources by inspection (Sec. 3.1). Students should master this material before plunging into the following sections where the inspection method is extended to include linear switching circuits in Sec. 4 and piecewise- linear circuits in Sec. 5. Here,-the important concept of a dynamic route plays a crucial role in the analysis of piecewise-linear circuits by inspection. l TWO-TERMINAL CAPACITORS AND INDUCTORS Many devices cannot be modeled accurately using only resistors. -

Basic Electrical Engineering

BASIC ELECTRICAL ENGINEERING V.HimaBindu V.V.S Madhuri Chandrashekar.D GOKARAJU RANGARAJU INSTITUTE OF ENGINEERING AND TECHNOLOGY (Autonomous) Index: 1. Syllabus……………………………………………….……….. .1 2. Ohm’s Law………………………………………….…………..3 3. KVL,KCL…………………………………………….……….. .4 4. Nodes,Branches& Loops…………………….……….………. 5 5. Series elements & Voltage Division………..………….……….6 6. Parallel elements & Current Division……………….………...7 7. Star-Delta transformation…………………………….………..8 8. Independent Sources …………………………………..……….9 9. Dependent sources……………………………………………12 10. Source Transformation:…………………………………….…13 11. Review of Complex Number…………………………………..16 12. Phasor Representation:………………….…………………….19 13. Phasor Relationship with a pure resistance……………..……23 14. Phasor Relationship with a pure inductance………………....24 15. Phasor Relationship with a pure capacitance………..……….25 16. Series and Parallel combinations of Inductors………….……30 17. Series and parallel connection of capacitors……………...…..32 18. Mesh Analysis…………………………………………………..34 19. Nodal Analysis……………………………………………….…37 20. Average, RMS values……………….……………………….....43 21. R-L Series Circuit……………………………………………...47 22. R-C Series circuit……………………………………………....50 23. R-L-C Series circuit…………………………………………....53 24. Real, reactive & Apparent Power…………………………….56 25. Power triangle……………………………………………….....61 26. Series Resonance……………………………………………….66 27. Parallel Resonance……………………………………………..69 28. Thevenin’s Theorem…………………………………………...72 29. Norton’s Theorem……………………………………………...75 30. Superposition Theorem………………………………………..79 31. -

MOS Caps II; Mosfets I

6.012 - Microelectronic Devices and Circuits Lecture 10 - MOS Caps II; MOSFETs I - Outline G cS vGS + SiO2 – • Review - MOS Capacitor (= vGB) The "Delta-Depletion Approximation" n+ (n-MOS example) p-Si Flat-band voltage: VFB ≡ vGB such that φ(0) = φp-Si: VFB = φp-Si – φm Threshold voltage: VT ≡ vGB such B 1/2 * that φ(0) = – φp-Si: VT = VFB – 2φp-Si + [2εSi qNA|2φp-Si| ] /Cox * * Inversion layer sheet charge density: qN = – Cox [vGC – VT] • Charge stores - qG(vGB) from below VFB to above VT Gate Charge: qG(vGB) from below VFB to above VT Gate Capacitance: Cgb(VGB) Sub-threshold charge: qN(vGB) below VT • 3-Terminal MOS Capacitors - Bias between B and C Impact is on VT(vBC): |2φp-Si| → (|2φp-Si| - vBC) • MOS Field Effect Transistors - Basics of model Gradual Channel Model: electrostatics problem normal to channel drift problem in the plane of the channel Clif Fonstad, 10/15/09 Lecture 10 - Slide 1 G CS vGS + SiO2 – (= vGB) The n-MOS capacitor n+ Right: Basic device p-Si with vBC = 0 B Below: One-dimensional structure for depletion approximation analysis* vGB + – SiO 2 p-Si G B x -tox 0 * Note: We can't forget the n+ region is there; we Clif Fonstad, 10/15/09 will need electrons, and they will come from there. Lecture 10 - Slide 2 MOS Capacitors: Where do the electrons in the inversion layer come from? Diffusion from the p-type substrate? If we relied on diffusion of minority carrier electrons from the p-type substrate it would take a long time to build up the inversion layer charge. -

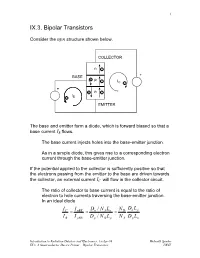

IX.3. a Semiconductor Device Primer – Bipolar Transistors LBNL 2

1 IX.3. Bipolar Transistors Consider the npn structure shown below. COLLECTOR n- BASE + +p -IC- + +n- I -B EMITTER The base and emitter form a diode, which is forward biased so that a base current IB flows. The base current injects holes into the base-emitter junction. As in a simple diode, this gives rise to a corresponding electron current through the base-emitter junction. If the potential applied to the collector is sufficiently positive so that the electrons passing from the emitter to the base are driven towards the collector, an external current IC will flow in the collector circuit. The ratio of collector to base current is equal to the ratio of electron to hole currents traversing the base-emitter junction. In an ideal diode IC I nBE Dn / N ALn N D Dn Lp = = = I B I pBE Dp / N D Lp N A Dp Ln Introduction to Radiation Detctors and Electronics, 13-Apr-99 Helmuth Spieler IX.3. A Semiconductor Device Primer – Bipolar Transistors LBNL 2 If the ratio of doping concentrations in the emitter and base regions ND /NA is sufficiently large, the collector current will be greater than the base current. ⇒ DC current gain Furthermore, we expect the collector current to saturate when the collector voltage becomes large enough to capture all of the minority carrier electrons injected into the base. Since the current inside the transistor comprises both electrons and holes, the device is called a bipolar transistor. Dimensions and doping levels of a modern high-frequency transistor (5 – 10 GHz bandwidth) 0 0.5 1.0 1.5 Distance [µm] (adapted from Sze) Introduction to Radiation Detctors and Electronics, 13-Apr-99 Helmuth Spieler IX.3. -

Laboratory Exercise 2 DC Characteristics of Bipolar Junction

DEPARTMENT OF SEMICONDUCTOR AND OPTOELECTRONIC DEVICES Semiconductor Device Laboratory Laboratory Exercise 2 DC characteristics of Bipolar Junction Transistors (BJT) The aim of the exercise The main aim of this laboratory exercise is to understand principles of operation of Bipolar Junction Transistors (BJT). It covers the measurements of static and small signal parameters. Backgrounds Physical structure of the BJT BJT is a semiconductor device having a three-layer structure with three external electrodes, the emitter (E), the base (B), and the collector (C). As shown in Fig. 1, the structure may be p-n-p or n-p-n type. Despite of the transistor type the emitter layer has always more acceptor or donor impurities added than the base or the collector layer. This asymmetry results from different roles the emitter and the collector layers play in the BJT. In normal operation of the BJT (as an amplifier), the base-emitter junction is forward biased and the base-collector junction is reverse biased. Transistor amplification is controlled by changing the current flow through the base-emitter junction. C N C . C P C . P B. N B. B . B . E . N . E P . E E (a) (b) Fig. 1. The n-p-n BJT (a) and the p-n-p BJT (b) along with their symbols There are three operating configurations of the BJT. These are the common-emitter (OE) configuration, the common-base configuration (OB), and the common-collector (OC) configuration. These configurations are shown in Fig. 2. (a) (b) (c) Fig. 2 The n-p-n transistor operating configurations: (a) common-emitter, (b) common-base, (c) common-collector DC characteristics Four types of characteristics can be defined for each of the transistor operating configurations. -

Chapter 2: Kirchhoff Law and the Thvenin Theorem

Chapter 3: Capacitors, Inductors, and Complex Impedance Chapter 3: Capacitors, Inductors, and Complex Impedance In this chapter we introduce the concept of complex resistance, or impedance, by studying two reactive circuit elements, the capacitor and the inductor. We will study capacitors and inductors using differential equations and Fourier analysis and from these derive their impedance. Capacitors and inductors are used primarily in circuits involving time-dependent voltages and currents, such as AC circuits. I. AC Voltages and circuits Most electronic circuits involve time-dependent voltages and currents. An important class of time-dependent signal is the sinusoidal voltage (or current), also known as an AC signal (Alternating Current). Kirchhoff’s laws and Ohm’s law still apply (they always apply), but one must be careful to differentiate between time-averaged and instantaneous quantities. An AC voltage (or signal) is of the form: V(t) =Vp cos(ωt) (3.1) where ω is the angular frequency, Vp is the amplitude of the waveform or the peak voltage and t is the time. The angular frequency is related to the freguency (f) by ω=2πf and the period (T) is related to the frequency by T=1/f. Other useful voltages are also commonly defined. They include the peak-to-peak voltage (Vpp) which is twice the amplitude and the RMS voltage (VRMS) which is VVRMS = p / 2 . Average power in a resistive AC device is computed using RMS quantities: P=IRMSVRMS = IpVp/2. (3.2) This is important enough that voltmeters and ammeters in AC mode actually return the RMS values for current and voltage. -

Photovoltaic Couplers for MOSFET Drive for Relays

Photocoupler Application Notes Basic Electrical Characteristics and Application Circuit Design of Photovoltaic Couplers for MOSFET Drive for Relays Outline: Photovoltaic-output photocouplers(photovoltaic couplers), which incorporate a photodiode array as an output device, are commonly used in combination with a discrete MOSFET(s) to form a semiconductor relay. This application note discusses the electrical characteristics and application circuits of photovoltaic-output photocouplers. ©2019 1 Rev. 1.0 2019-04-25 Toshiba Electronic Devices & Storage Corporation Photocoupler Application Notes Table of Contents 1. What is a photovoltaic-output photocoupler? ............................................................ 3 1.1 Structure of a photovoltaic-output photocoupler .................................................... 3 1.2 Principle of operation of a photovoltaic-output photocoupler .................................... 3 1.3 Basic usage of photovoltaic-output photocouplers .................................................. 4 1.4 Advantages of PV+MOSFET combinations ............................................................. 5 1.5 Types of photovoltaic-output photocouplers .......................................................... 7 2. Major electrical characteristics and behavior of photovoltaic-output photocouplers ........ 8 2.1 VOC-IF characteristics .......................................................................................... 9 2.2 VOC-Ta characteristic ........................................................................................ -

Fundamentals of MOSFET and IGBT Gate Driver Circuits

Application Report SLUA618A–March 2017–Revised October 2018 Fundamentals of MOSFET and IGBT Gate Driver Circuits Laszlo Balogh ABSTRACT The main purpose of this application report is to demonstrate a systematic approach to design high performance gate drive circuits for high speed switching applications. It is an informative collection of topics offering a “one-stop-shopping” to solve the most common design challenges. Therefore, it should be of interest to power electronics engineers at all levels of experience. The most popular circuit solutions and their performance are analyzed, including the effect of parasitic components, transient and extreme operating conditions. The discussion builds from simple to more complex problems starting with an overview of MOSFET technology and switching operation. Design procedure for ground referenced and high side gate drive circuits, AC coupled and transformer isolated solutions are described in great details. A special section deals with the gate drive requirements of the MOSFETs in synchronous rectifier applications. For more information, see the Overview for MOSFET and IGBT Gate Drivers product page. Several, step-by-step numerical design examples complement the application report. This document is also available in Chinese: MOSFET 和 IGBT 栅极驱动器电路的基本原理 Contents 1 Introduction ................................................................................................................... 2 2 MOSFET Technology ......................................................................................................