Comparative Study of Various Gates Based in Different Technologies

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Episode 5.02 – NAND Logic

Episode 5.02 – NAND Logic Welcome to the Geek Author series on Computer Organization and Design Fundamentals. I’m David Tarnoff, and in this series, we are working our way through the topics of Computer Organization, Computer Architecture, Digital Design, and Embedded System Design. If you’re interested in the inner workings of a computer, then you’re in the right place. The only background you’ll need for this series is an understanding of integer math, and if possible, a little experience with a programming language such as Java. And one more thing. Our topics involve a bit of figuring, so it might help to keep a pencil and paper handy. In our last episode, we covered three attributes of the sum-of-product expression including its general format and the benefits derived from it, a method to generate a truth table from a given sum-of- products expression, and lastly, a simple procedure we can use to create the proper sum-of-products expression from a given truth table. In this episode, we’re going to look at a fourth attribute. While this last trait may appear to be no more than an interesting exercise in Boolean algebra, it turns out that it offers several benefits when we implement our SOP expressions with digital circuitry. In Episode 4.08 – DeMorgan’s Theorem, we showed how an inverter can be distributed across the inputs of an AND or an OR gate by flipping the operation. In other words, we can distribute an inverter from the output of an AND gate across all the gate’s inputs as long as we change the gate operation to an OR. -

Transistors and Logic Gates

Introduction to Computer Engineering CS/ECE 252, Spring 2013 Prof. Mark D. Hill Computer Sciences Department University of Wisconsin – Madison Chapter 3 Digital Logic Structures Slides based on set prepared by Gregory T. Byrd, North Carolina State University Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or display. Transistor: Building Block of Computers Microprocessors contain millions of transistors • Intel Pentium II: 7 million • Compaq Alpha 21264: 15 million • Intel Pentium III: 28 million Logically, each transistor acts as a switch Combined to implement logic functions • AND, OR, NOT Combined to build higher-level structures • Adder, multiplexer, decoder, register, … Combined to build processor • LC-3 3-3 Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or display. Simple Switch Circuit Switch open: • No current through circuit • Light is off • Vout is +2.9V Switch closed: • Short circuit across switch • Current flows • Light is on • Vout is 0V Switch-based circuits can easily represent two states: on/off, open/closed, voltage/no voltage. 3-4 Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or display. N-type MOS Transistor MOS = Metal Oxide Semiconductor • two types: N-type and P-type N-type • when Gate has positive voltage, short circuit between #1 and #2 (switch closed) • when Gate has zero voltage, open circuit between #1 and #2 Gate = 1 (switch open) Gate = 0 Terminal #2 must be connected to GND (0V). 3-5 Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or display. P-type MOS Transistor P-type is complementary to N-type • when Gate has positive voltage, open circuit between #1 and #2 (switch open) • when Gate has zero voltage, short circuit between #1 and #2 (switch closed) Gate = 1 Gate = 0 Terminal #1 must be connected to +2.9V. -

ECSE-4760 Real-Time Applications in Control & Communications

Rensselaer Polytechnic Institute ECSE-4760 Real-Time Applications in Control & Communications EXPERIMENTS IN DIGITAL LOGIC DESIGN Number of Sessions – 4 INTRODUCTION Over the past few decades the digital world has come into its own. Even though engineering has gone into specialization, it is necessary to understand digital circuits to be able to communicate with others. This experiment attempts to teach a simple method of designing digital circuits. Due to the quick pace of the lab, it is highly recommended that you read one of the references. This will enable you to proceed quickly through the preliminary problems so you will have more time for the design problems. The following is an outline of the experiment. Following each section will be a set of questions that should be answered to show an understanding of the material presented. Any difficulties should be referred to a reference or your instructor. You should use the DesignWorks (LogicWorks or any other you may have) logic circuit simulator on the Macintosh after most sections to cement together all the preceding sections. BACKGROUND THEORY Boolean Algebra Switching Algebra Combinational Logic Minimization Flip-Flops and Registers Counters Synthesis of Synchronous Circuits EXPERIMENTAL PROCEDURE Questions and Problems Simulator Operation & FPGA Implementation REFERENCES It is required that you show all circuits, as built, in your write-up. Please include equations too. The first part of the procedure section contains all the questions and problems to be answered and the second part describes the use of DesignWorks. Note: all references to DesignWorks (on Macintosh computers) throughout this procedure may be replaced with LogicWorks on the lab Windows PCs. -

Digital Logic Design

Digital Logic Design Chapter 3 Gate-Level Minimization Nasser M. Sabah Outline of Chapter 3 2 Introduction The Map Method Four-Variable Map Five-Variable Map Product of Sums Simplification NAND & NOR Implementation Other Two-Level Implementations Exclusive-OR Function Introduction 3 Gate-level minimization refers to the design task of finding an optimal gate-level implementation of Boolean functions describing a digital circuit. The Map Method 4 The complexity of the digital logic gates The complexity of the algebraic expression Logic minimization Algebraic approaches: lack specific rules The Karnaugh map A simple straight forward procedure A pictorial form of a truth table A diagram made up of squares Each square represents one minterm of the function that is to be minimized. Review of Boolean Function 5 Boolean function Sum of minterms Sum of products (or product of sum) in the simplest form A minimum number of terms A minimum number of literals The simplified expression may not be unique Two-Variable Map 6 A two-variable map Four minterms x' = row 0; x = row 1 y' = column 0; y = column 1 A truth table in square diagram Figure 3.1 Two-variable Map xy m3 xym 1 m 2 m 3 xyxy'' xy Representation of functions in the map Three-Variable Map 7 A three-variable map Eight minterms The Gray code sequence Any two adjacent squares in the map differ by only on variable. Primed in one square and unprimed in the other. e.g., m5 and m7 can be simplified. m57 m xy'(') z xyz xz y y xz Three-variable Map Three-Variable -

Lab 1: Study of Gates & Flip-Flops

Lab 1: Study of Gates & Flip-flops Aim To familiarize with circuit implementations using ICs and test the behavior of different logic gates and Flip-flops. Hardware Requirement a. Equipments - Digital IC Trainer Kit b. Discrete Components - 74LS00 Quad 2-Input NAND gate 74LS02 Quad 2-Input NOR gate 74LS04 Hex 1-Input NOT gate 74LS08 Quad 2-Input AND gate 74LS10 Triple 3-Input NAND gate 74LS11 Triple 3-Input AND gate 74LS32 Quad 2-Input OR gate 74LS86 Quad 2-Input XOR 74LS73 JK-Flip flop 74LS74 D Flip flop Background Digital logic devices are the circuits that electronically perform logic operations on binary variables. The binary information is represented by high and low voltage levels, which the device processes electronically. The devices that perform the simplest of the logic operations (such as AND, OR, NAND, etc.) are called gates. For example, an AND gate electronically computes the AND of the voltage encoded binary signals appearing at its inputs and presents the voltage encoded result at its output. The digital logic circuits used in this laboratory are contained in integrated circuit (IC) packages, with generally 14 or 16 pins for electrical connections. Each IC is labeled (usually with an 74LSxx number) to identify the logic it performs. The logic diagrams and pin connections for these IC’s are described in the TTL Data Book by Texas Instruments1. The transistor-transistor logic(TTL) IC’s used in this laboratory require a 5.0 volt power supply for operation. TTL inputs require a voltage greater than 2 volts to represent a binary 1 and a voltage less than 0.8 volts to represent a binary 0. -

Realization of Morphing Logic Gates in a Repressilator with Quorum Sensing Feedback

Realization of Morphing Logic Gates in a Repressilator with Quorum Sensing Feedback Vidit Agarwal, Shivpal Singh Kang and Sudeshna Sinha Indian Institute of Science Education and Research (IISER) Mohali, Knowledge City, SAS Nagar, Sector 81, Manauli PO 140 306, Punjab, India Abstract We demonstrate how a genetic ring oscillator network with quorum sensing feedback can operate as a robust logic gate. Specifically we show how a range of logic functions, namely AND/NAND, OR/NOR and XOR/XNOR, can be realized by the system, thus yielding a versatile unit that can morph between different logic operations. We further demonstrate the capacity of this system to yield complementary logic operations in parallel. Our results then indicate the computing potential of this biological system, and may lead to bio-inspired computing devices. arXiv:1310.8267v1 [physics.bio-ph] 30 Oct 2013 1 I. INTRODUCTION The operation of any computing device is necessarily a physical process, and this funda- mentally determines the possibilities and limitations of the computing machine. A common thread in the history of computers is the exploitation and manipulation of different natural phenomena to obtain newer forms of computing paradigms [1]. For instance, chaos comput- ing [2], neurobiologically inspired computing, quantum computing[3], and DNA computing[4] all aim to utilize, at the basic level, some of the computational capabilities inherent in natural systems. In particular, larger understanding of biological systems has triggered the interest- ing question: what new directions do bio-systems offer for understanding and implementing computations? The broad idea then, is to create machines that benefit from natural phenomena and utilize patterns inherent in systems to encode inputs and subsequently obtain a desired output. -

Universal Gate - NOR Digital Electronics 2.2 Intro to NAND & NOR Logic

Universal Gate - NOR Digital Electronics 2.2 Intro to NAND & NOR Logic Universal Gate – NOR This presentation will demonstrate… • The basic function of the NOR gate. • How an NOR gate can be using to replace an AND gate, an OR gate or an INVERTER gate. • How a logic circuit implemented with AOI logic gates Universal Gate – NOR could be re-implemented using only NOR gates • That using a single gate type, in this case NOR, will reduce the number of integrated circuits (IC) required to implement a logic circuit. Digital Electronics AOI Logic NOR Logic 2 More ICs = More $$ Less ICs = Less $$ NOR Gate NOR Gate as an Inverter Gate X X X (Before Bubble) X Z X Y X Y X Z X Y X Y Z X Z 0 0 1 0 1 Equivalent to Inverter 0 1 0 1 0 1 0 0 1 1 0 3 4 Project Lead The Way, Inc. Copyright 2009 1 Universal Gate - NOR Digital Electronics 2.2 Intro to NAND & NOR Logic NOR Gate as an OR Gate NOR Gate as an AND Gate X X Y Y X X Z X Y X Y Y Z X Y X Y X Y Y NOR Gate “Inverter” “Inverters” NOR Gate X Y Z X Y Z 0 0 0 0 0 0 0 1 1 0 1 0 Equivalent to OR Gate Equivalent to AND Gate 1 0 1 1 0 0 1 1 1 1 1 1 5 6 NOR Gate Equivalent of AOI Gates Process for NOR Implementation 1. -

Universal Gate - NAND Digital Electronics 2.2 Intro to NAND & NOR Logic

Universal Gate - NAND Digital Electronics 2.2 Intro to NAND & NOR Logic Universal Gate – NAND This presentation will demonstrate • The basic function of the NAND gate. • How a NAND gate can be used to replace an AND gate, an OR gate, or an INVERTER gate. • How a logic circuit implemented with AOI logic gates can Universal Gate – NAND be re-implemented using only NAND gates. • That using a single gate type, in this case NAND, will reduce the number of integrated circuits (IC) required to implement a logic circuit. Digital Electronics AOI Logic NAND Logic 2 More ICs = More $$ Less ICs = Less $$ NAND Gate NAND Gate as an Inverter Gate X X X (Before Bubble) X Z X Y X Y X Z X Y X Y Z X Z 0 0 1 0 1 Equivalent to Inverter 0 1 1 1 0 1 0 1 1 1 0 3 4 Project Lead The Way, Inc Copyright 2009 1 Universal Gate - NAND Digital Electronics 2.2 Intro to NAND & NOR Logic NAND Gate as an AND Gate NAND Gate as an OR Gate X X Y Y X X Z X Y X Y Y Z X Y X Y X Y Y NAND Gate Inverter Inverters NAND Gate X Y Z X Y Z 0 0 0 0 0 0 0 1 0 0 1 1 Equivalent to AND Gate Equivalent to OR Gate 1 0 0 1 0 1 1 1 1 1 1 1 5 6 NAND Gate Equivalent to AOI Gates Process for NAND Implementation 1. -

New Approaches for Memristive Logic Computations

Portland State University PDXScholar Dissertations and Theses Dissertations and Theses 6-6-2018 New Approaches for Memristive Logic Computations Muayad Jaafar Aljafar Portland State University Let us know how access to this document benefits ouy . Follow this and additional works at: https://pdxscholar.library.pdx.edu/open_access_etds Part of the Electrical and Computer Engineering Commons Recommended Citation Aljafar, Muayad Jaafar, "New Approaches for Memristive Logic Computations" (2018). Dissertations and Theses. Paper 4372. 10.15760/etd.6256 This Dissertation is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. For more information, please contact [email protected]. New Approaches for Memristive Logic Computations by Muayad Jaafar Aljafar A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering Dissertation Committee: Marek A. Perkowski, Chair John M. Acken Xiaoyu Song Steven Bleiler Portland State University 2018 © 2018 Muayad Jaafar Aljafar Abstract Over the past five decades, exponential advances in device integration in microelectronics for memory and computation applications have been observed. These advances are closely related to miniaturization in integrated circuit technologies. However, this miniaturization is reaching the physical limit (i.e., the end of Moore’s Law). This miniaturization is also causing a dramatic problem of heat dissipation in integrated circuits. Additionally, approaching the physical limit of semiconductor devices in fabrication process increases the delay of moving data between computing and memory units hence decreasing the performance. The market requirements for faster computers with lower power consumption can be addressed by new emerging technologies such as memristors. -

EE 434 Lecture 2

EE 330 Lecture 6 • PU and PD Networks • Complex Logic Gates • Pass Transistor Logic • Improved Switch-Level Model • Propagation Delay Review from Last Time MOS Transistor Qualitative Discussion of n-channel Operation Source Gate Drain Drain Bulk Gate n-channel MOSFET Source Equivalent Circuit for n-channel MOSFET D D • Source assumed connected to (or close to) ground • VGS=0 denoted as Boolean gate voltage G=0 G = 0 G = 1 • VGS=VDD denoted as Boolean gate voltage G=1 • Boolean G is relative to ground potential S S This is the first model we have for the n-channel MOSFET ! Ideal switch-level model Review from Last Time MOS Transistor Qualitative Discussion of p-channel Operation Source Gate Drain Drain Bulk Gate Source p-channel MOSFET Equivalent Circuit for p-channel MOSFET D D • Source assumed connected to (or close to) positive G = 0 G = 1 VDD • VGS=0 denoted as Boolean gate voltage G=1 • VGS= -VDD denoted as Boolean gate voltage G=0 S S • Boolean G is relative to ground potential This is the first model we have for the p-channel MOSFET ! Review from Last Time Logic Circuits VDD Truth Table A B A B 0 1 1 0 Inverter Review from Last Time Logic Circuits VDD Truth Table A B C 0 0 1 0 1 0 A C 1 0 0 B 1 1 0 NOR Gate Review from Last Time Logic Circuits VDD Truth Table A B C A C 0 0 1 B 0 1 1 1 0 1 1 1 0 NAND Gate Logic Circuits Approach can be extended to arbitrary number of inputs n-input NOR n-input NAND gate gate VDD VDD A1 A1 A2 An A2 F A1 An F A2 A1 A2 An An A1 A 1 A2 F A2 F An An Complete Logic Family Family of n-input NOR gates forms -

Digital IC Listing

BELS Digital IC Report Package BELS Unit PartName Type Location ID # Price Type CMOS 74HC00, Quad 2-Input NAND Gate DIP-14 3 - A 500 0.24 74HCT00, Quad 2-Input NAND Gate DIP-14 3 - A 501 0.36 74HC02, Quad 2 Input NOR DIP-14 3 - A 417 0.24 74HC04, Hex Inverter, buffered DIP-14 3 - A 418 0.24 74HC04, Hex Inverter (buffered) DIP-14 3 - A 511 0.24 74HCT04, Hex Inverter (Open Collector) DIP-14 3 - A 512 0.36 74HC08, Quad 2 Input AND Gate DIP-14 3 - A 408 0.24 74HC10, Triple 3-Input NAND DIP-14 3 - A 419 0.31 74HC32, Quad OR DIP-14 3 - B 409 0.24 74HC32, Quad 2-Input OR Gates DIP-14 3 - B 543 0.24 74HC138, 3-line to 8-line decoder / demultiplexer DIP-16 3 - C 603 1.05 74HCT139, Dual 2-line to 4-line decoders / demultiplexers DIP-16 3 - C 605 0.86 74HC154, 4-16 line decoder/demulitplexer, 0.3 wide DIP - Small none 445 1.49 74HC154W, 4-16 line decoder/demultiplexer, 0.6wide DIP none 446 1.86 74HC190, Synchronous 4-Bit Up/Down Decade and Binary Counters DIP-16 3 - D 637 74HCT240, Octal Buffers and Line Drivers w/ 3-State outputs DIP-20 3 - D 643 1.04 74HC244, Octal Buffers And Line Drivers w/ 3-State outputs DIP-20 3 - D 647 1.43 74HCT245, Octal Bus Transceivers w/ 3-State outputs DIP-20 3 - D 649 1.13 74HCT273, Octal D-Type Flip-Flops w/ Clear DIP-20 3 - D 658 1.35 74HCT373, Octal Transparent D-Type Latches w/ 3-State outputs DIP-20 3 - E 666 1.35 74HCT377, Octal D-Type Flip-Flops w/ Clock Enable DIP-20 3 - E 669 1.50 74HCT573, Octal Transparent D-Type Latches w/ 3-State outputs DIP-20 3 - E 674 0.88 Type CMOS CD4000 Series CD4001, Quad 2-input -

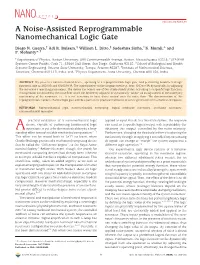

A Noise-Assisted Reprogrammable Nanomechanical Logic Gate

pubs.acs.org/NanoLett A Noise-Assisted Reprogrammable Nanomechanical Logic Gate Diego N. Guerra,† Adi R. Bulsara,‡ William L. Ditto,§ Sudeshna Sinha,| K. Murali,⊥ and P. Mohanty*,† † Department of Physics, Boston University, 590 Commonwealth Avenue, Boston, Massachusetts 02215, ‡ SPAWAR Systems Center Pacific, Code 71, 53560 Hull Street, San Diego, California 92152, § School of Biological and Health Systems Engineering, Arizona State University, Tempe, Arizona 85287, | Institute of Mathematical Sciences, Taramani, Chennai 600 113, India, and ⊥ Physics Department, Anna University, Chennai 600 025, India ABSTRACT We present a nanomechanical device, operating as a reprogrammable logic gate, and performing fundamental logic functions such as AND/OR and NAND/NOR. The logic function can be programmed (e.g., from AND to OR) dynamically, by adjusting the resonator’s operating parameters. The device can access one of two stable steady states, according to a specific logic function; this operation is mediated by the noise floor which can be directly adjusted, or dynamically “tuned” via an adjustment of the underlying nonlinearity of the resonator, i.e., it is not necessary to have direct control over the noise floor. The demonstration of this reprogrammable nanomechanical logic gate affords a path to the practical realization of a new generation of mechanical computers. KEYWORDS Nanomechanical logic, nanomechanical computing, logical stochastic resonance, stochastic resonance, nanomechanical resonator practical realization of a nanomechanical logic applied as input stimuli to a two-state system, the response device, capable of performing fundamental logic can result in a specific logical output with a probability (for operations, is yet to be demonstrated despite a long- obtaining this output) controlled by the noise intensity.