Exploring the Ultimate Limits of Adiabatic Circuits

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

By Erika Azabache Villar a Thesis Submitted in Partial Fulfillment of The

SMALLER/FASTER DELTA-SIGMA DIGITAL PIXEL SENSORS by Erika Azabache Villar A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Integrated Circuits and Systems Department of Electrical and Computer Engineering University of Alberta c Erika Azabache Villar, 2016 Abstract A digital pixel sensor (DPS) array is an image sensor where each pixel has an analog-to-digital converter (ADC). Recently, a logarithmic delta-sigma (ΔΣ) DPS array, using first-order ΔΣ ADCs, achieved wide dynamic range and high signal-to-noise-and-distortion ratios at video rates, requirements that are difficult to meet using conventional image sensors. However, this state-of-the-art ΔΣ DPS design is either too large for some applications, such as optical imag- ing, or too slow for others, such as gamma imaging. Consequently, this master’s thesis investi- gates smaller or faster ΔΣ DPS designs, relative to the state of the art. All designs are validated through simulations. Commercial image sensors, for optical and gamma imaging, are used as targeted baselines to establish competitive specifications. To achieve a smaller pixel, process scaling is exploited. Three logarithmic ΔΣ DPS designs are presented for 180, 130, and 65 nm fabrication processes, demonstrating a path to competitiveness for the optical imaging market. Decimator and readout circuits are improved, compared to previous work, while reducing area, and capacitors in the modulator prove to be the limiting factor in deep-submicron processes. Area trends are used to construct a roadmap to even smaller pixels. To achieve a faster pixel, a higher-order ΔΣ architecture is exploited. -

An Area Efficient Sub-Threshold Voltage Level Shifter Using a Modified Wilson Current Mirror for Low Power Applications

An Area Efficient Sub-threshold Voltage Level Shifter using a Modified Wilson Current Mirror for Low Power Applications Biswarup Mukherjee & Aniruddha Ghosal Published online: 22 May 2019. Submit your article to this journal Article views: 12 View Crossmark data An Area Efficient Sub-threshold Voltage Level Shifter using a Modified Wilson Current Mirror for Low Power Applications Biswarup Mukherjee1 and Aniruddha Ghosal2 1Neotia Institute of Technology, Management and Science, Jhinga, Diamond Harbour Road, 24Pgs. (S), West Bengal, India; 2Institute of Radio Physics and Electronics, University of Calcutta, West Bengal, India ABSTRACT KEYWORDS In the present communication, a new technique has been introduced for implementing low-power Current mirror; CAD area efficient sub-threshold voltage level shifter (LS) circuit. The proposed LS circuit consists of only simulation; Level shifter (LS); nine transistors and can operate up to 100 MHz of input frequency successfully. The proposed LS Low power; Sub-threshold is made of single threshold voltage transistors which show least complexity in fabrication and bet- operation; Typical transistor (TT) ter performance in terms of delay analysis and power consumption compared to other available designs. CAD tool-based simulation at TSMC 180 nm technology and comparison between the pro- posed design and other available designs show that the proposed design performs better than other state-of-the-art designs for a similar range of voltage conversion with the most area efficiency. 1. INTRODUCTION are used to reduce the circuit activity or the capacitance value in order to reduce the switching power consump- With the increasing demand of portable devices in elec- tion. -

Overview of CMOS Sensors for Future Tracking Detectors

instruments Review Overview of CMOS Sensors for Future Tracking Detectors Ricardo Marco-Hernández Instituto de Física Corpuscular (CSIC-UV), 46980 Valencia, Spain; rmarco@ific.uv.es Received: 23 October 2020; Accepted: 27 November 2020; Published: 30 November 2020 Abstract: Depleted Complementary Metal-Oxide-Semiconductor (CMOS) sensors are emerging as one of the main candidate technologies for future tracking detectors in high luminosity colliders. Their capability of integrating the sensing diode into the CMOS wafer hosting the front-end electronics allows for reduced noise and higher signal sensitivity, due to the direct collection of the sensor signal by the readout electronics. They are suitable for high radiation environments due to the possibility of applying high depletion voltage and the availability of relatively high resistivity substrates. The use of a CMOS commercial fabrication process leads to their cost reduction and allows faster construction of large area detectors. In this contribution, a general perspective of the state of the art of CMOS detectors for High Energy Physics experiments is given. The main developments carried out with regard to these devices in the framework of the CERN RD50 collaboration are summarized. Keywords: DMAPS; CMOS; radiation sensors; electronics 1. Introduction Current large pixel detectors in High Energy Physics, such as the ones which will be part of the A Toroidal LHC (Large Hadron Collider) ApparatuS (ATLAS) Tracker Detector [1] or the Compact Muon Solenoid (CMS) Tracker Detector [2] upgrades for the High-Luminosity Large Hadron Collider (HL-LHC), mostly follow a hybrid approach. In a hybrid pixel detector the sensor and the readout electronics are independent devices connected by means of bump-bonding, as can be seen in Figure1. -

A Area VLSI Design (SCL)

A Area VLSI Design (SCL) A1 Sub Area ASIC Design (SCL) A1.1 Design of Instrumentation Amplifier A High-Precision Instrumentation Amplifier with large CMRR is required for the Sensor Signal conditioning applications. Instrumentation amplifier is a versatile device used for amplification of small differential mode signals while rejecting large common mode signal at the same time. In a typical signal conditioning chain, the output of the sensor goes to the instrumentation amplifier. The instrumentation amplifier amplifies the small output signal of the sensor and gives it to the ADC for digitization. Target Specification: • Supply Voltage: 3.3V • Temperature Range: -40 degC to 125 degC • Programmable Gain: 1 to 1000 • Low noise < 0.3µV p-p at 0.1 Hz to 10 Hz • Low non linearity < 20ppm (Gain = 1) • High CMRR (Common Mode Rejection Ratio) > 90dB (Gain=1) • Low offset voltage < 100µV • 3 dB Bandwidth: 1MHz (at Gain = 1) The design of the proposed Instrumentation Amplifier is to be carried out in SCL 180 nm process. A1.2 Design of a Current Feedback Amplifier (CFA) Opamps come in two types: the voltage-feedback amplifier (VFA), for which the input error is a voltage; and the current-feedback amplifier (CFA), for which the input error is a current. The CFA noninverting amplifier is relatively free from a gain-bandwidth trade-off. Additional advantage of CFAs compared to VFAs is the absence of slew-rate limiting. CFA is primarily used where both high speed and low distortion signal processing is required. CFAs are mainly used in broadcast video systems, radar systems , IF and RF stages and other high speed circuits. -

Progress in Particle Tracking and Vertexing Detectors Nicolas Fourches

Progress in particle tracking and vertexing detectors Nicolas Fourches (CEA/IRFU): 22nd March 2020, University Paris-Saclay Abstract: This is part of a document, which is devoted to the developments of pixel detectors in the context of the International Linear Collider. From the early developments of the MIMOSAs to the proposed DotPix I recall some of the major progresses. The need for very precise vertex reconstruction is the reason for the Research and Development of new pixel detectors, first derived from the CMOS sensors and in further steps with new semiconductors structures. The problem of radiation effects was investigated and this is the case for the noise level with emphasis of the benefits of downscaling. Specific semiconductor processing and characterisation techniques are also described, with the perspective of a new pixel structure. TABLE OF CONTENTS: 1. The trend towards 1-micron point-to-point resolution and below 1.1. Gaseous detectors : 1.2. Liquid based detectors : 1.3. Solid state detectors : 2. The solution: the monolithically integrated pixel detector: 2.1. Advantages and drawbacks 2.2. Spatial resolution : experimental physics requirements 2.2.1. Detection Physics at colliders 2.2.1.1. Track reconstruction 2.2.1.2. Constraints on detector design a) Multiple interaction points in the incident colliding particle bunches b) Multiple hits in single pixels even in the outer layers c) Large NIEL (Non Ionizing Energy Loss) in the pixels leading to displacement defects in the silicon layers d) Cumulative ionization in the solid state detectors leading to a total dose above 1 MGy in the operating time of the machine a) First reducing the bunch length and beam diameter would significantly limit the number of spurious interaction points. -

EP Activity Report 2015

EUROPRACTICE IC SERVICE THE RIGHT COCKTAIL OF ASIC SERVICES EUROPRACTICE IC SERVICE OFFERS YOU A PROVEN ROUTE TO ASICS THAT FEATURES: · .QYEQUV#5+%RTQVQV[RKPI · (NGZKDNGCEEGUUVQUKNKEQPECRCEKV[HQTUOCNNCPFOGFKWOXQNWOGRTQFWEVKQPSWCPVKVKGU · 2CTVPGTUJKRUYKVJNGCFKPIYQTNFENCUUHQWPFTKGUCUUGODN[CPFVGUVJQWUGU · 9KFGEJQKEGQH+%VGEJPQNQIKGU · &KUVTKDWVKQPCPFHWNNUWRRQTVQHJKIJSWCNKV[EGNNNKDTCTKGUCPFFGUKIPMKVUHQTVJGOQUVRQRWNCT%#&VQQNU · 46.VQ.C[QWVUGTXKEGHQTFGGRUWDOKETQPVGEJPQNQIKGU · (TQPVGPF#5+%FGUKIPVJTQWIJ#NNKCPEG2CTVPGTU +PFWUVT[KUTCRKFN[FKUEQXGTKPIVJGDGPG«VUQHWUKPIVJG'74124#%6+%'+%UGTXKEGVQJGNRDTKPIPGYRTQFWEVFGUKIPUVQOCTMGV SWKEMN[CPFEQUVGHHGEVKXGN[6JG'74124#%6+%'#5+%TQWVGUWRRQTVUGURGEKCNN[VJQUGEQORCPKGUYJQFQP°VPGGFCNYC[UVJG HWNNTCPIGQHUGTXKEGUQTJKIJRTQFWEVKQPXQNWOGU6JQUGEQORCPKGUYKNNICKPHTQOVJG¬GZKDNGCEEGUUVQUKNKEQPRTQVQV[RGCPF RTQFWEVKQPECRCEKV[CVNGCFKPIHQWPFTKGUFGUKIPUGTXKEGUJKIJSWCNKV[UWRRQTVCPFOCPWHCEVWTKPIGZRGTVKUGVJCVKPENWFGU+% OCPWHCEVWTKPIRCEMCIKPICPFVGUV6JKU[QWECPIGVCNNHTQO'74124#%6+%'+%UGTXKEGCUGTXKEGVJCVKUCNTGCF[GUVCDNKUJGF HQT[GCTUKPVJGOCTMGV THE EUROPRACTICE IC SERVICES ARE OFFERED BY THE FOLLOWING CENTERS: · KOGE.GWXGP $GNIKWO · (TCWPJQHGT+PUVKVWVHWGT+PVGITKGTVG5EJCNVWPIGP (TCWPJQHGT++5 'TNCPIGP )GTOCP[ This project has received funding from the European Union’s Seventh Programme for research, technological development and demonstration under grant agreement N° 610018. This funding is exclusively used to support European universities and research laboratories. © imec FOREWORD Dear EUROPRACTICE customers, We are at the start of the -

A Survey of Analog-To-Digital Converters for Operation Under Radiation Environments

electronics Review A Survey of Analog-to-Digital Converters for Operation under Radiation Environments Ernesto Pun-García 1,*,† and Marisa López-Vallejo 2 1 R&D Department, Arquimea Ingeniería SLU, 28918 Leganés, Spain 2 IPTC, ETSI Telecomunicación, Universidad Politécnica de Madrid, 28040 Madrid, Spain; [email protected] * Correspondence: [email protected]; Tel.: +34-610-571-208 † Current address: Calle Margarita Salas 10, 28918 Leganés, Madrid, Spain. Academic Editors: Marko Laketic, Paisley Shi and Anna Li Received: 7 September 2020; Accepted: 3 October 2020; Published: 15 October 2020 Abstract: In this work, we analyze in depth multiple characteristic data of a representative population of radenv-ADCs (analog-to-digital converters able to operate under radiation). Selected ADCs behave without latch-up below 50 MeV·cm2/mg and are able to bear doses of ionizing radiation above 50 krad(Si). An exhaustive search of ADCs with radiation characterization data has been carried out throughout the literature. The obtained collection is analyzed and compared against the state of the art of scientific ADCs, which reached years ago the electrical performance that radenv-ADCs provide nowadays. In fact, for a given Nyquist sampling rate, radenv-ADCs require significantly more power to achieve lower effective resolution. The extracted performance patterns and conclusions from our study aim to serve as reference for new developments towards more efficient implementations. As tools for this purpose, we have conceived FOMTID and FOMSET, two new figures of merit to compare radenv-ADCs that consider electrical and radiation performance. Keywords: ADC performance patterns; ADC state of the art; ADC survey; analog-to-digital converters; applications under radiation environments; figure of merit under radiation; radenv-ADC design guidelines; radiation effects; radiation hardening; radiation test methods 1. -

WP Microelectronics and Interconnections

Advanced European Infrastructures for Detectors at Accelerators FirSecondst Ann Annualual MeMeetingeting: WPWP44 St Statusatus R Reporteport ChrisChristophetophe de LA TA ILdeLE (laCN TailleRS/IN2P(CNRS/IN2P3)3) Valerio RE (INFN ) Valerio Re (INFN/Univ. Bergamo) LPNHE, Paris, April 7, 2017 DESY, Hamburg, June 17, 2016 This project has received funding from the European Union’s Horizon 2020 Research and Innovation programme under Grant Agreement no. 654168. WP4: microelectronics and interconnections • WP Coordinators: Christophe de la Taille, Valerio Re • Goal : provide chips and interconnections to detectors developed by other WPs • Task 1: Scientific coordination (CNRS-OMEGA, INFN-UNIBG) • Task 2 : 65 nm chips for trackers (CERN) • Fine pitch, low power, advanced digital processing • Task 3 : SiGe 130nm for calorimeters/gaseous (IN2P3) • Highly integrated charge and time measurement • Task 4 : interconnections between 65 nm chips and pixel sensors (INFN) • TSVs in 65 nm CMOS wafers, bonding of 65 nm chips to sensors, exploration of fine pitch bonding processes AIDA WP4 milestones MS4.1 Architectural review of deliverable chips in 65nm run M14 (accomplished) MS4.2 Final design review of 65nm M30 (October 2017) MS4.3 Test report of deliverable D4.1 M46 (February 2019) MS4.4 Selection of SiGe foundry M14 (accomplished) MS4.5 Final design review of deliverable chips in SiGe run M30 (October 2017) MS4.6 Test report of deliverable D4.2 M46 MS4.7 Selection of TSV process M14 (accomplished) MS4.8 Final design review of deliverable D4.3 (TSV -

On the Effects of Total Ionizing Dose in Silicon-Germanium Bicmos Platforms

ON THE EFFECTS OF TOTAL IONIZING DOSE IN SILICON-GERMANIUM BICMOS PLATFORMS A Thesis Presented to The Academic Faculty by Zachary E. Fleetwood In Partial Fulfillment of the Requirements for the Degree Master's Thesis in the School of Electrical and Computer Engineering Georgia Institute of Technology December 2014 Copyright c 2014 by Zachary E. Fleetwood ON THE EFFECTS OF TOTAL IONIZING DOSE IN SILICON-GERMANIUM BICMOS PLATFORMS Approved by: Professor John D. Cressler, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology Professor John Papapolymerou School of Electrical Engineering Georgia Institute of Technology Professor Douglas Yoder School of Electrical Engineering Georgia Institute of Technology Date Approved: 5 Dec 2014 ACKNOWLEDGEMENTS I would first like to thank my research advisor Dr. Cressler. His endless support and encouragement has made me a better researcher and has provided me with the perfect environment to continue my education. I would also like to thank the members of my reading committee: Dr. Papapolymerou and Dr. Yoder. I appreciate their taking the time to provide me with helpful feedback on this thesis in addition to being my teachers at Georgia Tech. I would also like to thank my Mom, Dad, and brothers: Aaron and Nathan. Your support and love over the years means everything to me. I would especially like to thank my father for taking the time to help provide me with feedback on my technical work | you have taught me so much. And I would also like to thank all my friends. Thank you to my Vandy friends Dylan McQuaide and Zac Diggins | I don't know where I would be right now without you guys. -

Intel's Atom Lines 1. Introduction to Intel's Atom Lines 3. Atom-Based Platforms Targeting Entry Level Desktops and Notebook

Intel’s Atom lines • 1. Introduction to Intel’s Atom lines • 2. Intel’s low-power oriented CPU micro-architectures • 3. Atom-based platforms targeting entry level desktops and notebooks • 4. Atom-based platforms targeting tablets • 5. Atom-based platforms targeting smartphones • 6. Intel’s withdrawal from the mobile market • 7. References 1. Introduction to Intel’s Atom lines • 1.1 The rapidly increasing importance of the mobile market space • 1.2 Related terminology • 1.3 Introduction to Intel’s low-power Atom series 1.1 The rapidly increasing importance of the mobile market space 1.1 The rapidly increasing importance of the mobile market space (1) 1.1 The rapidly increasing importance of the mobile market space Diversification of computer market segments in the 2000’s Main computer market segments around 2000 Servers Desktops Embedded computer devices E.g. Intel’s Xeon lines Intel’s Pentium 4 lines ARM’s lines AMD’s Opteron lines AMD’s Athlon lines Major trend in the first half of the 2000’s: spreading of mobile devices (laptops) Main computer market segments around 2005 Servers Desktops Mobiles Embedded computer devices E.g. Intel’s Xeon lines Intel’s Pentium 4 lines Intel’s Celeron lines ARM’s lines AMD’s Opteron lines AMD’s Athlon64 lines AMD’s Duron lines 1.1 The rapidly increasing importance of the mobile market space (2) Yearly worldwide sales and Compound Annual Growth Rates (CAGR) of desktops and mobiles (laptops) around 2005 [1] 350 300 Millions 250 CAGR 17% 200 Mobile 150 100 Desktop CAGR 5% 50 0 2003 2004 2005 2006 2007 2008 -

A Case for Packageless Processors

A Case for Packageless Processors Saptadeep Pal∗, Daniel Petrisko†, Adeel A. Bajwa∗, Puneet Gupta∗, Subramanian S. Iyer∗, and Rakesh Kumar† ∗Department of Electrical and Computer Engineering, University of California, Los Angeles †Department of Electrical and Computer Engineering, University of Illinois at Urbana-Champaign fsaptadeep,abajwa,s.s.iyer,[email protected], fpetrisk2,[email protected] Abstract—Demand for increasing performance is far out- significantly limit the number of supportable IOs in the pacing the capability of traditional methods for performance processor due to the large size and pitch of the package- scaling. Disruptive solutions are needed to advance beyond to-board connection relative to the size and pitch of on- incremental improvements. Traditionally, processors reside inside packages to enable PCB-based integration. We argue chip interconnects (∼10X and not scaling well). In addition, that packages reduce the potential memory bandwidth of a the packages significantly increase the interconnect distance processor by at least one order of magnitude, allowable thermal between the processor die and other dies. Eliminating the design power (TDP) by up to 70%, and area efficiency by package, therefore, has the potential to increase bandwidth a factor of 5 to 18. Further, silicon chips have scaled well by at least an order of magnitude(Section II). Similarly, while packages have not. We propose packageless processors - processors where packages have been removed and dies processor packages are much bigger than the processor itself directly mounted on a silicon board using a novel integra- (5 to 18 times bigger). Removing the processor package tion technology, Silicon Interconnection Fabric (Si-IF). -

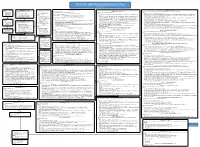

The Intel X86 Microarchitectures Map Version 3.2

The Intel x86 Microarchitectures Map Version 3.2 8086 (1978, 3 µm) 80386 (1985, 1.5 to 1 µm) P6 (1995, 0.50 to 0.35 μm) Skylake (2015, 14 nm) NetBurst (2000 , 180 to 130 nm) Series: Alternative Names: iAPX 386, 386, i386 Alternative Names: i686 Alternative Names: SKL (Desktop and Mobile), SKX (Server) (Note : all U and Y processors are MCPs) P5 (1993, 0.80 to 0.35 μm) Alternative Names: Pentium 4, Pentium IV, P4 • 16-bit data bus: Series: Series: Pentium Pro (used in desktops and servers) Series: Alternative Names: Pentium, Series: 8086 (iAPX 86) • Desktop/Server: i386DX Variant: Klamath (1997, 0.35 μm) • Desktop: Desktop 6th Generation Core i5 (i5-6xxx, S-H) 80586, 586, i586 • Desktop: Pentium 4 1.x (except those with a suffix, Willamette, 180 nm), Pentium 4 2.0 (Willamette, 180 • 8-bit data bus: • Desktop lower-performance: i386SX Alternative Names: Pentium II, PII • Desktop higher-performance: Desktop 6th Generation Core i7 (i7-6xxx, S-H), Desktop 7th Generation Core i7 X (i7-7xxxX, X), Desktop 7th Series: nm) 8088 (iAPX 88) • Mobile: i386SL, 80376, i386EX, Series: Pentium II 233/266/300 steppings C0 and C1 (Klamath, used in desktops) Generation Core i9 X (i7-7xxxXE, i7-7xxxX, X), Desktop 9th Generation Core i7 X (i7-9xxxX, X, 14 nm++?), Desktop 9th Generation Core i9 X • Desktop/Server: P5, P54C • Desktop higher-performance: Pentium 4 1.xA (Northwood, 130 nm), Pentium 4 2.x (except 2.0, 2.40A, i386CXSA, i386SXSA, i386CXSB New instructions: Deschutes (1998, 0.25 to 0.18 μm) (i7-9xxxXE, i7-9xxxX, X, 14 nm++?), Xeon W-3175X (W, 14 nm++?)