Diode-Connected BJT

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Chapter 7: AC Transistor Amplifiers

Chapter 7: Transistors, part 2 Chapter 7: AC Transistor Amplifiers The transistor amplifiers that we studied in the last chapter have some serious problems for use in AC signals. Their most serious shortcoming is that there is a “dead region” where small signals do not turn on the transistor. So, if your signal is smaller than 0.6 V, or if it is negative, the transistor does not conduct and the amplifier does not work. Design goals for an AC amplifier Before moving on to making a better AC amplifier, let’s define some useful terms. We define the output range to be the range of possible output voltages. We refer to the maximum and minimum output voltages as the rail voltages and the output swing is the difference between the rail voltages. The input range is the range of input voltages that produce outputs which are not at either rail voltage. Our goal in designing an AC amplifier is to get an input range and output range which is symmetric around zero and ensure that there is not a dead region. To do this we need make sure that the transistor is in conduction for all of our input range. How does this work? We do it by adding an offset voltage to the input to make sure the voltage presented to the transistor’s base with no input signal, the resting or quiescent voltage , is well above ground. In lab 6, the function generator provided the offset, in this chapter we will show how to design an amplifier which provides its own offset. -

Basic DC Motor Circuits

Basic DC Motor Circuits Living with the Lab Gerald Recktenwald Portland State University [email protected] DC Motor Learning Objectives • Explain the role of a snubber diode • Describe how PWM controls DC motor speed • Implement a transistor circuit and Arduino program for PWM control of the DC motor • Use a potentiometer as input to a program that controls fan speed LWTL: DC Motor 2 What is a snubber diode and why should I care? Simplest DC Motor Circuit Connect the motor to a DC power supply Switch open Switch closed +5V +5V I LWTL: DC Motor 4 Current continues after switch is opened Opening the switch does not immediately stop current in the motor windings. +5V – Inductive behavior of the I motor causes current to + continue to flow when the switch is opened suddenly. Charge builds up on what was the negative terminal of the motor. LWTL: DC Motor 5 Reverse current Charge build-up can cause damage +5V Reverse current surge – through the voltage supply I + Arc across the switch and discharge to ground LWTL: DC Motor 6 Motor Model Simple model of a DC motor: ❖ Windings have inductance and resistance ❖ Inductor stores electrical energy in the windings ❖ We need to provide a way to safely dissipate electrical energy when the switch is opened +5V +5V I LWTL: DC Motor 7 Flyback diode or snubber diode Adding a diode in parallel with the motor provides a path for dissipation of stored energy when the switch is opened +5V – The flyback diode allows charge to dissipate + without arcing across the switch, or without flowing back to ground through the +5V voltage supply. -

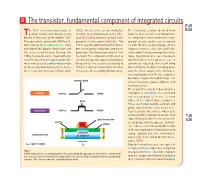

The Transistor, Fundamental Component of Integrated Circuits

D The transistor, fundamental component of integrated circuits he first transistor was made in (SiO2), which serves as an insulator. The transistor, a name derived from Tgermanium by John Bardeen and In 1958, Jack Kilby invented the inte- transfer and resistor, is a fundamen- Walter H. Brattain, in December 1947. grated circuit by manufacturing 5 com- tal component of microelectronic inte- The year after, along with William B. ponents on the same substrate. The grated circuits, and is set to remain Shockley at Bell Laboratories, they 1970s saw the advent of the first micro- so with the necessary changes at the developed the bipolar transistor and processor, produced by Intel and incor- nanoelectronics scale: also well-sui- the associated theory. During the porating 2,250 transistors, and the first ted to amplification, among other func- 1950s, transistors were made with sili- memory. The complexity of integrated tions, it performs one essential basic con (Si), which to this day remains the circuits has grown exponentially (dou- function which is to open or close a most widely-used semiconductor due bling every 2 to 3 years according to current as required, like a switching to the exceptional quality of the inter- “Moore's law”) as transistors continue device (Figure). Its basic working prin- face created by silicon and silicon oxide to become increasingly miniaturized. ciple therefore applies directly to pro- cessing binary code (0, the current is blocked, 1 it goes through) in logic cir- control gate cuits (inverters, gates, adders, and memory cells). The transistor, which is based on the switch source drain transport of electrons in a solid and not in a vacuum, as in the electron gate tubes of the old triodes, comprises three electrodes (anode, cathode and gate), two of which serve as an elec- transistor source drain tron reservoir: the source, which acts as the emitter filament of an electron gate insulator tube, the drain, which acts as the col- source lector plate, with the gate as “control- gate drain ler”. -

Fundamentals of MOSFET and IGBT Gate Driver Circuits

Application Report SLUA618A–March 2017–Revised October 2018 Fundamentals of MOSFET and IGBT Gate Driver Circuits Laszlo Balogh ABSTRACT The main purpose of this application report is to demonstrate a systematic approach to design high performance gate drive circuits for high speed switching applications. It is an informative collection of topics offering a “one-stop-shopping” to solve the most common design challenges. Therefore, it should be of interest to power electronics engineers at all levels of experience. The most popular circuit solutions and their performance are analyzed, including the effect of parasitic components, transient and extreme operating conditions. The discussion builds from simple to more complex problems starting with an overview of MOSFET technology and switching operation. Design procedure for ground referenced and high side gate drive circuits, AC coupled and transformer isolated solutions are described in great details. A special section deals with the gate drive requirements of the MOSFETs in synchronous rectifier applications. For more information, see the Overview for MOSFET and IGBT Gate Drivers product page. Several, step-by-step numerical design examples complement the application report. This document is also available in Chinese: MOSFET 和 IGBT 栅极驱动器电路的基本原理 Contents 1 Introduction ................................................................................................................... 2 2 MOSFET Technology ...................................................................................................... -

Power MOSFET Basics by Vrej Barkhordarian, International Rectifier, El Segundo, Ca

Power MOSFET Basics By Vrej Barkhordarian, International Rectifier, El Segundo, Ca. Breakdown Voltage......................................... 5 On-resistance.................................................. 6 Transconductance............................................ 6 Threshold Voltage........................................... 7 Diode Forward Voltage.................................. 7 Power Dissipation........................................... 7 Dynamic Characteristics................................ 8 Gate Charge.................................................... 10 dV/dt Capability............................................... 11 www.irf.com Power MOSFET Basics Vrej Barkhordarian, International Rectifier, El Segundo, Ca. Discrete power MOSFETs Source Field Gate Gate Drain employ semiconductor Contact Oxide Oxide Metallization Contact processing techniques that are similar to those of today's VLSI circuits, although the device geometry, voltage and current n* Drain levels are significantly different n* Source t from the design used in VLSI ox devices. The metal oxide semiconductor field effect p-Substrate transistor (MOSFET) is based on the original field-effect Channel l transistor introduced in the 70s. Figure 1 shows the device schematic, transfer (a) characteristics and device symbol for a MOSFET. The ID invention of the power MOSFET was partly driven by the limitations of bipolar power junction transistors (BJTs) which, until recently, was the device of choice in power electronics applications. 0 0 V V Although it is not possible to T GS define absolutely the operating (b) boundaries of a power device, we will loosely refer to the I power device as any device D that can switch at least 1A. D The bipolar power transistor is a current controlled device. A SB (Channel or Substrate) large base drive current as G high as one-fifth of the collector current is required to S keep the device in the ON (c) state. Figure 1. Power MOSFET (a) Schematic, (b) Transfer Characteristics, (c) Also, higher reverse base drive Device Symbol. -

Chapter 4: the MOS Transistor

Chapter 4: the MOS transistor 1. Introduction First products in Complementary Metal Oxide Silicon (CMOS) technology appeared in the market in seventies. At the beginning, CMOS devices were reserved for logic, as they offer the highest density (in gates/mm2), and the lowest static power consumption. Most high‐frequency circuitry was carried out in bipolar technology. As a result, a lot of analog functions were realized in bipolar technology. The technology development, which is driven by digital circuits (in particular by flash memories), lead to smaller and faster CMOS devices. At the beginning of the seventies, 1µm transistors length was considered short. Currently, CMOS technology with 22nm channel length is available. In the last twenty years a lot of analog circuits started to be developed in CMOS technology. In fact, the technology scaling enabled CMOS devices at higher frequencies of working, also for the analog counterpart. Today, CMOS and bipolar technologies are in competition over a wide frequency region up to 100GHz. The challenge indeed, to choice the technology that fulfills best the system and circuit requirements at a reasonable cost. Bipolar is more expensive than standard CMOS technology. Moreover, most systems and circuits are mixed signal, i.e. they include digital and analog parts. In the past, separated integrated circuits were dedicated to the analog (bipolar) and digital (CMOS) circuits. As analog circuits were also available in CMOS technology, this technology started to offer the opportunity to integrate cheap, high density and low power digital circuits, as well as analog circuits, in the same chip. This brings enormous advantages in terms of reduced costs and smaller form factors of electronic devices. -

CMOS Basics MOS: Metal Oxide Semiconductor Transistors Are Built on a Silicon

Principles of VLSI Design CMOS Basics CMPE 413 MOS: Metal Oxide Semiconductor Transistors are built on a Silicon (semiconductor) substrate. Pure silicon has no free carriers and conducts poorly. Dopants are added to increase conductivity: extra electrons (n-type) or extra holes (p-type) MOS structure created by superimposing several layers of conducting, insulating and tran- sistor-forming materials. Metal gate has been replaced by polysilicon or poly in modern technologies. There are two types of MOS transistors: nMOS : Negatively doped silicon, rich in electrons. pMOS : Positively doped silicon, rich in holes. CMOS: Both type of transistors are used to construct any gate. 1 Principles of VLSI Design CMOS Basics CMPE 413 nMOS and pMOS Four terminal devices: Source, Gate, Drain, body (substrate, bulk). SourceGate Drain Polysilicon Thin W Oxide SiO2 Source Gate Drain L nMOS n+ n+ n+ p bulk Si p substrate n+ SourceGate Drain Polysilicon SiO2 pMOS p+ p+ n bulk Si 2 Principles of VLSI Design CMOS Basics CMPE 413 CMOS Inverter Cross-Section Cadence Layer's for AMI 0.6mm technology m1-m2 contact (via) p-diffusion contact (cc) p-substrate contact (cc) (source) metal2 metal1 n-diffusion contact (cc) n-substrate contact (cc) (source) (Out) glass(insulator) VDD GND layer #3 layer #2 layer #1 p+ n+ n+ p+ p+ n+ (pactive) (drains) n-well (nwell) (nactive) p substrate (black background) n-transistor polysilicon gate (poly ) p-transistor 3 Principles of VLSI Design CMOS Basics CMPE 413 CMOS Cadence Layout Cadence Layout for the inverter on previous slide 4 Principles of VLSI Design CMOS Basics CMPE 413 MOS Transistor Switches We can treat MOS transistors as simple on-off switches with a source (S), gate (G) (con- trols the state of the switch) and drain (D). -

Designing Combinational Logic Gates in Cmos

CHAPTER 6 DESIGNING COMBINATIONAL LOGIC GATES IN CMOS In-depth discussion of logic families in CMOS—static and dynamic, pass-transistor, nonra- tioed and ratioed logic n Optimizing a logic gate for area, speed, energy, or robustness n Low-power and high-performance circuit-design techniques 6.1 Introduction 6.3.2 Speed and Power Dissipation of Dynamic Logic 6.2 Static CMOS Design 6.3.3 Issues in Dynamic Design 6.2.1 Complementary CMOS 6.3.4 Cascading Dynamic Gates 6.5 Leakage in Low Voltage Systems 6.2.2 Ratioed Logic 6.4 Perspective: How to Choose a Logic Style 6.2.3 Pass-Transistor Logic 6.6 Summary 6.3 Dynamic CMOS Design 6.7 To Probe Further 6.3.1 Dynamic Logic: Basic Principles 6.8 Exercises and Design Problems 197 198 DESIGNING COMBINATIONAL LOGIC GATES IN CMOS Chapter 6 6.1Introduction The design considerations for a simple inverter circuit were presented in the previous chapter. In this chapter, the design of the inverter will be extended to address the synthesis of arbitrary digital gates such as NOR, NAND and XOR. The focus will be on combina- tional logic (or non-regenerative) circuits that have the property that at any point in time, the output of the circuit is related to its current input signals by some Boolean expression (assuming that the transients through the logic gates have settled). No intentional connec- tion between outputs and inputs is present. In another class of circuits, known as sequential or regenerative circuits —to be dis- cussed in a later chapter—, the output is not only a function of the current input data, but also of previous values of the input signals (Figure 6.1). -

AI Chips: What They Are and Why They Matter

APRIL 2020 AI Chips: What They Are and Why They Matter An AI Chips Reference AUTHORS Saif M. Khan Alexander Mann Table of Contents Introduction and Summary 3 The Laws of Chip Innovation 7 Transistor Shrinkage: Moore’s Law 7 Efficiency and Speed Improvements 8 Increasing Transistor Density Unlocks Improved Designs for Efficiency and Speed 9 Transistor Design is Reaching Fundamental Size Limits 10 The Slowing of Moore’s Law and the Decline of General-Purpose Chips 10 The Economies of Scale of General-Purpose Chips 10 Costs are Increasing Faster than the Semiconductor Market 11 The Semiconductor Industry’s Growth Rate is Unlikely to Increase 14 Chip Improvements as Moore’s Law Slows 15 Transistor Improvements Continue, but are Slowing 16 Improved Transistor Density Enables Specialization 18 The AI Chip Zoo 19 AI Chip Types 20 AI Chip Benchmarks 22 The Value of State-of-the-Art AI Chips 23 The Efficiency of State-of-the-Art AI Chips Translates into Cost-Effectiveness 23 Compute-Intensive AI Algorithms are Bottlenecked by Chip Costs and Speed 26 U.S. and Chinese AI Chips and Implications for National Competitiveness 27 Appendix A: Basics of Semiconductors and Chips 31 Appendix B: How AI Chips Work 33 Parallel Computing 33 Low-Precision Computing 34 Memory Optimization 35 Domain-Specific Languages 36 Appendix C: AI Chip Benchmarking Studies 37 Appendix D: Chip Economics Model 39 Chip Transistor Density, Design Costs, and Energy Costs 40 Foundry, Assembly, Test and Packaging Costs 41 Acknowledgments 44 Center for Security and Emerging Technology | 2 Introduction and Summary Artificial intelligence will play an important role in national and international security in the years to come. -

Integrated Circuit Design Macmillan New Electronics Series Series Editor: Paul A

Integrated Circuit Design Macmillan New Electronics Series Series Editor: Paul A. Lynn Paul A. Lynn, Radar Systems A. F. Murray and H. M. Reekie, Integrated Circuit Design Integrated Circuit Design Alan F. Murray and H. Martin Reekie Department of' Electrical Engineering Edinhurgh Unit·ersity Macmillan New Electronics Introductions to Advanced Topics M MACMILLAN EDUCATION ©Alan F. Murray and H. Martin Reekie 1987 All rights reserved. No reproduction, copy or transmission of this publication may be made without written permission. No paragraph of this publication may be reproduced, copied or transmitted save with written permission or in accordance with the provisions of the Copyright Act 1956 (as amended), or under the terms of any licence permitting limited copying issued by the Copyright Licensing Agency, 7 Ridgmount Street, London WC1E 7AE. Any person who does any unauthorised act in relation to this publication may be liable to criminal prosecution and civil claims for damages. First published 1987 Published by MACMILLAN EDUCATION LTD Houndmills, Basingstoke, Hampshire RG21 2XS and London Companies and representatives throughout the world British Library Cataloguing in Publication Data Murray, A. F. Integrated circuit design.-(Macmillan new electronics series). 1. Integrated circuits-Design and construction I. Title II. Reekie, H. M. 621.381'73 TK7874 ISBN 978-0-333-43799-5 ISBN 978-1-349-18758-4 (eBook) DOI 10.1007/978-1-349-18758-4 To Glynis and Christa Contents Series Editor's Foreword xi Preface xii Section I 1 General Introduction -

ES110 Transistor Current Amplifiers

Sonoma State University Department of Engineering Science Fall 2016 ES-110 Laboratory Introduction to Engineering & Laboratory Experience Transistors and Transistor Applications Introduction Transistors are divided into two general categories: Bipolar Junction Transistors (BJT) and Field-Effect Transistors (FET). The latter is divided into several different sub categories (JFET, MOSFET, etc.). Each type is manufactured in many different forms and sizes and one chooses a transistor based on the required parameter, which include current amplification, voltage amplification, switching speed, frequency response, power ratings, cost, etc. In this laboratory we will primarily use BJT Transistors and refer to other types when appropriate. Transistor can be packaged in single transistor or multiple transistor packages. Transistors are also commonly and abundantly used in many analog and digital integrated circuits. Here we will start with a single transistor and then combine two or more transistors in our circuits. Transistors may be used for voltage amplification, current amplification, power amplification, or for switches. Specific transistors are used for each application. Transistors are manufactured in different packages and some of the packages are shown in figure below. From left: TO-92; TO- 18; TO-220, and TO-3 (TO stands for Transfer Outline). Transistors in general have three pins, identified as Collector, Base and Emitter. The TO-3 type only has two pins (Base and Emitter) and its metal casing acts as a Collector. The three pins of field-effect transistors are called Source, Gate and Drain. There is no universal agreement on the arrangement of the pins and in order to identify transistor pins one must view the manufacturers' pin diagrams, which are easily accessible on the web. -

Power MOSFET Structure and Characteristics Application Note

Power MOSFET Structure and Characteristics Application Note Power MOSFET Structure and Characteristics Description This document explains structures and characteristics of power MOSFETs. © 2017 - 20 18 1 2018-07-26 Toshiba Electronic Devices & Storage Corporation Power MOSFET Structure and Characteristics Application Note Table of Contents Description ............................................................................................................................................ 1 Table of Contents ................................................................................................................................. 2 1. Structures and Characteristics ....................................................................................................... 3 1.1. Structures of Power MOSFETs ........................................................................................................... 3 1.2. Characteristics of Power MOSFETs .................................................................................................... 4 RESTRICTIONS ON PRODUCT USE.................................................................................................... 6 © 2017 - 2018 2 2018-07-26 Toshiba Electronic Devices & Storage Corporation Power MOSFET Structure and Characteristics Application Note 1. Structures and Characteristics Since Power MOSFETs operate principally as majority-carrier devices, they are not affected by minority carriers. This is in contrast to the situation with minority-carrier devices such as bipolar