FLEX 10K Embedded Programmable Logic Device Family Data Sheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Ultrascale Architecture PCB Design User Guide (UG583)

UltraScale Architecture PCB Design User Guide UG583 (v1.21) June 3, 2021 Revision History The following table shows the revision history for this document. Date Version Revision 06/03/2021 1.21 Chapter 1: Added Recommended Decoupling Capacitor Quantities for Zynq UltraScale+ Devices in UBVA530 Package. In Table 1-13, added row for 1.0 µF. Chapter 2: Added PCB Routing Guidelines for LPDDR4 Memories in High-Density Interconnect Boards. 02/12/2021 1.20 Chapter 1: Added XCKU19P to Table 1-4. Added XCVU23P-FFVJ1760 to Table 1-5. Added XCVU57P-FSVK2892 to Table 1-7. Added VU57P to Table 1-8. Updated first sentence in VCCINT_VCU Plane Design and Power Delivery. Chapter 2: Updated item 13 in General Memory Routing Guidelines. Updated first paragraph in PCB Guidelines for DDR4 SDRAM (PL and PS). Added Routing Rule Changes for Thicker Printed Circuit Boards. Chapter 3: Added XCZU42DR to Table 3-1. Added paragraph about clock forwarding capability in Gen 3 RFSoC devices to Recommended Clocking Options. Added Table 3-11. Updated Powering RFSoCs with Switch Regulators. Added Power Delivery Network Design for Time Division Duplex. Chapter 4: Added bullet about device without DQS pin to DDR Mode (100 MHz). In SD/SDIO, added note about external pull-up resistor after fifth bullet, and added two bullets about level shifters. Chapter 11: Replaced I/O with I/O/PSIO in Unconnected VCCO Pins. 09/02/2020 1.19 Chapter 1: In Table 1-4, updated packages for XQKU5P and XCVU7P, added row for XCVU23P-VSVA1365, and updated note 3. In Table 1-9, updated packages for XCZU3CG, XCZU6CG, XCZU9CG, XCZU3EG, XCZU6EG, XCZU9EG, and XCZU15EG. -

FLEX 10K Embedded Programmable Logic Family Data Sheet

FLEX 10K ® Embedded Programmable Logic Family October 1998, ver. 3.13 Data Sheet Features... ■ The industryÕs first embedded programmable logic device (PLD) family, providing system integration in a single device Ð Embedded array for implementing megafunctions, such as efficient memory and specialized logic functions Ð Logic array for general logic functions ■ High density Ð 10,000 to 250,000 typical gates (see Tables 1 and 2) Ð Up to 40,960 RAM bits; 2,048 bits per embedded array block (EAB), all of which can be used without reducing logic capacity ■ System-level features Ð MultiVoltª I/O interface support Ð 5.0-V tolerant input pins in FLEX¨ 10KA devices Ð Low power consumption (typical specification less than 0.5 mA in standby mode for most devices) Ð FLEX 10K and FLEX 10KA devices support peripheral component interconnect Special Interest GroupÕs (PCI-SIG) PCI Local Bus Specification, Revision 2.1 Ð FLEX 10KA devices include pull-up clamping diode, selectable on a pin-by-pin basis for 3.3-V PCI compliance Ð Select FLEX 10KA devices support 5.0-V PCI buses with eight or fewer loads Ð Built-in JTAG boundary-scan test (BST) circuitry compliant with IEEE Std. 1149.1-1990, available without consuming any device logic Table 1. FLEX 10K Device Features Feature EPF10K10 EPF10K20 EPF10K30 EPF10K40 EPF10K50 EPF10K10A EPF10K30A EPF10K50V Typical gates (logic and RAM), 10,000 20,000 30,000 40,000 50,000 Note (1) Usable gates 7,000 to 15,000 to 22,000 to 29,000 to 36,000 to 31,000 63,000 69,000 93,000 116,000 Logic elements (LEs) 576 1,152 1,728 2,304 2,880 Logic array blocks (LABs) 72 144 216 288 360 Embedded array blocks (EABs) 366810 Total RAM bits 6,144 12,288 12,288 16,384 20,480 Maximum user I/O pins 134 189 246 189 310 Altera Corporation 1 A-DS-F10K-03.13 FLEX 10K Embedded Programmable Logic Family Data Sheet Table 2. -

A+ Computer Maintenance

Multiple Category Scope and Sequence: Scope and Sequence Report For Course Standards and Objectives, Content, Skills, Vocabulary Wednesday, August 20, 2014, 12:35PM Course Standards and Unit Content Skills Vocabulary Objectives District U1: UT: CTE: Information Technology, UT: . Basic components and . Identify the component 1. Documentation Advanced Professionalism Grades 9-12, Computer Maintenance & functions of a computer of a basic computer 2. RAM A+ (Computer and Computer Repair (A+) . The art of elicitation . Effectively interface 3. OS Standard 2 with a customer to 4. Server Maintenance) Basics (Week 1, . Importance of respect and Students will demonstrate integrity when dealing with address their concerns 5. Memory Stick (11.9920) 1 Week) Troubleshooting, Repair and customers with their computer 6. My Documents (District) Maintenance Skills. Troubleshooting . Summarize the 7. Peripheral methodology troubleshooting 8. Plug and Play 2014-2015 9. Port (input/output) Objective 1 . Legacy vs Modern Ports process Collaboration . 10. Printer Given a scenario, explain the 11. Software troubleshooting theory. 12. Tablet PC a. Identify the problem - 13. Toner Question the user and identify 14. Toner Cartridge user changes to computer and 15. USB perform backups before 16. Mouse making changes 17. User Account b. Establish a theory of 18. WAV probable cause (question the 19. Anti-aliasing obvious) 20. Anti-static c. Test the theory to determine 21. Anti-Static Mat cause - Once theory is 22. Antistatic Bag confirmed determine next 23. Wrist Strap steps to resolve problem, If 24. Daily Backup theory is not confirmed re- 25. DHCP establish new theory or 26. DOS escalate 27. Laser Printer d. -

Introduction

Introduction ►Purpose • This course describes Freescale’s new 32-bit microcontroller: the Version 1 ColdFire core. ►Objectives • Explain the ColdFire family • Describe the features of the V1 ColdFire core • Explain the architecture, debug architecture, and microarchitecture of the V1 ColdFire core. ►Content • 36 pages • 3 questions ►Learning Time •60 minutes 1 Welcome to the “V1 ColdFire core” course, one of an exciting series of courses offered by Freescale. This course describes the details on Freescale’s new, ground breaking, 32-bit microcontroller, the Version 1 ColdFire core. The V1 ColdFire core was developed as part of the controller continuum. It introduces several exciting new features that place it at the forefront of a new era of compatibility between 8- and 32-bit processors. 1 Freescale Controller Continuum The Freescale Controller Continuum is our roadmap for ColdFire V4 8-bit and 32-bit compatibility ColdFire V3 ColdFire V2 32-bit ColdFire V1 FlexisFlexisTMTM TheThe ControllerController HCS08 core ContinuumContinuum “Connection“Connection Point”Point” RS08 core 8-bit 2 Freescale is redefining compatibility for the industry with our Controller Continuum. The Freescale Controller Continuum provides stepwise compatibility for an easy migration path up or down the performance spectrum From the ultra-low-end RS08 to our highest-performance ColdFire® V4 devices. The connection point on the Freescale Controller Continuum is the Flexis series of microcontrollers. This connection point is where complimentary families of S08 and V1 ColdFire cores share a common set of peripherals and development tools to deliver the ultimate in migration flexibility. Pin-for-pin compatibility between many Flexis devices allows controller exchanges without board redesign. -

MC34903/4/5, System Basis Chip Gen2 with High Speed CAN and LIN Interface

Freescale Semiconductor Document Number: MC34903_4_5 Technical Data Rev. 4.0, 10/2013 System Basis Chip with CAN 34903/4/5 34903/ High Speed and LIN Interface Industrial The 34903/4/5 is the second generation family of the System Basis Chip (SBC). It combines several features and enhances present module designs. The device works as an advanced power SYSTEM BASIS CHIP management unit for the MCU with additional integrated circuits such as sensors and CAN transceivers. It has a built-in enhanced high-speed CAN interface (ISO11898-2 and -5) with local and bus failure diagnostics, protection, and fail-safe operation modes. The SBC may include zero or one LIN 2.1 interface with LIN output pin switches. It includes up to four wake-up input pins that can also be configured as output drivers for flexibility. This device is powered by SMARTMOS technology. This device implements multiple Low-power (LP) modes, with very EK Suffix (Pb-free) low-current consumption. In addition, the device is part of a family 98ASA10556D concept where pin compatibility adds versatility to module design. 32-PIN SOIC The 34903/4/5 also implements an innovative and advanced fail-safe state machine and concept solution. Applications Features • Industrial process control • Voltage regulator for MCU, 5.0 or 3.3 V, part number selectable, with • Automation possibility of usage external PNP to extend current capability and • Motor control share power dissipation • Robotics • Voltage, current, and temperature protection • Extremely low quiescent current in LP modes • Fully-protected embedded 5.0 V regulator for the CAN driver • Multiple undervoltage detections to address various MCU specifications and system operation modes (i.e. -

Integrated Circuit Test Engineering Iana.Grout Integrated Circuit Test Engineering Modern Techniques

Integrated Circuit Test Engineering IanA.Grout Integrated Circuit Test Engineering Modern Techniques With 149 Figures 123 Ian A. Grout, PhD Department of Electronic and Computer Engineering University of Limerick Limerick Ireland British Library Cataloguing in Publication Data Grout, Ian Integrated circuit test engineering: modern techniques 1. Integrated circuits - Verification I. Title 621.3’81548 ISBN-10: 1846280230 Library of Congress Control Number: 2005929631 ISBN-10: 1-84628-023-0 e-ISBN: 1-84628-173-3 Printed on acid-free paper ISBN-13: 978-1-84628-023-8 © Springer-Verlag London Limited 2006 HSPICE® is the registered trademark of Synopsys, Inc., 700 East Middlefield Road, Mountain View, CA 94043, U.S.A. http://www.synopsys.com/home.html MATLAB® is the registered trademark of The MathWorks, Inc., 3 Apple Hill Drive Natick, MA 01760- 2098, U.S.A. http://www.mathworks.com Verifault-XL®, Verilog® and PSpice® are registered trademarks of Cadence Design Systems, Inc., 2655 Seely Avenue, San Jose, CA 95134, U.S.A. http://www.cadence.com/index.aspx T-Spice™ is the trademark of Tanner Research, Inc., 2650 East Foothill Blvd. Pasadena, CA 91107, U.S.A. http://www.tanner.com/ Apart from any fair dealing for the purposes of research or private study, or criticism or review, as permitted under the Copyright, Designs and Patents Act 1988, this publication may only be reproduced, stored or transmitted, in any form or by any means, with the prior permission in writing of the publishers, or in the case of reprographic reproduction in accordance with the terms of licences issued by the Copyright Licensing Agency. -

Research, Development and Testing of a Fault-Tolerant Fpga-Based Sequencer for Cubesat Launching Applications

Calhoun: The NPS Institutional Archive Theses and Dissertations Thesis Collection 2013-03 RESEARCH, DEVELOPMENT AND TESTING OF A FAULT-TOLERANT FPGA-BASED SEQUENCER FOR CUBESAT LAUNCHING APPLICATIONS Parobek, Lucas S. Monterey, California. Naval Postgraduate School http://hdl.handle.net/10945/32882 NAVAL POSTGRADUATE SCHOOL MONTEREY, CALIFORNIA THESIS RESEARCH, DEVELOPMENT AND TESTING OF A FAULT-TOLERANT FPGA-BASED SEQUENCER FOR CUBESAT LAUNCHING APPLICATIONS by Lucas S. Parobek March 2013 Thesis Co-Advisors: Herschel H. Loomis, Jr. James H. Newman Approved for public release; distribution is unlimited THIS PAGE INTENTIONALLY LEFT BLANK REPORT DOCUMENTATION PAGE Form Approved OMB No. 0704–0188 Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instruction, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202–4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704–0188) Washington DC 20503. 1. AGENCY USE ONLY (Leave blank) 2. REPORT DATE 3. REPORT TYPE AND DATES COVERED March 2013 Master’s Thesis 4. TITLE AND SUBTITLE RESEARCH, DEVELOPMENT AND TESTING OF 5. FUNDING NUMBERS A FAULT-TOLERANT FPGA-BASED SEQUENCER FOR CUBESAT LAUNCHING APPLICATIONS 6. AUTHOR(S) Lucas S. Parobek 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES) 8. PERFORMING ORGANIZATION Naval Postgraduate School REPORT NUMBER Monterey, CA 93943–5000 9. -

AURIX™ 32-Bit Microcontrollers for Automotive and Industrial Applications Highly Integrated and Performance Optimized

AURIX™ 32-bit microcontrollers for automotive and industrial applications Highly integrated and performance optimized Issue 2020 www.infineon.com/aurix Contents TriCore™ family concept 3 AURIX™ for powertrain applications 36 Evolution of TriCore™ generations 4 AURIX™ for xEV applications 43 TriCore™ based product roadmap 5 AURIX™ for safety applications 48 AURIX™ product selector 6 AURIX™ for connectivity applications 61 PRO-SIL™ safety concept 7 AURIX™ for transportation applications 67 AURIX™ family housing options 8 AURIX™ for industrial applications 75 AURIX™ family system architecture 9 Tool partners 85 Peripheral highlights 14 AURIX™ security features 18 Embedded software (AUTOSAR etc.) 21 Development support 23 Multicore software development with AURIX™ 24 Kits and evaluation boards 25 Ease of use 29 AURIX™ solution finder 29 AURIX™ forum 30 Artificial intelligence in AURIX™ TC3xx 31 AURIX™ Development Studio 32 AURIX™ and XMC™ PDH partners 33 2 Family highlights › Compatibility and scalability › Easy to use › Lowest system cost › Broad portfolio › Industry benchmark system › Certified to automotive standards performance Applications › Powertrain domain controller › Diesel direct injection › Gasoline direct injection › Automatic transmission Gasoline multi-port injection Transfer case/torque vectoring › › Powertrain Applications › Battery management › Inverter › Off-board charging › Low-voltage DC-DC xEV › Charging station › High-voltage DC-DC Applications › Chassis domain control › Short-range radar (24/60 GHz) system › Electric -

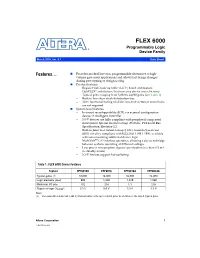

FLEX 6000 Programmable Logic Device Family Data Sheet

FLEX 6000 Programmable Logic ® Device Family March 2001, ver. 4.1 Data Sheet Features... ■ Provides an ideal low-cost, programmable alternative to high- volume gate array applications and allows fast design changes during prototyping or design testing ■ Product features – Register-rich, look-up table- (LUT-) based architecture – OptiFLEX® architecture that increases device area efficiency – Typical gates ranging from 5,000 to 24,000 gates (see Table 1) – Built-in low-skew clock distribution tree – 100% functional testing of all devices; test vectors or scan chains are not required ■ System-level features – In-circuit reconfigurability (ICR) via external configuration device or intelligent controller – 5.0-V devices are fully compliant with peripheral component interconnect Special Interest Group (PCI SIG) PCI Local Bus Specification, Revision 2.2 – Built-in Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry compliant with IEEE Std. 1149.1-1990, available without consuming additional device logic –MultiVoltTM I/O interface operation, allowing a device to bridge between systems operating at different voltages – Low power consumption (typical specification less than 0.5 mA in standby mode) – 3.3-V devices support hot-socketing Table 1. FLEX 6000 Device Features Feature EPF6010A EPF6016 EPF6016A EPF6024A Typical gates (1) 10,000 16,000 16,000 24,000 Logic elements (LEs) 880 1,320 1,320 1,960 Maximum I/O pins 102 204 171 218 Supply voltage (VCCINT) 3.3 V 5.0 V 3.3 V 3.3 V Note: (1) The embedded IEEE Std. 1149.1 JTAG circuitry adds up to 14,000 gates in addition to the listed typical gates. -

RX FAMILY Renesas 32-Bit Microcontrollers

RX FAMILY Renesas 32-Bit Microcontrollers 2018.02 02-03 Maintaining and Advancing the Renesas Tradition Mid-range 32-bit microcontrollers built around an exclusive CPU core developed by Renesas The RX microcontroller (MCU) family is designed around a cutting-edge CPU core that is exclusive to Renesas. Built on differentiated technologies perfected over many years, RX MCUs deliver superior performance with excellent power efficiency. The 32-bit enhanced Harvard architecture provides very high code density, with sizes typical of 16-bit CPUs. Factory Office Home The flagship of the RX Family, with the highest speed and 32-bit best performance (4MB Flash / 512KB RAM) microcontroller The mainstream of family the RX Family, with high performance and an extensive product lineup The best balance between (4MB Flash / 512KB RAM) power efficiency and RX700 high performance (240MHz) (1MB Flash / 96KB RAM) RX600 The entry-level series (120MHz) designed for ultra-low power consumption RX200 (512KB Flash) (80MHz) CPU, Software, Tool Compatibility CONTENT RX100 (32MHz) RX Family Product Evolution ........................................................................04 RX Family Specifications ..............................................................................63 RX Family Roadmap and Extensibility..........................................................06 RX Family Safety Functions and Product Support .....................................130 Power and functionality poised to dominate the market: RX Family Solutions .....................................................................................08 -

Cyclone V Device Handbook Volume 1

Cyclone V Device Handbook Volume 1: Device Interfaces and Integration Subscribe CV-5V2 101 Innovation Drive 2020.07.24 San Jose, CA 95134 Send Feedback www.altera.com TOC-2 Logic Array Blocks and Adaptive Logic Modules in Cyclone V Devices Contents ® Logic Array Blocks and Adaptive Logic Modules in Cyclone V Devices......... 1-1 LAB ............................................................................................................................................................... 1-1 MLAB ............................................................................................................................................... 1-2 Local and Direct Link Interconnects ............................................................................................1-3 LAB Control Signals........................................................................................................................ 1-4 ALM Resources ............................................................................................................................... 1-5 ALM Output .................................................................................................................................... 1-6 ALM Operating Modes .............................................................................................................................. 1-8 Normal Mode ...................................................................................................................................1-8 Extended LUT Mode ..................................................................................................................... -

Introduction

Introduction Purpose • This course highlights the compatibility between the S08, 8-bit S08 QE, 32-bit 32- bit V1 QE, and Coldfire V2 microcontrollers and reviews the strengths and applications of the 8bit and 32-bit processors. Objectives • Understand the benefits of software, peripheral, and pin compatibility. • Explain the compatibility between the S08, 8-bit S08 QE, 32-bit 32-bit V1 QE, and Coldfire V2 microcontrollers • Understand the progression up and down the microcontroller family. Content • 38 pages • 4 questions Learning Time • 60 minutes Welcome to the “QE128 Unprecedented Compatibility” course, one of an exciting series of courses offered by Freescale. This courses describes how Freescale has achieved unprecedented compatibility with its processor designs. This course highlights the compatibility between the S08, 8-bit S08 QE, 32-bit V1 QE, and Coldfire V2 microcontrollers and reviews the strengths and applications of the 8bit and 32-bit processors. 1 Microcontroller Family V2 32-bit V1 QE 8 bit QE S08 This course will highlight the compatibility between the S08, 8 bit QE, 32 bit QE and Coldfire V2 devices and the progression up and down the device family. The course will then conclude with a review of the strengths and applications for both the 8bit and 32-bit processors. 2 Compatibility We hate getting stuck! • Right solution? • Enough features? • Adequate performance? ►Freescale designers developed the revolutionary QE128 incorporating a few key fundamentals • Unprecedented compatibility between 8-bit and 32-bit • Ultra-low power • Ease of use ►By offering pin, peripheral and tool compatibility, the QE microcontrollers make migration between 8- and 32-bit as easy as swapping a chip 3 Everybody hates to get stuck.