Risk Factors

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Intel® Xeon® Processor E3-1200 V2 Product Family and LGA 1155 Socket

Intel® Xeon® Processor E3-1200 v2 Product Family and LGA 1155 Socket Thermal/Mechanical Specifications and Design Guidelines May 2012 Document Number: 324973-001 NFORMATIONLegal Lines and Disclaimers IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications. Intel may make changes to specifications and product descriptions at any time, without notice. This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The Intel® Xeon® processor E3-1200 v2 product family and Intel® C200 Series Chipset family may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. -

Mack DFM Keynote

The future of lithography and its impact on design Chris Mack www.lithoguru.com 1 Outline • History Lessons – Moore’s Law – Dennard Scaling – Cost Trends • Is Moore’s Law Over? – Litho scaling? • The Design Gap • The Future is Here 2 1965: Moore’s Observation 100000 65,000 transistors 10000 Doubling each year 1000 100 Components per chip per Components 10 64 transistors! 1 1959 1961 1963 1965 1967 1969 1971 1973 1975 Year G. E. Moore, “Cramming More Components onto Integrated Circuits,” Electronics Vol. 38, No. 8 (Apr. 19, 1965) pp. 114-117. 3 Moore’s Law “Doubling every 1 – 2 years” 25 nm 100000000000 10000000000 feature size + die size 1000000000 100000000 10000000 1000000 Today only lithography 100000 25 µm contributes 10000 1000 Componentsper chip 100 feature size + die size + device cleverness 10 1 1959 1969 1979 1989 1999 2009 2019 Year 4 Dennard’s MOSFET Scaling Rules Device/Circuit Parameter Scaling Factor Device dimension/thickness 1/ λ Doping Concentration λ Voltage 1/ λ Current 1/ λ Robert Dennard Capacitance 1/ λ Delay time 1/ λ Transistorpower 1/ λ2 Power density 1 There are no trade-offs. Everything gets better when you shrink a transistor! 5 The Golden Age 1975 - 2000 • Dennard Scaling - as transistor shrinks it gets: – Faster – Lower power (constant power density) – Smaller/lighter • Moore’s Law – More transistors/chip & cost of transistor = ‒15%/year • More powerful chip for same price • Same chip for lower price – Many new applications – large increase in volume 6 Problems with Dennard Scaling • Voltage stopped shrinking -

Intel® Core™ I7 Processor Family for the LGA-2011 Socket

Intel® Core™ i7 Processor Family for the LGA-2011 Socket Datasheet, Volume 1 Supporting Desktop Intel® Core™ i7-3960X and i7-3970X Extreme Edition Processor for the LGA-2011 Socket Supporting Desktop Intel® Core™ i7-39xxK and i7-38xx Processor Series for the LGA-2011 Socket This is volume 1 of 2. February 2014 Reference Number: 326196-003 INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications. Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information. The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. -

Multiprocessing Contents

Multiprocessing Contents 1 Multiprocessing 1 1.1 Pre-history .............................................. 1 1.2 Key topics ............................................... 1 1.2.1 Processor symmetry ...................................... 1 1.2.2 Instruction and data streams ................................. 1 1.2.3 Processor coupling ...................................... 2 1.2.4 Multiprocessor Communication Architecture ......................... 2 1.3 Flynn’s taxonomy ........................................... 2 1.3.1 SISD multiprocessing ..................................... 2 1.3.2 SIMD multiprocessing .................................... 2 1.3.3 MISD multiprocessing .................................... 3 1.3.4 MIMD multiprocessing .................................... 3 1.4 See also ................................................ 3 1.5 References ............................................... 3 2 Computer multitasking 5 2.1 Multiprogramming .......................................... 5 2.2 Cooperative multitasking ....................................... 6 2.3 Preemptive multitasking ....................................... 6 2.4 Real time ............................................... 7 2.5 Multithreading ............................................ 7 2.6 Memory protection .......................................... 7 2.7 Memory swapping .......................................... 7 2.8 Programming ............................................. 7 2.9 See also ................................................ 8 2.10 References ............................................. -

ESC4000 G3/G3S Series 2U Rackmount Server User Guide E9711 First Edition October 2014

ESC4000 G3/G3S Series 2U Rackmount Server User Guide E9711 First Edition October 2014 Copyright © 2014 ASUSTeK COMPUTER INC. All Rights Reserved. No part of this manual, including the products and software described in it, may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means, except documentation kept by the purchaser for backup purposes, without the express written permission of ASUSTeK COMPUTER INC. (“ASUS”). ASUS provides this manual “as is” without warranty of any kind, either express or implied, including but not limited to the implied warranties or conditions of merchantability or fitness for a particular purpose. In no event shall ASUS, its directors, officers, employees, or agents be liable for any indirect, special, incidental, or consequential damages (including damages for loss of profits, loss of business, loss of use or data, interruption of business and the like), even if ASUS has been advised of the possibility of such damages arising from any defect or error in this manual or product. Specifications and information contained in this manual ae furnished for informational use only, and are subject to change at any time without notice, and should not be construed as a commitment by ASUS. ASUS assumes no responsibility or liability for any errors or inaccuracies that may appear in this manual, including the products and software described in it. Product warranty or service will not be extended if: (1) the product is repaired, modified or altered, unless such repair, modification of alteration is authorized in writing by ASUS; or (2) the serial number of the product is defaced or missing. -

Pcie-H610 Pcie-Q670-R20

Single Board Computer Full-size www.ieiworld.com PCIE-Q670-R20 PCIE-H610 Full-size PICMG 1.3 CPU card supports LGA 1155 32nm Intel® Core™ i7/i5/i3, Pentium® or Full-size PICMG 1.3 CPU Card supports 32nm LGA 1155 Intel® Core™ i7/i5/i3, Pentium® Celeron® CPU with Intel® Q67, DDR3, VGA, dual Intel® PCIe GbE, SATA 6Gb/s, PCIe Mini, or Celeron® CPU with Intel® H61, DDR3, VGA, USB 2.0, SATA 3Gb/s, Dual Realtek PCIe HD Audio and RoHS GbE, HD Audio and RoHS Dual-channel DDR3 Front panel 2 x RS-232 4 x SATA 3Gb/s 2 x RS-232 I²C Dual-channel DDR3 1333/1066 MHz SMBus TPM KB/MS Front RS-422/485 1333/1066 MHz SMBus panel KB/MS 2 x SATA 6Gb/s RS-422/485 I²C TPM FDD 2 x RS-232 LPTDIO LPT IR DIO CF-115XC-R10 USB 2.0 USB 2.0 IR 1U chassis compatible LAN1 Intel ® Intel® LAN Q67 LAN2 H61 VGA VGA IO-KIT-001-R20 DVI cable included in 4 x SATA 3Gb/s PCIe Mini TPM 1.2 Support 4 x USB 2.0 DVI-D Audio DVI model 6 x USB 2.0 Features ● PICMG 1.3 full-size graphics grade solution DDR3 1.35V ● LGA 1155 Intel® Core™ i7/i5/i3, Pentium® or Celeron® processors supported 1333 DDR3 SATA 3Gb/s ● Up to 16 GB 1333 MHz dual-channel DDR3 SDRAM ● Supports dual independent display by VGA Features TPM 1.2 Support ● Supports RAID function via SATA 6Gb/s and SATA 3Gb/s ● TPM v1.2 hardware security provided by the TPM module ● Full-size PICMG 1.3 graphics grade solution ● IEI One Key Recovery solution allows you to create rapid OS backup and recovery ● LGA 1155 Intel® Core™ i7/i5/i3, Pentium® or Celeron® processor supported ● Dual-channel 1333/1066 MHz DDR3/DDR3L SDRAM supported up -

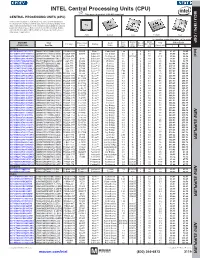

CPU) MCU / MPU / DSP This Page of Product Is Rohs Compliant

INTEL Central Processing Units (CPU) MPU /DSP MCU / This page of product is RoHS compliant. CENTRAL PROCESSING UNITS (CPU) Intel Processor families include the most powerful and flexible Central Processing Units (CPUs) available today. Utilizing industry leading 22nm device fabrication techniques, Intel continues to pack greater processing power into smaller spaces than ever before, providing desktop, mobile, and embedded products with maximum performance per watt across a wide range of applications. Atom Celeron Core Pentium Xeon For quantities greater than listed, call for quote. MOUSER Intel Core Cache Data Price Each Package Processor Family Code Freq. Size No. of Bus Width TDP STOCK NO. Part No. Series Name (GHz) (MB) Cores (bit) (Max) (W) 1 10 Desktop Intel 607-DF8064101211300Y DF8064101211300S R0VY FCBGA-559 D2550 Atom™ Cedarview 1.86 1 2 64 10 61.60 59.40 607-CM8063701444901S CM8063701444901S R10K FCLGA-1155 G1610 Celeron® Ivy Bridge 2.6 2 2 64 55 54.93 52.70 607-RK80532RC041128S RK80532RC041128S L6VR PPGA-478 - Celeron® Northwood 2.0 0.0156 1 32 52.8 42.00 40.50 607-CM8062301046804S CM8062301046804S R05J FCLGA-1155 G540 Celeron® Sandy Bridge 2.5 2 2 64 65 54.60 52.65 607-AT80571RG0641MLS AT80571RG0641MLS LGTZ LGA-775 E3400 Celeron® Wolfdale 2.6 1 2 64 65 54.93 52.70 607-HH80557PG0332MS HH80557PG0332MS LA99 LGA-775 E4300 Core™ 2 Conroe 1.8 2 2 64 65 139.44 133.78 607-AT80570PJ0806MS AT80570PJ0806MS LB9J LGA-775 E8400 Core™ 2 Wolfdale 3.0 6 2 64 65 207.04 196.00 607-AT80571PH0723MLS AT80571PH0723MLS LGW3 LGA-775 E7400 Core™ 2 Wolfdale -

3D-AFM Measurements for Semiconductor Structures and Devices

3D-AFM Measurements for Semiconductor Structures and Devices Ndubuisi G. Orji and Ronald G. Dixson Engineering Physics Division Physical Measurement Laboratory National Institute of Standards and Technology Gaithersburg, MD, 20899, USA Abstract This book chapter reviews different types of three-dimensional atomic force microscope (3D-AFM) measurements for semiconductor metrology. It covers different implementations of 3D-AFM, calibrations methods, measurement uncertainty considerations and applications. The goal is to outline key aspects of 3D-AFM for dimensional semiconductor measurements in a way that is accessible to both new and experienced users and gives readers a strong foundation for further study. Preprint version For published version see: N. G. Orji & R. G. Dixson “3D-AFM Measurements for Semiconductor Structures and Devices” In Metrology and Diagnostic Techniques for Nanoelectronics (eds. Z. Ma, & D. G. Seiler) (Pan Stanford, 2017). Official contributions of the U.S. Government, not subject to copyright. Certain commercial equipment, instruments, materials or companies are identified in this paper in order to specify the experimental procedure adequately, or to give full credit to sources of some material. Such identification is not intended to imply recommendation or endorsement by the National Institute of Standards and Technology, nor is it intended to imply that the materials or equipment identified are necessarily the best available for the purpose. 3D-AFM Measurements for Semiconductor Structures and Devices Table of -

Electrical Characterization and Modeling of Low Dimensional Nanostructure FET Jae Woo Lee

Electrical characterization and modeling of low dimensional nanostructure FET Jae Woo Lee To cite this version: Jae Woo Lee. Electrical characterization and modeling of low dimensional nanostructure FET. Autre. Université de Grenoble; 239 - Korea University, 2011. Français. NNT : 2011GRENT070. tel- 00767413 HAL Id: tel-00767413 https://tel.archives-ouvertes.fr/tel-00767413 Submitted on 19 Dec 2012 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. THÈSE Pour obtenir le grade de DOCTEUR DE LUNIVERSITÉ DE GRENOBLE Spécialité : Micro et Nano Électronique Arrêté ministériel : 7 août 2006 Présentée par Jae Woo LEE Thèse dirigée par Mireille MOUIS et Gérard GHIBAUDO préparée au sein du Laboratoire IMEP-LAHC dans l'École Doctorale EEATS Caractérisation électrique et modélisation des transistors à effet de champ de faible dimensionnalité Thèse soutenue publiquement le 5 décembre 2011 devant le jury composé de : M. Gérard GHIBAUDO DR CNRS Alpes-IMEP/INPG, Président M. Jong-Tae PARK Dr Incheon University, Rapporteur M. Jongwan JUNG Dr Sejong University, Rapporteur -

United States Securities and Exchange Commission Form

UNITED STATES SECURITIES AND EXCHANGE COMMISSION Washington, D.C. 20549 FORM 8-K CURRENT REPORT Pursuant to Section 13 OR 15(d) of The Securities Exchange Act of 1934 Date of Report: November 20, 2014 (Date of earliest event reported) INTEL CORPORATION (Exact name of registrant as specified in its charter) Delaware 000-06217 94-1672743 (State or other jurisdiction (Commission (IRS Employer of incorporation) File Number) Identification No.) 2200 Mission College Blvd., Santa Clara, California 95054-1549 (Address of principal executive offices) (Zip Code) (408) 765-8080 (Registrant's telephone number, including area code) (Former name or former address, if changed since last report) Check the appropriate box below if the Form 8-K filing is intended to simultaneously satisfy the filing obligation of the registrant under any of the following provisions (see General Instruction A.2. below): [ ] Written communications pursuant to Rule 425 under the Securities Act (17 CFR 230.425) [ ] Soliciting material pursuant to Rule 14a-12 under the Exchange Act (17 CFR 240.14a-12) [ ] Pre-commencement communications pursuant to Rule 14d-2(b) under the Exchange Act (17 CFR 240.14d-2(b)) [ ] Pre-commencement communications pursuant to Rule 13e-4(c) under the Exchange Act (17 CFR 240.13e-4c)) Item 7.01 Regulation FD Disclosure The information in this report shall not be treated as filed for purposes of the Securities Exchange Act of 1934, as amended. On November 20, 2014, Intel Corporation presented business and financial information to institutional investors, analysts, members of the press and the general public at a publicly available webcast meeting (the "Investor Meeting"). -

Intel® Core™ I7 Processor Families for the LGA2011-0 Socket

® Intel Core™ i7 Processor Families for the LGA2011-0 Socket Thermal Mechanical Specification and Design Guide — Supporting Desktop Intel® Core™ i7-3970X and i7-3960X Extreme Edition Processor Series for the LGA2011-0 Socket — Supporting Intel® Core™ i7-3000K Processor Series and Intel® Core™ i7-3000 Processor Series for the LGA2011-0 Socket — Supporting Desktop Intel® Core™ i7-4960X Extreme Edition Processor Series for the LGA2011 Socket — Supporting Desktop Intel® Core™ i7-49xx and i7-48xx Processor Series for the LGA2011 Socket November 2013 326199-004 INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The processors and LGA2011-0 socket may contain design defects or errors known as errata which may cause the product to deviate from published specifications. -

Mainboard Diagram

2012 ATX Industrial Motherboard NAF93-Q77 Based on Intel® Q77 Panther Point Platform for Ivy Bridge Jetway Computer Corporation Phone: 510-857-0130 Fax: 510-857-0138 38507 Cherry St., Ste E, Newark, CA 94560 www.jetwaycomputer.com NAF93-Q77 ATX Industrial Motherboard 1. Intel® Q77 Express Chipset HI08 2. Socket LGA 1155 for 3rd generation Intel Core i3, i5, i7 Processors 3. Dual Channel DDR3-1066/1333 up to 32GB 4. Intel 82579LM & 82574L PCI-E Gigabit LAN 5. Intel Active Management Technology (iAMT 8.0) 6. 2 * SATA2 6Gb/s, 4 * SATA2 3Gb/s with RAID 7. 1 * mSATA Slot for Embedded SSD 8. 1 * PCI-E 3.0 x16, 1 * PCI-E x4, 1 * PCI-E x1, 4 * PCI 9. 1 * PCI Express Mini Card Slot (half-size) 10. 10 * Serial Ports Onboard, TPM 1.2 Header 11. All Solid Polymer Capacitors for Improved Reliability 12. Industrial Embedded Platform with 5-Year Availability 2 / 3 NAF93-Q77 Specifications Model No: NAF93 HI08 Part No: JNAF93-Q77 Processor Socket LGA 1155 for 3nd-generation Intel Core i3, i5, i7 & Pentium processors (Ivy Bridge), Supports Turbo Boost 2.0, 64-bit, Hyper-Threading, Virtualization (VT-d), and Intel HD graphics on selected models* Chipset Intel Q77 Express chipset Video Intel HD graphics built into processors” Memory 4 * 240-pin DIMM Sockets for un-buffered dual channel DDR3-1066/1333 up to 32GB Storage 2 * SATA3 6Gb/s supporting RAID 0, 1 and 4 * SATA2 3Gb/s supporting RAID 0, 1, 5, 10 1 * mSATA 3Gb/s for embedded SSD Expansion Slots 1 * PCI Express 3.0 x16, 1 * PCI Express x4, 1 * PCI Express x1, 4 * PCI LAN 1 * Intel 82579LM PCI-E gigabit