Saving the Future of Moore's

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Imperial College London Department of Physics Graphene Field Effect

Imperial College London Department of Physics Graphene Field Effect Transistors arXiv:2010.10382v2 [cond-mat.mes-hall] 20 Jul 2021 By Mohamed Warda and Khodr Badih 20 July 2021 Abstract The past decade has seen rapid growth in the research area of graphene and its application to novel electronics. With Moore's law beginning to plateau, the need for post-silicon technology in industry is becoming more apparent. Moreover, exist- ing technologies are insufficient for implementing terahertz detectors and receivers, which are required for a number of applications including medical imaging and secu- rity scanning. Graphene is considered to be a key potential candidate for replacing silicon in existing CMOS technology as well as realizing field effect transistors for terahertz detection, due to its remarkable electronic properties, with observed elec- tronic mobilities reaching up to 2 × 105 cm2 V−1 s−1 in suspended graphene sam- ples. This report reviews the physics and electronic properties of graphene in the context of graphene transistor implementations. Common techniques used to syn- thesize graphene, such as mechanical exfoliation, chemical vapor deposition, and epitaxial growth are reviewed and compared. One of the challenges associated with realizing graphene transistors is that graphene is semimetallic, with a zero bandgap, which is troublesome in the context of digital electronics applications. Thus, the report also reviews different ways of opening a bandgap in graphene by using bi- layer graphene and graphene nanoribbons. The basic operation of a conventional field effect transistor is explained and key figures of merit used in the literature are extracted. Finally, a review of some examples of state-of-the-art graphene field effect transistors is presented, with particular focus on monolayer graphene, bilayer graphene, and graphene nanoribbons. -

Chapter 7: AC Transistor Amplifiers

Chapter 7: Transistors, part 2 Chapter 7: AC Transistor Amplifiers The transistor amplifiers that we studied in the last chapter have some serious problems for use in AC signals. Their most serious shortcoming is that there is a “dead region” where small signals do not turn on the transistor. So, if your signal is smaller than 0.6 V, or if it is negative, the transistor does not conduct and the amplifier does not work. Design goals for an AC amplifier Before moving on to making a better AC amplifier, let’s define some useful terms. We define the output range to be the range of possible output voltages. We refer to the maximum and minimum output voltages as the rail voltages and the output swing is the difference between the rail voltages. The input range is the range of input voltages that produce outputs which are not at either rail voltage. Our goal in designing an AC amplifier is to get an input range and output range which is symmetric around zero and ensure that there is not a dead region. To do this we need make sure that the transistor is in conduction for all of our input range. How does this work? We do it by adding an offset voltage to the input to make sure the voltage presented to the transistor’s base with no input signal, the resting or quiescent voltage , is well above ground. In lab 6, the function generator provided the offset, in this chapter we will show how to design an amplifier which provides its own offset. -

Nano Computing Revolution and Future Prospects

Recent Research in Science and Technology 2012, 4(3): 16-17 ISSN: 2076-5061 Available Online: http://recent-science.com/ Nano computing revolution and future prospects Deepti Hirwani and Anuradha Sharma Maharaja Agrasen International College, Raipur C.G, India Abstract There are several ways nanocomputers might be built, using mechanical, electronic, biochemical, or quantum technology. It is unlikely that nanocomputers will be made out of semiconductor transistors (Microelectronic components that are at the core of all modern electronic devices), as they seem to perform significantly less well when shrunk to sizes under 100 nanometers.The research results summarized here also suggest that many useful, yet strikingly different solutions may exist for tolerating defects and faults within nanocomputing systems. Also included in the survey are a number of software tools useful for quantifying the reliability of nanocomputing systems in the presence of defects and faults. Keywords: Nano computing, electronic devices, technology INTRODUCTION classical computer would have to repeat 2 x input numbers, Nanocomputer is the logical name for the computer smaller performing the same task that a classical computer would have to then the microcomputer, which is smaller than the minicomputer. repeat 2 x times or use 2 xprocessors working in parallel. In other (The minicomputer is called “mini” because it was a lot smaller than words a quantum computer offers an enormous gain in the use of the original (mainframe) computers.) More technically, it is a computational resources such as time and memory. This becomes computer whose fundamental part is no bigger than a few mind boggling when you think of what 32 qubits can accomplish. -

From Sand to Circuits

From sand to circuits By continually advancing silicon technology and moving the industry forward, we help empower people to do more. To enhance their knowledge. To strengthen their connections. To change the world. How Intel makes integrated circuit chips www.intel.com www.intel.com/museum Copyright © 2005Intel Corporation. All rights reserved. Intel, the Intel logo, Celeron, i386, i486, Intel Xeon, Itanium, and Pentium are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries. *Other names and brands may be claimed as the property of others. 0605/TSM/LAI/HP/XK 308301-001US From sand to circuits Revolutionary They are small, about the size of a fingernail. Yet tiny silicon chips like the Intel® Pentium® 4 processor that you see here are changing the way people live, work, and play. This Intel® Pentium® 4 processor contains more than 50 million transistors. Today, silicon chips are everywhere — powering the Internet, enabling a revolution in mobile computing, automating factories, enhancing cell phones, and enriching home entertainment. Silicon is at the heart of an ever expanding, increasingly connected digital world. The task of making chips like these is no small feat. Intel’s manufacturing technology — the most advanced in the world — builds individual circuit lines 1,000 times thinner than a human hair on these slivers of silicon. The most sophisticated chip, a microprocessor, can contain hundreds of millions or even billions of transistors interconnected by fine wires made of copper. Each transistor acts as an on/off switch, controlling the flow of electricity through the chip to send, receive, and process information in a fraction of a second. -

Part III. Functional Polymers for Semiconductor Applications Outline

Functional Polymer/1st Semester, 2006 _________________________________________ Part III. Functional Polymers for Semiconductor Applications Outline of Part Photoresist for Semiconductor Applications Introduction of photolithography Photoresist Materials for Exposure at 193 nm Wavelength Chemically Amplified Resists for F2 Excimer laser Lithography Prof. Jin-Heong Yim Motivations Creation of integrated circuits, which are a major component in computer technology An extension of photolithography processes are used to create standard semiconductor chips Play a key role in the production of technically demanding components of advanced microsensors Used to make adhesives in electronics Prof. Jin-Heong Yim History Historically, lithography is a type of printing technology that is based on the chemical repellence of oil and water. Photo-litho-graphy: latin: light-stone-writing In 1826, Joseph Nicephore Niepce, in Chalon, France, takes the first photograph using bitumen of Judea on a pewter plate, developed using oil of lavender and mineral spirits In 1935 Louis Minsk of Eastman Kodak developed the first negative photoresist In 1940 Otto Suess developed the first positive photoresist. In 1954, Louis Plambeck, Jr., of Du Pont, develops the Dycryl polymeric letterpress plate Prof. Jin-Heong Yim Microlithography A process that involves transferring an integrated circuit pattern into a polymer film and subsequently replicating that pattern in an underlying thin conductor or dielectric film Prof. Jin-Heong Yim How Small Can We Print ? SEM picture of typical lithographic pattern Comparison of the dimensions of lithographic images and familiar objects Thompson, L. F.; Willson, C. G.; Bowden, M. J. Introduction to Microlithography; 2nd Ed; ACS Professional Reference Book; American Chemical Society; Washington, DC, 1994 Prof. -

Basic DC Motor Circuits

Basic DC Motor Circuits Living with the Lab Gerald Recktenwald Portland State University [email protected] DC Motor Learning Objectives • Explain the role of a snubber diode • Describe how PWM controls DC motor speed • Implement a transistor circuit and Arduino program for PWM control of the DC motor • Use a potentiometer as input to a program that controls fan speed LWTL: DC Motor 2 What is a snubber diode and why should I care? Simplest DC Motor Circuit Connect the motor to a DC power supply Switch open Switch closed +5V +5V I LWTL: DC Motor 4 Current continues after switch is opened Opening the switch does not immediately stop current in the motor windings. +5V – Inductive behavior of the I motor causes current to + continue to flow when the switch is opened suddenly. Charge builds up on what was the negative terminal of the motor. LWTL: DC Motor 5 Reverse current Charge build-up can cause damage +5V Reverse current surge – through the voltage supply I + Arc across the switch and discharge to ground LWTL: DC Motor 6 Motor Model Simple model of a DC motor: ❖ Windings have inductance and resistance ❖ Inductor stores electrical energy in the windings ❖ We need to provide a way to safely dissipate electrical energy when the switch is opened +5V +5V I LWTL: DC Motor 7 Flyback diode or snubber diode Adding a diode in parallel with the motor provides a path for dissipation of stored energy when the switch is opened +5V – The flyback diode allows charge to dissipate + without arcing across the switch, or without flowing back to ground through the +5V voltage supply. -

The Economic Impact of Moore's Law: Evidence from When It Faltered

The Economic Impact of Moore’s Law: Evidence from when it faltered Neil Thompson Sloan School of Management, MIT1 Abstract “Computing performance doubles every couple of years” is the popular re- phrasing of Moore’s Law, which describes the 500,000-fold increase in the number of transistors on modern computer chips. But what impact has this 50- year expansion of the technological frontier of computing had on the productivity of firms? This paper focuses on the surprise change in chip design in the mid-2000s, when Moore’s Law faltered. No longer could it provide ever-faster processors, but instead it provided multicore ones with stagnant speeds. Using the asymmetric impacts from the changeover to multicore, this paper shows that firms that were ill-suited to this change because of their software usage were much less advantaged by later improvements from Moore’s Law. Each standard deviation in this mismatch between firm software and multicore chips cost them 0.5-0.7pp in yearly total factor productivity growth. These losses are permanent, and without adaptation would reflect a lower long-term growth rate for these firms. These findings may help explain larger observed declines in the productivity growth of users of information technology. 1 I would like to thank my PhD advisors David Mowery, Lee Fleming, Brian Wright and Bronwyn Hall for excellent support and advice over the years. Thanks also to Philip Stark for his statistical guidance. This work would not have been possible without the help of computer scientists Horst Simon (Lawrence Berkeley National Lab) and Jim Demmel, Kurt Keutzer, and Dave Patterson in the Berkeley Parallel Computing Lab, I gratefully acknowledge their overall guidance, their help with the Berkeley Software Parallelism Survey and their hospitality in letting me be part of their lab. -

Nanoelectronics

Highlights from the Nanoelectronics for 2020 and Beyond (Nanoelectronics) NSI April 2017 The semiconductor industry will continue to be a significant driver in the modern global economy as society becomes increasingly dependent on mobile devices, the Internet of Things (IoT) emerges, massive quantities of data generated need to be stored and analyzed, and high-performance computing develops to support vital national interests in science, medicine, engineering, technology, and industry. These applications will be enabled, in part, with ever-increasing miniaturization of semiconductor-based information processing and memory devices. Continuing to shrink device dimensions is important in order to further improve chip and system performance and reduce manufacturing cost per bit. As the physical length scales of devices approach atomic dimensions, continued miniaturization is limited by the fundamental physics of current approaches. Innovation in nanoelectronics will carry complementary metal-oxide semiconductor (CMOS) technology to its physical limits and provide new methods and architectures to store and manipulate information into the future. The Nanoelectronics Nanotechnology Signature Initiative (NSI) was launched in July 2010 to accelerate the discovery and use of novel nanoscale fabrication processes and innovative concepts to produce revolutionary materials, devices, systems, and architectures to advance the field of nanoelectronics. The Nanoelectronics NSI white paper1 describes five thrust areas that focus the efforts of the six participating agencies2 on cooperative, interdependent R&D: 1. Exploring new or alternative state variables for computing. 2. Merging nanophotonics with nanoelectronics. 3. Exploring carbon-based nanoelectronics. 4. Exploiting nanoscale processes and phenomena for quantum information science. 5. Expanding the national nanoelectronics research and manufacturing infrastructure network. -

Biocompatibility of SU-8 and Its Biomedical Device Applications

micromachines Review Biocompatibility of SU-8 and Its Biomedical Device Applications Ziyu Chen and Jeong-Bong Lee * Department of Electrical and Computer Engineering, The University of Texas at Dallas, Richardson, TX 75080, USA; [email protected] * Correspondence: [email protected]; Tel.: +1-972-883-2893; Fax: +1-972-883-5842 Abstract: SU-8 is an epoxy-based, negative-tone photoresist that has been extensively utilized to fabricate myriads of devices including biomedical devices in the recent years. This paper first reviews the biocompatibility of SU-8 for in vitro and in vivo applications. Surface modification techniques as well as various biomedical applications based on SU-8 are also discussed. Although SU-8 might not be completely biocompatible, existing surface modification techniques, such as O2 plasma treatment or grafting of biocompatible polymers, might be sufficient to minimize biofouling caused by SU-8. As a result, a great deal of effort has been directed to the development of SU-8-based functional devices for biomedical applications. This review includes biomedical applications such as platforms for cell culture and cell encapsulation, immunosensing, neural probes, and implantable pressure sensors. Proper treatments of SU-8 and slight modification of surfaces have enabled the SU-8 as one of the unique choices of materials in the fabrication of biomedical devices. Due to the versatility of SU-8 and comparative advantages in terms of improved Young’s modulus and yield strength, we believe that SU-8-based biomedical devices would gain wider proliferation among the biomedical community in the future. Keywords: SU-8; biocompatibility; biosensing; biomedical; implantable Citation: Chen, Z.; Lee, J.-B. -

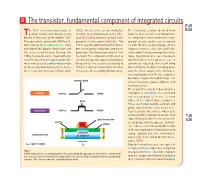

The Transistor, Fundamental Component of Integrated Circuits

D The transistor, fundamental component of integrated circuits he first transistor was made in (SiO2), which serves as an insulator. The transistor, a name derived from Tgermanium by John Bardeen and In 1958, Jack Kilby invented the inte- transfer and resistor, is a fundamen- Walter H. Brattain, in December 1947. grated circuit by manufacturing 5 com- tal component of microelectronic inte- The year after, along with William B. ponents on the same substrate. The grated circuits, and is set to remain Shockley at Bell Laboratories, they 1970s saw the advent of the first micro- so with the necessary changes at the developed the bipolar transistor and processor, produced by Intel and incor- nanoelectronics scale: also well-sui- the associated theory. During the porating 2,250 transistors, and the first ted to amplification, among other func- 1950s, transistors were made with sili- memory. The complexity of integrated tions, it performs one essential basic con (Si), which to this day remains the circuits has grown exponentially (dou- function which is to open or close a most widely-used semiconductor due bling every 2 to 3 years according to current as required, like a switching to the exceptional quality of the inter- “Moore's law”) as transistors continue device (Figure). Its basic working prin- face created by silicon and silicon oxide to become increasingly miniaturized. ciple therefore applies directly to pro- cessing binary code (0, the current is blocked, 1 it goes through) in logic cir- control gate cuits (inverters, gates, adders, and memory cells). The transistor, which is based on the switch source drain transport of electrons in a solid and not in a vacuum, as in the electron gate tubes of the old triodes, comprises three electrodes (anode, cathode and gate), two of which serve as an elec- transistor source drain tron reservoir: the source, which acts as the emitter filament of an electron gate insulator tube, the drain, which acts as the col- source lector plate, with the gate as “control- gate drain ler”. -

FAQ: Sic MOSFET Application Notes

FAQ SiC MOSFET Description This document introduces the Frequently Asked Questions and answers of SiC MOSFET. © 20 21 2021-3-22 Toshiba Electronic Devices & Storage Corporation 1 Table of Contents Description .............................................................................................................................................................. 1 Table of Contents .................................................................................................................................................... 2 List of Figures / List of Tables ................................................................................................................................ 3 1. What is SiC ? ...................................................................................................................................................... 4 2. Is it possible to connect multiple SiC MOSFETs in parallel ? ........................................................................... 5 ............................................................................... 6 .................................................................................... 7 5. If Si IGBT replaced with SiC MOSFET, what will change ? ............................................................................. 8 6. Is there anything to note about the Gate drive voltage ? ..................................................................................... 9 RESTRICTIONS ON PRODUCT USE .............................................................................................................. -

Fundamentals of MOSFET and IGBT Gate Driver Circuits

Application Report SLUA618A–March 2017–Revised October 2018 Fundamentals of MOSFET and IGBT Gate Driver Circuits Laszlo Balogh ABSTRACT The main purpose of this application report is to demonstrate a systematic approach to design high performance gate drive circuits for high speed switching applications. It is an informative collection of topics offering a “one-stop-shopping” to solve the most common design challenges. Therefore, it should be of interest to power electronics engineers at all levels of experience. The most popular circuit solutions and their performance are analyzed, including the effect of parasitic components, transient and extreme operating conditions. The discussion builds from simple to more complex problems starting with an overview of MOSFET technology and switching operation. Design procedure for ground referenced and high side gate drive circuits, AC coupled and transformer isolated solutions are described in great details. A special section deals with the gate drive requirements of the MOSFETs in synchronous rectifier applications. For more information, see the Overview for MOSFET and IGBT Gate Drivers product page. Several, step-by-step numerical design examples complement the application report. This document is also available in Chinese: MOSFET 和 IGBT 栅极驱动器电路的基本原理 Contents 1 Introduction ................................................................................................................... 2 2 MOSFET Technology ......................................................................................................