Minor Changes and Bug Fixes

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

PLM Weekly Summary Editor: Cimdata News Team 15 January 2021 Contents Cimdata News

PLM Weekly Summary Editor: CIMdata News Team 15 January 2021 Contents CIMdata News ............................................................................................................................................ 2 An Enterprise Digital Transformation Platform – a CIMdata Commentary......................................................2 Aras’ Cloud Strategy – a CIMdata Blog Post ....................................................................................................5 CIMdata Announces its 2021 PLM Market & Industry Forum Series ..............................................................6 CIMdata to Host a Free Webinar on CAD Trends ............................................................................................7 NLign Analytics “Structural Lifecycle Digital Environment” Enables Model-Driven Product Quality – a CIMdata Commentary .......................................................................................................................................8 PTC’s Cloud Strategy – a CIMdata Blog Post ................................................................................................. 13 Acquisitions .............................................................................................................................................. 14 Accenture Acquires Real Protect, Brazil-Based Information Security Company ........................................... 14 Atos to acquire In Fidem to reinforce its cybersecurity position in the North American market .................... 15 Planview -

Eagle Tutorial

EAGLE EASILY APPLICABLE GRAPHICAL LAYOUT EDITOR Tutorial Version 5 Schematic – Layout – Autorouter for Linux® Mac® Windows® CadSoft Computer www.cadsoftusa.com 6th Edition 005175100 Copyright © 2010 CadSoft Computer All Rights Reserved CadSoft Computer is a trading division of Newark Corporation. If you have any questions please feel free to contact us: USA and other countries: Phone: +1 (954) 237 0932 Fax: +1 (954) 237 0968 Internet: www.cadsoftusa.com Email: [email protected] Germany and other European countries: Phone: +49 (0)8635 6989-10 Hotline: +49 (0)8635 6989-30 Fax: +49 (0)8635 6989-40 Internet: www.cadsoft.de Email: [email protected] And remember that we offer a free hotline for our customers! Copyright 2010 CadSoft Computer. All rights reserved worldwide. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, scanning, digitizing, or otherwise, without the prior consense of CadSoft Computer. Printing this tutorial for your personal use is allowed. Windows is a registered trademark of Microsoft Corporation. Linux is a registered trademark of Linus Torvalds. Mac is a registered trademark of Apple Computer Inc. Table Of Contents 1 What to expect from this Tutorial...............................................................6 2 Features of EAGLE.......................................................................................7 System Requirements...............................................................................7 -

IDF Exporter IDF Exporter Ii

IDF Exporter IDF Exporter ii April 27, 2021 IDF Exporter iii Contents 1 Introduction to the IDFv3 exporter 2 2 Specifying component models for use by the exporter 2 3 Creating a component outline file 4 4 Guidelines for creating outlines 6 4.1 Package naming ................................................ 6 4.2 Comments .................................................... 6 4.3 Geometry and Part Number entries ...................................... 7 4.4 Pin orientation and positioning ........................................ 7 4.5 Tips on dimensions ............................................... 8 5 IDF Component Outline Tools 8 5.1 idfcyl ....................................................... 9 5.2 idfrect ...................................................... 10 5.3 dxf2idf ...................................................... 11 6 idf2vrml 12 IDF Exporter 1 / 12 Reference manual Copyright This document is Copyright © 2014-2015 by it’s contributors as listed below. You may distribute it and/or modify it under the terms of either the GNU General Public License (http://www.gnu.org/licenses/gpl.html), version 3 or later, or the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0/), version 3.0 or later. All trademarks within this guide belong to their legitimate owners. Contributors Cirilo Bernardo Feedback Please direct any bug reports, suggestions or new versions to here: • About KiCad document: https://gitlab.com/kicad/services/kicad-doc/issues • About KiCad software: https://gitlab.com/kicad/code/kicad/issues • About KiCad software i18n: https://gitlab.com/kicad/code/kicad-i18n/issues Publication date and software version Published on January 26, 2014. IDF Exporter 2 / 12 1 Introduction to the IDFv3 exporter The IDF exporter exports an IDFv3 1 compliant board (.emn) and library (.emp) file for communicating mechanical dimensions to a mechanical CAD package. -

S. No. SPECIFICATION for Features to Be Provided by PCB Design Tool

S. No. SPECIFICATION for features to be provided by PCB Design Tool Software 1 General Specification 1.1 Basic requirements The Electronics PCB Design Tool shall be a floating license with software for PCB design including schematic entry, component creation, component libraries, BOM generation, PCB placement and routing, ERC and DRC checks and exporting for manufacturing and documentation. 1.2 Import / export Should support for import and/or export of designs and library data created in similar reputed PCB CAD packages, viz. OrCAD®, Allegro®, PADS®, Cadstar®, Eagle®, P- CAD®, Protel®, Altium®, Mentor Graphics® DxDesigner®(Import), Mentor Graphics® Expedition(Import), Zuken® CADSTAR®(Import), P-CAD 1.3 Manufacturing File Outputs Should have facility to publish to PDF, print or web with a controlled view of a project's history and dependencies, generate Gerber, Gerber X2, NC Drill, ODB++ 3D video animations, and STEP files. 1.4 Assembly file outputs Should generate assembly drawings, pick and place file, test point report. 1.5 Batch processing Should support post processing using Batch Process 1.6 System The software shall work in 64bit Windows 7 , Requirements Windows 8 or Windows 10 version desktop / laptop. Linux support is desirable but not essential. The software should work on intranet from behind proxy server of the organization and internet connectivity should not be essential for its installation, use and upgrade. 2 Library 2.1 Library Management Should have unified library management based on a single data source for all component models and linked data including 3D models, data sheets and supplier links. 2.2 Library Should have library of major components from reputed manufacturers with provision to download files and work offline. -

Industrial Circuit Board Design and Microprocessor Programming Bachelor of Science Thesis in Mechatronics

Industrial circuit board design and microprocessor programming Bachelor of Science thesis in Mechatronics FREDRIK HÖGBERG Department of Signals and Systems CHALMERS UNIVERSITY OF TECHNOLOGY Gothenburg, Sweden 2017 REPORT NO. XXXX XXXX Industrial circuit boar! design and %icroprocessor pro$ram%in$ FREDRIK HÖGBERG Depart%ent of Signal and S'ste%s CH)*MERS UNI,ERSIT- OF TE(HNO*OG- Gothenbur$, S/eden 2017 Industrial circuit board design and microprocessor pro$ra%%in$ FREDRIK HÖGBERG FREDRIK HÖGBERG, 2017 Technical report no xxxx544 Depart%ent of Signals and S'ste%s Chal%ers +ni6ersit' of Technolo$' SE-412 96 G;tebor$ S/eden Telephone + 46 (0)31-772 1000 (o6er5 Hot Screen 2000 is an industrial heat press machine that can be used to attach screen prints on clothin$. This thesis will go in to details on ho/ the circuit board and pro$ra% was ma!e for this %achine. Chal%ers Reproservice G;tebor$. S/eden 2017 CHALMERS Signals and Systems, Bachelor@s Thesis XXXX5XX I Abstract The %ain obAect of this proAect is to design and %aBe circuitr' to control a industrial heat press %achine. The circuitr' consist of a 0 la'er boar! containin$ a %icro controller. displa' %odule. )( DC module. te%perature controller and electronics to control electromechanical devices. The fra%e of reference /ill $o through the basics steps in designin$ and %anufacturin$ electrical circ"itry /ith digital and analo$ technolo$y and explain the basics of the most com%on electrical components use! in circuitr' toda'. The fra%e of reference /ill also sho/ ho/ to create sche%atic and circuit design "sin$ Ki()D and ho/ to pro$ra% a Microchi& %icroprocessor in the C pro$ra%ing lan$"a$e. -

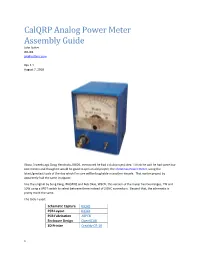

Calqrp Analog Power Meter Assembly Guide John Sutter W1JDS [email protected]

CalQRP Analog Power Meter Assembly Guide John Sutter W1JDS [email protected] Rev 1.1 August 7, 2018 About 3 weeks ago Doug Hendricks, KI6DS, mentioned he had a club project idea. I think he said he had some low cost meters and thought it would be good to spin an old project, the Christmas Power Meter, using the latest/greatest tools of the day which I’m sure will be laughable in another decade. That earlier project by apparently had the same instigator. Like the original by Song Kang, WA3AYQ and Bob Okas, W3CD, this version of the meter has two ranges, 1W and 10W using a SPDT switch to select between them instead of 2 BNC connectors. Beyond that, the schematic is pretty much the same. The tools I used: Schematic Capture KiCAD PCB Layout KiCAD PCB Fabrication AllPCB Enclosure Design OpenSCAD 3D Printer Creality CR-10 1 The Circuit As mentioned earlier the schematic matches the Christmas Power Meter pretty closely. SW1 is used to switch the power from the BNC connector into either the 10W load consisting of four 200 Ω 3 Watt carbon film resistors or the 1W load consisting of two 100 Ω ½ Watt carbon film resistors. The diodes are used as detectors with the resulting voltage filtered by the capacitors. The resistors are used to adjust the full-scale current to 200 μA. More on that later. FIGURE 1 SCHEMATIC A germanium diode was used on the 1 W range due to its lower voltage drop. More on that later. If you decide to use a through hole switch, the maximum shaft diameter is 6.3 mm. -

Tutorial and Design of Printed Circuit Board ”Big Blinky”

Paper ID #31292 An Electronics Lab Project—Tutorial and Design of Printed Circuit Board ”big blinky” Dr. Rod Blaine Foist, California Baptist University Rod Foist Professor (and IEEE student club advisor), Electrical and Computer Engineering, Gordon & Jill Bourns College of Engineering, California Baptist University, [email protected]. Dr. Foist received his B.S. and M.S. degrees in Electrical Engineering from the University of Washington in 1982 and 1989, respectively. He earned his Ph.D. degree in Electrical and Computer Engineering from the University of British Columbia in 2011, specializing in signal processing of spectroscopy data with secondary emphasis in system-on-chip implementation. His on-going research interests involve embedded processing using FPGAs and hardware acceleration of algorithms. In the fall of 2011, Dr. Foist joined the College of Engineering at California Baptist University. He is a U.S. Navy veteran who still strives to serve God and country. He has been happily married for 42 years and has four adult children and two grandchildren. Dr. John Butler, California Baptist University Dr. John Butler is currently an Assistant Professor in the department of Electrical and Computer En- gineering at California Baptist University. He received his B.S., M.S., and Ph.D. degrees in Electrical Engineering from the University of California, Riverside, in 2009, 2011, and 2014, respectively. In the fall of 2018 Dr. Butler joined the Gordon and Jill Bourns College of Engineering at California Baptist University as an Assistant Professor. Prior to this, he served as an Adjunct Professor since 2014. His re- search background includes nanoscale fabrication and characterization, particularly of magnetic thin films for data storage and logic devices. -

Low-Cost Industrial Controller Based on the Raspberry Pi Platform

Low-cost Industrial Controller based on the Raspberry Pi platform Gustavo Mendonça de Morais Rabelo Vieira Dissertation presented to the School of Technology and Management of Bragança to obtain the Master Degree in Industrial Engineering. Work oriented by: Professor PhD Paulo Leitão Professor PhD José Barbosa Professor MsC Ulisses da Graça Bragança 2018-2019 ii Low-cost Industrial Controller based on the Raspberry Pi platform Gustavo Mendonça de Morais Rabelo Vieira Dissertation presented to the School of Technology and Management of Bragança to obtain the Master Degree in Industrial Engineering. Work oriented by: Professor PhD Paulo Leitão Professor PhD José Barbosa Professor MsC Ulisses da Graça Bragança 2018-2019 iv Dedication Este trabalho é dedicado a mulher mais trabalhadora que conheço, a quem admiro muito e me inspira imensamente desde criança, minha querida e amada avó Terezinha Mendonça de Morais, singularmente importante em minha vida. À minha mãe Janaína, à minha tia Gildete, melhores amigas que sempre me ofereceram apoio a perseverar em minhas conquistas. Aos meus queridos irmãos mais novos, Lucas e Vitor que me orgulham pelas pessoas que estão se tornando e por toda a companhia que tive o prazer de desfrutar durante o nosso crescimento. v vi Acknowledgements Agradeço a todo o apoio e suporte que tive da minha família por me proporcionar a oportunidade de chegar até aqui. Aos meus professores orientadores José Barbosa e Paulo Leitão pela rica e experiente orientação. A todos os amigos, colegas e professores que foram sumariamente importantes para o sucesso da realização deste trabalho. vii viii Abstract The low-cost automation field exhibits the need of innovation both in terms of hardware and software. -

Manual EAGLE

EAGLE EASILY APPLICABLE GRAPHICAL LAYOUT EDITOR Manual Version4.1 ® 2ndEdition Copyright©2004CadSoftAllRightsReserved ThissoftwareanddocumentationarecopyrightedbyCadSoftComputer, Inc.,doingbusinessunderthetradenameEAGLE.Thesoftwareanddocu- mentationarelicensed,notsold,andmaybeusedorcopiedonlyinaccor- dancewiththeEAGLELicenseAgreementaccompanyingthesoftware and/orreprintedinthisdocument.Thissoftwareembodiesvaluabletradese- cretsproprietarytoCadSoftComputer,Inc. All trademarks referenced in this document are the property of their respec- tive owners. Specifications subject to change without notice. Copyright2004CadSoftComputer,Inc.Allrightsreservedworldwide No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electonic, mechanical, photocopy- ing, recording, scanning, digitizing, or otherwise, without the prior consense ofCadSoft. Printed in the United States of America. Howtoreachus OfficeHoursare: Mon-Thu: 9amto5pmEST Fri: 9amto4pmEST Phone: +1561274-8355 Fax: +1561274-8218 E-mail: [email protected] Web: http://www.cadsoftusa.com CadSoftComputer,Inc. 801SouthFederalHighway,Suite201 DelrayBeach,Florida33483-5185 U.S.A. EAGLELICENSEAGREEMENT Thisisalegalagreementbetweenyou,theenduser,andCadSoftComputer,Inc.,which marketssoftwareproductsunderthetrademarkEAGLE.CadSoftComputer,Inc.shallbe referredtointhisAgreementasCadSoft.IfyoudonotagreetothetermsofthisAgree- ment,promptlyreturnthediskettepackageandaccompanyingitems(includingwritten materialsandcontainers)totheplaceyouobtainedthemforafullrefund.USEOFTHIS -

Metadefender Core V4.17.3

MetaDefender Core v4.17.3 © 2020 OPSWAT, Inc. All rights reserved. OPSWAT®, MetadefenderTM and the OPSWAT logo are trademarks of OPSWAT, Inc. All other trademarks, trade names, service marks, service names, and images mentioned and/or used herein belong to their respective owners. Table of Contents About This Guide 13 Key Features of MetaDefender Core 14 1. Quick Start with MetaDefender Core 15 1.1. Installation 15 Operating system invariant initial steps 15 Basic setup 16 1.1.1. Configuration wizard 16 1.2. License Activation 21 1.3. Process Files with MetaDefender Core 21 2. Installing or Upgrading MetaDefender Core 22 2.1. Recommended System Configuration 22 Microsoft Windows Deployments 22 Unix Based Deployments 24 Data Retention 26 Custom Engines 27 Browser Requirements for the Metadefender Core Management Console 27 2.2. Installing MetaDefender 27 Installation 27 Installation notes 27 2.2.1. Installing Metadefender Core using command line 28 2.2.2. Installing Metadefender Core using the Install Wizard 31 2.3. Upgrading MetaDefender Core 31 Upgrading from MetaDefender Core 3.x 31 Upgrading from MetaDefender Core 4.x 31 2.4. MetaDefender Core Licensing 32 2.4.1. Activating Metadefender Licenses 32 2.4.2. Checking Your Metadefender Core License 37 2.5. Performance and Load Estimation 38 What to know before reading the results: Some factors that affect performance 38 How test results are calculated 39 Test Reports 39 Performance Report - Multi-Scanning On Linux 39 Performance Report - Multi-Scanning On Windows 43 2.6. Special installation options 46 Use RAMDISK for the tempdirectory 46 3. -

Altium Designer 14

Altium Designer 14 Altium Designer is the industry’s only electronics design system with a native 3D PCB engine backed by a unified design data model. Designers are presented with a complete and holistic picture of their electronics design, with real-time supply chain information, design costs and cost targets, live electrical and drafting rules checking, real-time PCB design constraint reporting and real-time views of the circuit board in 3D. Excellent visibility into the complete data model give the designer all the information needed to make good design decisions, on time. The design is synchronized between different domains. Schematics are tightly synchronized with the state of the PCB, FPGA pins. Signal definitions are synchronized with nets on the board, memory and port allocations in the embedded software platform can be synchronized to the hardware design. Board Design Altium Designer combines design capture, PCB layout, FPGA design, embedded software development and manufacturing files support in one unified application. Its single design database eliminates data translation and synchronization issues. Flexible library management including support for database and Vault driven libraries. Full hierarchical and multi-channel design entry with design reuse, and variant support. Logical and graphical comparison of different revisions in both schematic and PCB. Spice 3f5 compatible mixed signal simulation with support for popular pSpice extensions. pre- and post-layout signal integrity analysis. Advanced interactive routing incl. differential pair support, length tuning, impedance controlled routing. Native 3D Board Design with real time 3D collision check. Full 3D support for rigid-flex designs and automated linking and updating to, and from, mechanical CAD models. -

Getting Started in Kicad Getting Started in Kicad Ii

Getting Started in KiCad Getting Started in KiCad ii April 27, 2021 Getting Started in KiCad iii Contents 1 Introduction to KiCad 1 1.1 Downloading and installing KiCad ...................................... 2 1.1.1 Under GNU/Linux ........................................... 2 1.1.2 Under Apple macOS .......................................... 3 1.1.3 Under Windows ............................................ 3 1.2 Support ..................................................... 3 2 KiCad Workflow 4 2.1 Overview .................................................... 4 2.2 Forward and backward annotation ...................................... 6 3 Using KiCad 7 3.1 Shortcut keys .................................................. 7 3.1.1 Accelerator keys ............................................ 7 3.1.2 Hotkeys ................................................. 7 3.1.3 Example ................................................. 8 4 Draw electronic schematics 9 4.1 Using Eeschema ................................................. 9 4.2 Bus connections in KiCad ........................................... 21 5 Layout printed circuit boards 23 5.1 Using Pcbnew .................................................. 23 5.2 Generate Gerber files .............................................. 29 5.3 Using GerbView ................................................ 29 5.4 Automatically route with FreeRouter ..................................... 29 Getting Started in KiCad iv 6 Forward annotation in KiCad 31 7 Make schematic symbols in KiCad 33 7.1 Using Component