Training Autodesk EAGLE (English)

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Eagle Tutorial

EAGLE EASILY APPLICABLE GRAPHICAL LAYOUT EDITOR Tutorial Version 5 Schematic – Layout – Autorouter for Linux® Mac® Windows® CadSoft Computer www.cadsoftusa.com 6th Edition 005175100 Copyright © 2010 CadSoft Computer All Rights Reserved CadSoft Computer is a trading division of Newark Corporation. If you have any questions please feel free to contact us: USA and other countries: Phone: +1 (954) 237 0932 Fax: +1 (954) 237 0968 Internet: www.cadsoftusa.com Email: [email protected] Germany and other European countries: Phone: +49 (0)8635 6989-10 Hotline: +49 (0)8635 6989-30 Fax: +49 (0)8635 6989-40 Internet: www.cadsoft.de Email: [email protected] And remember that we offer a free hotline for our customers! Copyright 2010 CadSoft Computer. All rights reserved worldwide. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, scanning, digitizing, or otherwise, without the prior consense of CadSoft Computer. Printing this tutorial for your personal use is allowed. Windows is a registered trademark of Microsoft Corporation. Linux is a registered trademark of Linus Torvalds. Mac is a registered trademark of Apple Computer Inc. Table Of Contents 1 What to expect from this Tutorial...............................................................6 2 Features of EAGLE.......................................................................................7 System Requirements...............................................................................7 -

Experiences in Using Open Source Software for Teaching Electronic Engineering CAD

Experiences in Using Open Source Software for Teaching Electronic Engineering CAD Dr Simon Busbridge1 & Dr Deshinder Singh Gill School of Computing, Engineering and Mathematics, University of Brighton, Brighton BN2 4GJ [email protected] Abstract Embedded systems and simulation distinguish modern professional electronic engineering from that learnt at school. First year undergraduates typically have little appreciation of engineering software capabilities and file handling beyond elementary word processing. This year we expedited blended teaching through the experiential based learning process via open source engineering software. Students engaged with the entire electronic engineering product creation process from inception, performance simulation, printed circuit board design, manufacture and assembly, to cabinet design and complete finished product. Currently students learn software skills using a mixture of electronic and mechanical engineering software packages. Although these have professional capability they are not available off-campus and are sometimes surprisingly poor in simulating real world devices. In this paper we report use of LTspice, FreePCB and OpenSCAD for the learning and teaching of analogue electronics simulation and manufacture. Comparison of the software options, the type of tasks undertaken, examples of student assignments and outputs, and learning achieved are presented. Examples of assignment based learning, integration between the open source packages and difficulties encountered are discussed. Evaluation of student attitudes and responses to this method of learning and teaching are also discussed, and the educational advantages of using this approach compared to the use of commercial packages is highlighted. Introduction Most educational establishments use software for simulating or designing engineering. Most commercial packages come with an academic licence which restricts access to on-site computers. -

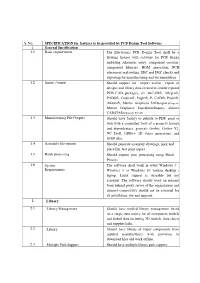

S. No. SPECIFICATION for Features to Be Provided by PCB Design Tool

S. No. SPECIFICATION for features to be provided by PCB Design Tool Software 1 General Specification 1.1 Basic requirements The Electronics PCB Design Tool shall be a floating license with software for PCB design including schematic entry, component creation, component libraries, BOM generation, PCB placement and routing, ERC and DRC checks and exporting for manufacturing and documentation. 1.2 Import / export Should support for import and/or export of designs and library data created in similar reputed PCB CAD packages, viz. OrCAD®, Allegro®, PADS®, Cadstar®, Eagle®, P- CAD®, Protel®, Altium®, Mentor Graphics® DxDesigner®(Import), Mentor Graphics® Expedition(Import), Zuken® CADSTAR®(Import), P-CAD 1.3 Manufacturing File Outputs Should have facility to publish to PDF, print or web with a controlled view of a project's history and dependencies, generate Gerber, Gerber X2, NC Drill, ODB++ 3D video animations, and STEP files. 1.4 Assembly file outputs Should generate assembly drawings, pick and place file, test point report. 1.5 Batch processing Should support post processing using Batch Process 1.6 System The software shall work in 64bit Windows 7 , Requirements Windows 8 or Windows 10 version desktop / laptop. Linux support is desirable but not essential. The software should work on intranet from behind proxy server of the organization and internet connectivity should not be essential for its installation, use and upgrade. 2 Library 2.1 Library Management Should have unified library management based on a single data source for all component models and linked data including 3D models, data sheets and supplier links. 2.2 Library Should have library of major components from reputed manufacturers with provision to download files and work offline. -

Elektronikentwicklung Unter Linux

Elektronikentwicklung unter Linux Clifford Wolf Clifford Wolf, 26. September 2010 http://www.clifford.at/ - p. 1 Einführung ● Behandelte Themen ● Unvollständigkeit Schaltungssimulation Leiterplattenentwurf und Schematic Einführung Compiler und Libraries Mathematik Mechanik Clifford Wolf, 26. September 2010 http://www.clifford.at/ - p. 2 Behandelte Themen Einführung ■ Schaltungssimulation ● Behandelte Themen ● Unvollständigkeit Schaltungssimulation ■ Leiterplattenentwurf und Schematic Leiterplattenentwurf und Schematic Compiler und Libraries ■ Compiler fuer embedded CPUs und ausgewaehlte Libraries Mathematik Mechanik ■ Mathematik ■ Mechanik Clifford Wolf, 26. September 2010 http://www.clifford.at/ - p. 3 Unvollständigkeit Einführung ■ Ich kann nur etwas über die Tools erzaehlen die ich selbst ● Behandelte Themen ● Unvollständigkeit verwende. Schaltungssimulation Leiterplattenentwurf und ■ Schematic Für Hinweise und Ergänzungen bin ich jederzeit offen und Compiler und Libraries dankbar. Mathematik Mechanik Clifford Wolf, 26. September 2010 http://www.clifford.at/ - p. 4 Einführung Schaltungssimulation ● QUCS ● GnuCap ● LTspice ● Java Circuit Simulator ● Icarus Verilog ● GTKWave Schaltungssimulation Leiterplattenentwurf und Schematic Compiler und Libraries Mathematik Mechanik Clifford Wolf, 26. September 2010 http://www.clifford.at/ - p. 5 QUCS Einführung http://qucs.sourceforge.net/ Schaltungssimulation ● QUCS ● GnuCap ■ Sehr sauber implementierter Simulator ● LTspice ● Java Circuit Simulator ● Icarus Verilog ● GTKWave ■ Gute GUI für Schematic-Entry -

Tutorial and Design of Printed Circuit Board ”Big Blinky”

Paper ID #31292 An Electronics Lab Project—Tutorial and Design of Printed Circuit Board ”big blinky” Dr. Rod Blaine Foist, California Baptist University Rod Foist Professor (and IEEE student club advisor), Electrical and Computer Engineering, Gordon & Jill Bourns College of Engineering, California Baptist University, [email protected]. Dr. Foist received his B.S. and M.S. degrees in Electrical Engineering from the University of Washington in 1982 and 1989, respectively. He earned his Ph.D. degree in Electrical and Computer Engineering from the University of British Columbia in 2011, specializing in signal processing of spectroscopy data with secondary emphasis in system-on-chip implementation. His on-going research interests involve embedded processing using FPGAs and hardware acceleration of algorithms. In the fall of 2011, Dr. Foist joined the College of Engineering at California Baptist University. He is a U.S. Navy veteran who still strives to serve God and country. He has been happily married for 42 years and has four adult children and two grandchildren. Dr. John Butler, California Baptist University Dr. John Butler is currently an Assistant Professor in the department of Electrical and Computer En- gineering at California Baptist University. He received his B.S., M.S., and Ph.D. degrees in Electrical Engineering from the University of California, Riverside, in 2009, 2011, and 2014, respectively. In the fall of 2018 Dr. Butler joined the Gordon and Jill Bourns College of Engineering at California Baptist University as an Assistant Professor. Prior to this, he served as an Adjunct Professor since 2014. His re- search background includes nanoscale fabrication and characterization, particularly of magnetic thin films for data storage and logic devices. -

Minor Changes and Bug Fixes

List of fixed bugs in DipTrace 4.1.3.1 if compared to 4.1.3.0 PCB Layout 1. If IPC-7351 models are used, STEP export does not work. 2. When entering text into table cells "Shift + U" works as a Hotkey. 3. When importing KiCad 5.1 files, SMD pads on the Bottom layer may be imported incorrectly. Schematics 1. When entering text into table cells "Shift + U" works as a Hotkey.. 2. Back Annotate does not update supplier information. List of fixed bugs in DipTrace 4.1.3.0 if compared to 4.1.2.0 General 1. Snap EDA: multiple clicks for page switching result in a long "freezing". PCB Layout 4. The panelization parameters are reset when opening a schematic file in the PCB Layout after starting. 5. D-shape pads are displayed incorrectly in the Mirror mode. 6. The Highlight Net for the Obround and D-shape pads is displayed incorrectly in the Mirror mode. 7. TrueType text is shifted in BOM HTML. 8. DXF with multilayer blocks is imported incorrectly 9. Export of arcs with a very small angle and extra-large radius to Gerber has been changed. 10. Chamfer of the corners of a rectangular board outline may result in incorrect formation of outlines in Gerber when panelizing with Edge Rails. 11. After changing any of the markings parameters for a group of selected objects, the marking for selected Mounting Hole and Fiducial may appear. 12. Dimension objects are not updated automatically after changing the shape dimensions in the shape properties. -

Ecebuntu - an Innovative and Multi-Purpose Educational Operating System for Electrical and Computer Engineering Undergraduate Courses

RESEARCH ARTICLE Electrica 2018; 18(2): 210-217 ECEbuntu - An Innovative and Multi-Purpose Educational Operating System for Electrical and Computer Engineering Undergraduate Courses Bilal Wajid1 , Ali Rıza Ekti2 , Mustafa Kamal AlShawaqfeh3 1Department of Electrical Engineering, University of Engineering and Technology, Lahore, Pakistan 2Department of Electrical-Electronics Engineering, Balıkesir University School of Engineering, Balıkesir, Turkey 3School of Electrical Engineering and Information Technology, German Jordanian University, Amman, Jordan Cite this article as: B. Wajid, A. R. Ekti, M. K. AlShawaqfeh, “ECEbuntu - An Innovative and Multi-Purpose Educational Operating System for Electrical and Computer Engineering Undergraduate Courses”, Electrica, vol. 18, no: 2, pp. 210-217, 2018. ABSTRACT ECEbuntu is a free, easily distributable, customized operating system based on Ubuntu 12.04 long term support (LTS) designed for electrical/electronic and computer engineering (ECE) students. ECEbuntu is aimed at universities and students as it represents a cohesive environment integrating more than 30 pre-installed software and packages all catering to undergraduate coursework offered in ECE and Computer Science (CS) programs. ECEbuntu supports a wide range of tools for programming, circuit analysis, printed circuit board design, mathematical and numerical analysis, network analysis, and RF and microwave transmitter design. ECEbuntu is free and effective alternative to the existing costly and copyrighted software packages. ECEbuntu attempts -

Manual EAGLE

EAGLE EASILY APPLICABLE GRAPHICAL LAYOUT EDITOR Manual Version4.1 ® 2ndEdition Copyright©2004CadSoftAllRightsReserved ThissoftwareanddocumentationarecopyrightedbyCadSoftComputer, Inc.,doingbusinessunderthetradenameEAGLE.Thesoftwareanddocu- mentationarelicensed,notsold,andmaybeusedorcopiedonlyinaccor- dancewiththeEAGLELicenseAgreementaccompanyingthesoftware and/orreprintedinthisdocument.Thissoftwareembodiesvaluabletradese- cretsproprietarytoCadSoftComputer,Inc. All trademarks referenced in this document are the property of their respec- tive owners. Specifications subject to change without notice. Copyright2004CadSoftComputer,Inc.Allrightsreservedworldwide No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electonic, mechanical, photocopy- ing, recording, scanning, digitizing, or otherwise, without the prior consense ofCadSoft. Printed in the United States of America. Howtoreachus OfficeHoursare: Mon-Thu: 9amto5pmEST Fri: 9amto4pmEST Phone: +1561274-8355 Fax: +1561274-8218 E-mail: [email protected] Web: http://www.cadsoftusa.com CadSoftComputer,Inc. 801SouthFederalHighway,Suite201 DelrayBeach,Florida33483-5185 U.S.A. EAGLELICENSEAGREEMENT Thisisalegalagreementbetweenyou,theenduser,andCadSoftComputer,Inc.,which marketssoftwareproductsunderthetrademarkEAGLE.CadSoftComputer,Inc.shallbe referredtointhisAgreementasCadSoft.IfyoudonotagreetothetermsofthisAgree- ment,promptlyreturnthediskettepackageandaccompanyingitems(includingwritten materialsandcontainers)totheplaceyouobtainedthemforafullrefund.USEOFTHIS -

Altium Designer 14

Altium Designer 14 Altium Designer is the industry’s only electronics design system with a native 3D PCB engine backed by a unified design data model. Designers are presented with a complete and holistic picture of their electronics design, with real-time supply chain information, design costs and cost targets, live electrical and drafting rules checking, real-time PCB design constraint reporting and real-time views of the circuit board in 3D. Excellent visibility into the complete data model give the designer all the information needed to make good design decisions, on time. The design is synchronized between different domains. Schematics are tightly synchronized with the state of the PCB, FPGA pins. Signal definitions are synchronized with nets on the board, memory and port allocations in the embedded software platform can be synchronized to the hardware design. Board Design Altium Designer combines design capture, PCB layout, FPGA design, embedded software development and manufacturing files support in one unified application. Its single design database eliminates data translation and synchronization issues. Flexible library management including support for database and Vault driven libraries. Full hierarchical and multi-channel design entry with design reuse, and variant support. Logical and graphical comparison of different revisions in both schematic and PCB. Spice 3f5 compatible mixed signal simulation with support for popular pSpice extensions. pre- and post-layout signal integrity analysis. Advanced interactive routing incl. differential pair support, length tuning, impedance controlled routing. Native 3D Board Design with real time 3D collision check. Full 3D support for rigid-flex designs and automated linking and updating to, and from, mechanical CAD models. -

How to Make an Eight Bit Computer and Save the World!

How to Make an Eight Bit Computer and Save the World! Braddock Gaskill Humane Informatics [email protected] SGVLUG 8 April 2010 Overview -Present Device -Overview -Goals -Device Demo -Functional Requirements -AVR Open Ecosystem - Uzebox -AVR Open Ecosystem - Arduino -AVR Open Ecosystem - gcc, avr-libc, avrdude -AVR Open Ecosystem - avrfreaks, uzebox forums, etc -Video Requirement - Tellymate -SD Card Requirement - Wave Shield/Uzebox -FAT Requirement - Petite FatFS -USB Desirement - V-USB -Schematic (Eagle, GEDA, gschem, PCB Artist) -Layout -Bill of Materials -PCB Fabrication -Assembly -Pricing SGVLUG 8 April 2010 Talk Overview Today's Audience Independently Wealthy Philanphrapists Non-Governmental Organizations, UN, etc DoD Civil Affairs, USAID Geeks interested in Playing with Microcontrollers Building & Fabricating things Open Source Tools and Hardware Today's Talk Overview and demo of device Survey of AVR Open Source Hardware Survey of AVR Open Source Tools Walk through of design and design tools Walk through of fabrication and manufacturing SGVLUG 8 April 2010 Bridging TV/Internet Gap SGVLUG 8 April 2010 Bridging TV/Internet Gap Market >700 million SGVLUG 8 April 2010 Pitch 2GB SD Card = ~5,000 books or better part of Wikipedia Humane Reader device turns any TV set into an e-book/wikipedia reader. Production Cost approx $20 (incl SD Card) SGVLUG 8 April 2010 Value Proposition The Humane Reader can provide a virtual library to any developing world school or individual with electrical power for less than the cost of a single textbook. SGVLUG 8 April 2010 Secondary Goals Goal: Create an extendable, hackable, 8-bit general computing platform both for first through third world developers and experimenters. -

Version 9.5 Manual

EASILY APPLICABLE GRAPHICAL LAYOUT EDITOR Version 9.5 Manual 90925951 Copyright © 2019 Autodesk All Rights Reserved This software and documentation are copyrighted by Autodesk, doing business under the trade name EAGLE. The software and documentation are licensed, not sold, and may be used or copied only in accordance with the EAGLE License Agreement accompanying the software and/or reprinted in this document. This software embodies valuable trade secrets proprietary to Autodesk. Specifications subject to change without notice. © Copyright 1988-2019 Autodesk. All rights reserved worldwide. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, scanning, digitizing, or otherwise, without the prior consent of Autodesk. Printing this manual for your personal use is allowed. Book compiled by Richard Hammerl since 1998. Windows is a registered trademark of Microsoft Corporation. Linux is a registered trademark of Linus Torvalds. Mac is a registered trademark of Apple Computer, Inc. Table of Contents Chapter 1 Introduction...............................................................25 1.1 What is in this Manual?................................................................25 1.2 Important Changes since Version 8..............................................26 Managed Folders for sharing libraries..........................................26 New GROUP Handling.................................................................26 -

Yuniel Freire Hernández.Pdf

Universidad Central “Marta Abreu” de Las Villas Facultad de Ingeniería Eléctrica Departamento de Telecomunicaciones y Electrónica TRABAJO DE DIPLOMA Simulación de Circuitos Digitales con Software Libre Autor: Yuniel Freire Hernández Tutor: Ing. Erisbel Orozco Crespo Santa Clara 2012 Universidad Central “Marta Abreu” de Las Villas Facultad de Ingeniería Eléctrica Departamento de Telecomunicaciones y Electrónica TRABAJO DE DIPLOMA Simulación de Circuitos Digitales con Software Libre Autor: Yuniel Freire Hernández Tutor: Ing. Erisbel Orozco Crespo Profesor, Dpto. Telec. Y Electrónica Santa Clara 2012 Hago constar que el presente trabajo de diploma fue realizado en la Universidad Central “Marta Abreu” de Las Villas como parte de la culminación de estudios de la especialidad de Ingeniería en Telecomunicaciones y Electrónica, autorizando a que el mismo sea utilizado por la Institución, para los fines que estime conveniente, tanto de forma parcial como total y que además no podrá ser presentado en eventos, ni publicados sin autorización de la Universidad. Firma del Autor Los abajo firmantes certificamos que el presente trabajo ha sido realizado según acuerdo de la dirección de nuestro centro y el mismo cumple con los requisitos que debe tener un trabajo de esta envergadura referido a la temática señalada. Firma del Tutor Firma del Jefe de Departamento donde se defiende el trabajo Firma del Responsable de Información Científico-Técnica PENSAMIENTO No fracasé, sólo descubrí 999 maneras de cómo no hacer una bombilla. Thomas Alva Edison AGRADECIMIENTOS A todos los profesores que brindaron sus conocimientos para mi formación. A mi tutor por su paciencia, esmero y dedicación. A mis amigos y compañeros por resistirme.