PCBNEW Wishlists, Blueprints, Design and Implementation Notes

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

The Leader in Advanced .Dwg Technology

October 17 2017 TEIGHA® DRAWINGS The leader in advanced .dwg technology www.opendesign.com Copyright © 2017 Open Design Alliance, All Rights Reserved BACKGROUND Teigha Drawings is a stand-alone independent SDK available for developers working with the .dwg, .dxf, and .dgn file formats. It was developed by Open Design Alliance (ODA), a technology consortium that has been providing interoperability tools for the engineering software industry since 1998. BUSINESS OVERVIEW INTRODUCTION ODA has a long history of experience with the .dwg file format, dating back to 1998. Our software has kept the .dwg file format open and universally accessible for the past 20 years. Today, in addition to providing interopera- bility, we are leveraging our vast experience with .dwg to make it a tool of choice for modern application development. INDUSTRY-PROVEN TECHNOLOGY Teigha Drawings has been powering thousands of mission critical engi- neering applications for more than a decade. It is a mature, high-quality and trusted solution for building CAD applications. ACCELERATE TIME-TO-MARKET In addition to turn-key support for .dwg and .dgn files, Teigha Drawings includes components for a variety of other common engineering tasks including version control, visualization and publishing. Using Teigha Drawings as a base, you can build more sophisticated applications in less time, using fewer resources. ATTRACTIVE LICENSING Teigha Drawings is offered under a fixed fee license with no royalties for cost-effective deployment. PRODUCT PORTFOLIO SUPPORTED FILE VERSIONS .dwg/.dxf -

PLM Weekly Summary Editor: Cimdata News Team 15 January 2021 Contents Cimdata News

PLM Weekly Summary Editor: CIMdata News Team 15 January 2021 Contents CIMdata News ............................................................................................................................................ 2 An Enterprise Digital Transformation Platform – a CIMdata Commentary......................................................2 Aras’ Cloud Strategy – a CIMdata Blog Post ....................................................................................................5 CIMdata Announces its 2021 PLM Market & Industry Forum Series ..............................................................6 CIMdata to Host a Free Webinar on CAD Trends ............................................................................................7 NLign Analytics “Structural Lifecycle Digital Environment” Enables Model-Driven Product Quality – a CIMdata Commentary .......................................................................................................................................8 PTC’s Cloud Strategy – a CIMdata Blog Post ................................................................................................. 13 Acquisitions .............................................................................................................................................. 14 Accenture Acquires Real Protect, Brazil-Based Information Security Company ........................................... 14 Atos to acquire In Fidem to reinforce its cybersecurity position in the North American market .................... 15 Planview -

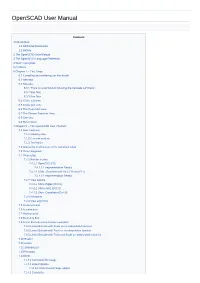

Openscad User Manual (PDF)

OpenSCAD User Manual Contents 1 Introduction 1.1 Additional Resources 1.2 History 2 The OpenSCAD User Manual 3 The OpenSCAD Language Reference 4 Work in progress 5 Contents 6 Chapter 1 -- First Steps 6.1 Compiling and rendering our first model 6.2 See also 6.3 See also 6.3.1 There is no semicolon following the translate command 6.3.2 See Also 6.3.3 See Also 6.4 CGAL surfaces 6.5 CGAL grid only 6.6 The OpenCSG view 6.7 The Thrown Together View 6.8 See also 6.9 References 7 Chapter 2 -- The OpenSCAD User Interface 7.1 User Interface 7.1.1 Viewing area 7.1.2 Console window 7.1.3 Text editor 7.2 Interactive modification of the numerical value 7.3 View navigation 7.4 View setup 7.4.1 Render modes 7.4.1.1 OpenCSG (F9) 7.4.1.1.1 Implementation Details 7.4.1.2 CGAL (Surfaces and Grid, F10 and F11) 7.4.1.2.1 Implementation Details 7.4.2 View options 7.4.2.1 Show Edges (Ctrl+1) 7.4.2.2 Show Axes (Ctrl+2) 7.4.2.3 Show Crosshairs (Ctrl+3) 7.4.3 Animation 7.4.4 View alignment 7.5 Dodecahedron 7.6 Icosahedron 7.7 Half-pyramid 7.8 Bounding Box 7.9 Linear Extrude extended use examples 7.9.1 Linear Extrude with Scale as an interpolated function 7.9.2 Linear Extrude with Twist as an interpolated function 7.9.3 Linear Extrude with Twist and Scale as interpolated functions 7.10 Rocket 7.11 Horns 7.12 Strandbeest 7.13 Previous 7.14 Next 7.14.1 Command line usage 7.14.2 Export options 7.14.2.1 Camera and image output 7.14.3 Constants 7.14.4 Command to build required files 7.14.5 Processing all .scad files in a folder 7.14.6 Makefile example 7.14.6.1 Automatic -

Dissertação De Mestrado

UNIVERSIDADE FEDERAL DE MINAS GERAIS PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA MECÂNICA “DESENVOLVIMENTO DE UM PROGRAMA DIDÁTICO COMPUTACIONAL DESTINADO À GERAÇÃO DE CÓDIGOS DE COMANDO NUMÉRICO A PARTIR DE MODELOS 3D OBTIDOS EM PLATAFORMA CAD CONSIDERANDO A TÉCNICA PROTOTIPAGEM RÁPIDA” RAFAEL JUAN COSTA DE MIRANDA Belo Horizonte, 26 de fevereiro de 2009 Rafael Juan Costa de Miranda “DESENVOLVIMENTO DE UM PROGRAMA DIDÁTICO COMPUTACIONAL DESTINADO À GERAÇÃO DE CÓDIGOS DE COMANDO NUMÉRICO A PARTIR DE MODELOS 3D OBTIDOS EM PLATAFORMA CAD CONSIDERANDO A TÉCNICA PROTOTIPAGEM RÁPIDA” Dissertação apresentada ao Programa de Pós-Graduação em Engenharia Mecânica da Universidade Federal de Minas Gerais, como requisito parcial à obtenção do título de Mestre em Engenharia Mecânica. Área de concentração: Projeto Mecânico Orientador: Prof. Antônio Eustáquio de Melo Pertence Universidade Federal de Minas Gerais Belo Horizonte Escola de Engenharia da UFMG 2009 Universidade Federal de Minas Gerais Programa de Pós-Graduação em Engenharia Mecânica Av. Antônio Carlos, 6627 - Pampulha - 31.270-901 - Belo Horizonte – MG Tel.: +55 31 3499-5145 - Fax.: +55 31 3443-3783 www.demec.ufmg.br - E-mail: [email protected] “DESENVOLVIMENTO DE UM PROGRAMA DIDÁTICO COMPUTACIONAL DESTINADO À GERAÇÃO DE CÓDIGOS DE COMANDO NUMÉRICO A PARTIR DE MODELOS 3D OBTIDOS EM PLATAFORMA CAD CONSIDERANDO A TÉCNICA PROTOTIPAGEM RÁPIDA” RAFAEL JUAN COSTA DE MIRANDA Dissertação/ defendida e aprovada em 26 de fevereiro de 2009, pela Banca Examinadora designada pelo Colegiado do Programa de Pós-Graduação em Engenharia Mecânica da Universidade Federal de Minas Gerais, como parte dos requisitos necessários à obtenção do título de "Mestre em Engenharia Mecânica", na área de concentração de "Projeto Mecânico". -

Experiences in Using Open Source Software for Teaching Electronic Engineering CAD

Experiences in Using Open Source Software for Teaching Electronic Engineering CAD Dr Simon Busbridge1 & Dr Deshinder Singh Gill School of Computing, Engineering and Mathematics, University of Brighton, Brighton BN2 4GJ [email protected] Abstract Embedded systems and simulation distinguish modern professional electronic engineering from that learnt at school. First year undergraduates typically have little appreciation of engineering software capabilities and file handling beyond elementary word processing. This year we expedited blended teaching through the experiential based learning process via open source engineering software. Students engaged with the entire electronic engineering product creation process from inception, performance simulation, printed circuit board design, manufacture and assembly, to cabinet design and complete finished product. Currently students learn software skills using a mixture of electronic and mechanical engineering software packages. Although these have professional capability they are not available off-campus and are sometimes surprisingly poor in simulating real world devices. In this paper we report use of LTspice, FreePCB and OpenSCAD for the learning and teaching of analogue electronics simulation and manufacture. Comparison of the software options, the type of tasks undertaken, examples of student assignments and outputs, and learning achieved are presented. Examples of assignment based learning, integration between the open source packages and difficulties encountered are discussed. Evaluation of student attitudes and responses to this method of learning and teaching are also discussed, and the educational advantages of using this approach compared to the use of commercial packages is highlighted. Introduction Most educational establishments use software for simulating or designing engineering. Most commercial packages come with an academic licence which restricts access to on-site computers. -

IDF Exporter IDF Exporter Ii

IDF Exporter IDF Exporter ii April 27, 2021 IDF Exporter iii Contents 1 Introduction to the IDFv3 exporter 2 2 Specifying component models for use by the exporter 2 3 Creating a component outline file 4 4 Guidelines for creating outlines 6 4.1 Package naming ................................................ 6 4.2 Comments .................................................... 6 4.3 Geometry and Part Number entries ...................................... 7 4.4 Pin orientation and positioning ........................................ 7 4.5 Tips on dimensions ............................................... 8 5 IDF Component Outline Tools 8 5.1 idfcyl ....................................................... 9 5.2 idfrect ...................................................... 10 5.3 dxf2idf ...................................................... 11 6 idf2vrml 12 IDF Exporter 1 / 12 Reference manual Copyright This document is Copyright © 2014-2015 by it’s contributors as listed below. You may distribute it and/or modify it under the terms of either the GNU General Public License (http://www.gnu.org/licenses/gpl.html), version 3 or later, or the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0/), version 3.0 or later. All trademarks within this guide belong to their legitimate owners. Contributors Cirilo Bernardo Feedback Please direct any bug reports, suggestions or new versions to here: • About KiCad document: https://gitlab.com/kicad/services/kicad-doc/issues • About KiCad software: https://gitlab.com/kicad/code/kicad/issues • About KiCad software i18n: https://gitlab.com/kicad/code/kicad-i18n/issues Publication date and software version Published on January 26, 2014. IDF Exporter 2 / 12 1 Introduction to the IDFv3 exporter The IDF exporter exports an IDFv3 1 compliant board (.emn) and library (.emp) file for communicating mechanical dimensions to a mechanical CAD package. -

Openscad User Manual/Print Version Table of Contents Introduction First

OpenSCAD User Manual/Print version Table of Contents 1. Introduction 2. First Steps 3. The OpenSCAD User Interface 4. The OpenSCAD Language 1. General 2. Mathematical Operators 3. Mathematical Functions 4. String Functions 5. Primitive Solids 6. Transformations 7. Conditional and Iterator Functions 8. CSG Modelling 9. Modifier Characters 10. Modules 11. Include Statement 12. Other Language Feature 5. Using the 2D Subsystem 1. 2D Primitives 2. 3D to 2D Projection 3. 2D to 2D Extrusion 4. DXF Extrusion 5. Other 2D formats 6. STL Import and Export 1. STL Import 2. STL Export 7. Commented Example Projects 8. Using OpenSCAD in a command line environment 9. Building OpenSCAD from Sources 1. Building on Linux/UNIX 2. Cross-compiling for Windows on Linux or Mac OS X 3. Building on Windows 4. Building on Mac OS X 10. Libraries 11. Glossary 12. Index Introduction OpenSCAD is a software for creating solid 3D CAD objects. It is free software (http://www.gnu.org/philosophy/free-sw.html) and available for GNU/Linux (http://www.gnu.org/) , MS Windows and Apple OS X. Unlike most free software for creating 3D models (such as the well-known application Blender (http://www.blender.org/) ), OpenSCAD does not focus on the artistic aspects of 3D modelling, but instead focuses on the CAD aspects. So it might be the application you are looking for when you are planning to create 3D models of machine parts, but probably is not what you are looking for when you are more interested in creating computer- animated movies. OpenSCAD is not an interactive modeller. -

Turbocad Pro 17 Autocad 2010 Comparisons-03-23

T ur b T oCA ur A b u oCA D toC P TurboCAD vs. AutoCAD ro AD D Comparative Matrix P Pla 20 ro ti 1 1 n 0 7 um 1 7 Suggested Retail Price $1,295 $1,495 $3,995 U SABILITY & INTERFACE Command Line Fully Customizable User Interface and Preferences Advanced Handle-Based Editing Drawing Performance - (TurboCAD includes Redway3d drawing engine) Draw Order by Layer Explode Viewports Layer Filters SNAP Prioritization True Units Retained between Drawings with Different Unit Settings Drawing Compare (1) 2D Drafting and Editing Auto Tools (for Scaling, Sizing, Positioning, Rotating, and Movement) 2D Drawing, Editing, and Modifying Bezier Curves Transparent and Bitmap Fills CTB Print Style Support Drafting and Detailing Palette - create associative sections and cut planes Index Color Support Layer Properties Manager Smart and Quick Dimension Tools Xclip Support 3D Modeling 3D Solid Modeling and Editing 3D Terrain Modeling 3D Shelling, Lofting and Surfaces 3D Deformable Modeling 3D Pattern Copy Tools Quick Pull Tool Parametric Part Maker and Manager History Tree with Editor Mechanical 2D Geometric and Dimension Constraints Adhesive Symbol Tool (fully parametric) Branched Lofting Face-to-Face Lofting Gear Contour Tool Geometric Tolerance Tool Surface Roughness and Weld Symbols Page 1 of 2 T ur b T oCA ur A b u oCA D toC P TurboCAD vs. AutoCAD ro AD D Comparative Matrix P Pla 20 ro ti 1 1 n 0 7 um 1 7 Architectural Intelligent (Parametric) Attribute-rich, Architectural Objects (2) Walls (Self-Healing; -

Elektronikentwicklung Unter Linux

Elektronikentwicklung unter Linux Clifford Wolf Clifford Wolf, 26. September 2010 http://www.clifford.at/ - p. 1 Einführung ● Behandelte Themen ● Unvollständigkeit Schaltungssimulation Leiterplattenentwurf und Schematic Einführung Compiler und Libraries Mathematik Mechanik Clifford Wolf, 26. September 2010 http://www.clifford.at/ - p. 2 Behandelte Themen Einführung ■ Schaltungssimulation ● Behandelte Themen ● Unvollständigkeit Schaltungssimulation ■ Leiterplattenentwurf und Schematic Leiterplattenentwurf und Schematic Compiler und Libraries ■ Compiler fuer embedded CPUs und ausgewaehlte Libraries Mathematik Mechanik ■ Mathematik ■ Mechanik Clifford Wolf, 26. September 2010 http://www.clifford.at/ - p. 3 Unvollständigkeit Einführung ■ Ich kann nur etwas über die Tools erzaehlen die ich selbst ● Behandelte Themen ● Unvollständigkeit verwende. Schaltungssimulation Leiterplattenentwurf und ■ Schematic Für Hinweise und Ergänzungen bin ich jederzeit offen und Compiler und Libraries dankbar. Mathematik Mechanik Clifford Wolf, 26. September 2010 http://www.clifford.at/ - p. 4 Einführung Schaltungssimulation ● QUCS ● GnuCap ● LTspice ● Java Circuit Simulator ● Icarus Verilog ● GTKWave Schaltungssimulation Leiterplattenentwurf und Schematic Compiler und Libraries Mathematik Mechanik Clifford Wolf, 26. September 2010 http://www.clifford.at/ - p. 5 QUCS Einführung http://qucs.sourceforge.net/ Schaltungssimulation ● QUCS ● GnuCap ■ Sehr sauber implementierter Simulator ● LTspice ● Java Circuit Simulator ● Icarus Verilog ● GTKWave ■ Gute GUI für Schematic-Entry -

The Role of Openbim® in Better Data Exchange for AEC Project Teams the ROLE of OPENBIM® in BETTER DATA EXCHANGE for AEC PROJECT TEAMS 2

The role of openBIM® in better data exchange for AEC project teams THE ROLE OF OPENBIM® IN BETTER DATA EXCHANGE FOR AEC PROJECT TEAMS 2 Introduction Project Data File type Architectural Model RVT, RFA, SKP, 3ds The success of complex, multi-stakeholder Architecture, Engineering and Construction (AEC) projects relies on smooth Structural Model IFC, CIS/2, RVT collaboration and information sharing throughout the project lifecycle, often across different disciplines and software. The costs 3D Printing STL, OBJ of inadequate interoperability to project teams, according to one analysis of capital facilities projects in the United States, approaches CAD Data DXF, DWG, ACIS SAT 17 billion annually, affecting all project stakeholders.¹ A more recent GIS Data SHP, KMZ, WFS, GML study by FMI and Autodesk’s portfolio company Plangrid found that 52% of rework could be prevented by better data and communication, and that Civil Engineering LandXML, DWG, DGN, CityGML in an average week, construction employees spend 14 hours (around 35% of their time) looking for project data, dealing with rework and/or handling Cost Estimating XLSX, ODBC conflict resolution.² Visualisation Models FBX, SKP, NWD, RVT In the AEC industry, many hands and many tools bring building and infrastructure projects to realisation. Across architects, engineers, contractors, fabricators and Handover to Facilities Management COBie, IFC, XLSX facility managers: inadequate interoperability leads to delays and rework, with ramifications that can reverberate throughout the entirety of the project lifecycle. Scheduling Data P3, MPP Over the last two decades, a strong point of alignment in the AEC industry has been in the development and adoption of the openBIM® collaborative process Energy Analysis IFC, gbXML to improve interoperability and collaboration for building and infrastructure projects. -

Kustannustehokkaat Cad, Fem Ja Cam -Ohjelmat Tutkimus Saatavilla Olevista Ohjelmista Tammikuussa 2018

OULUN YLIOPISTON KERTTU SAALASTI INSTITUUTIN JULKAISUJA 6/2018 Kustannustehokkaat Cad, Fem ja Cam -ohjelmat Tutkimus saatavilla olevista ohjelmista tammikuussa 2018 Terho Iso-Junno Tulevaisuuden tuotantoteknologiat FMT-tutkimusryhmä Terho Iso-Junno KUSTANNUSTEHOKKAAT CAD, FEM JA CAM -OHJELMAT Tutkimus saatavilla olevista ohjelmista tammikuussa 2018 OULUN YLIOPISTO Kerttu Saalasti Instituutin julkaisuja Tulevaisuuden tuotantoteknologiat (FMT) -tutkimusryhmä ISBN 978-952-62-2018-5 (painettu) ISBN 978-952-62-2019-2 (elektroninen) ISSN 2489-3501 (painettu) Terho Iso-Junno Kustannustehokkaat CAD, FEM ja CAM -ohjelmat. Tutkimus saatavilla olevista ohjelmista tammikuussa 2018. Oulun yliopiston Kerttu Saalasti Instituutti, Tulevaisuuden tuotantoteknologiat (FMT) -tutkimusryhmä Oulun yliopiston Kerttu Saalasti Instituutin julkaisuja 6/2018 Nivala Tiivistelmä Nykyaikaisessa tuotteen suunnittelussa ja valmistuksessa tietokoneohjelmat ovat avainasemassa olevia työkaluja. Kaupallisten ohjelmien lisenssihinnat voivat nousta korkeiksi ja olla hankinnan esteenä etenkin aloittelevilla yrityksillä. Tässä tutkimuk- sessa on kartoitettu kustannuksiltaan edullisia CAD, FEM ja CAM -ohjelmia, joita voisi käyttää yritystoiminnassa. CAD-ohjelmien puolella perinteisille 2D CAD-ohjelmille löytyy useita hyviä vaih- toehtoja. LibreCAD ja QCAD ovat helppokäyttöisiä ohjelmia perustason piirtämiseen. Solid Edge 2D Drafting on erittäin monipuolinen täysiverinen 2D CAD, joka perustuu parametriseen piirtämiseen. 3D CAD-ohjelmien puolella tarjonta on tasoltaan vaihtelevaa. -

Industrial Circuit Board Design and Microprocessor Programming Bachelor of Science Thesis in Mechatronics

Industrial circuit board design and microprocessor programming Bachelor of Science thesis in Mechatronics FREDRIK HÖGBERG Department of Signals and Systems CHALMERS UNIVERSITY OF TECHNOLOGY Gothenburg, Sweden 2017 REPORT NO. XXXX XXXX Industrial circuit boar! design and %icroprocessor pro$ram%in$ FREDRIK HÖGBERG Depart%ent of Signal and S'ste%s CH)*MERS UNI,ERSIT- OF TE(HNO*OG- Gothenbur$, S/eden 2017 Industrial circuit board design and microprocessor pro$ra%%in$ FREDRIK HÖGBERG FREDRIK HÖGBERG, 2017 Technical report no xxxx544 Depart%ent of Signals and S'ste%s Chal%ers +ni6ersit' of Technolo$' SE-412 96 G;tebor$ S/eden Telephone + 46 (0)31-772 1000 (o6er5 Hot Screen 2000 is an industrial heat press machine that can be used to attach screen prints on clothin$. This thesis will go in to details on ho/ the circuit board and pro$ra% was ma!e for this %achine. Chal%ers Reproservice G;tebor$. S/eden 2017 CHALMERS Signals and Systems, Bachelor@s Thesis XXXX5XX I Abstract The %ain obAect of this proAect is to design and %aBe circuitr' to control a industrial heat press %achine. The circuitr' consist of a 0 la'er boar! containin$ a %icro controller. displa' %odule. )( DC module. te%perature controller and electronics to control electromechanical devices. The fra%e of reference /ill $o through the basics steps in designin$ and %anufacturin$ electrical circ"itry /ith digital and analo$ technolo$y and explain the basics of the most com%on electrical components use! in circuitr' toda'. The fra%e of reference /ill also sho/ ho/ to create sche%atic and circuit design "sin$ Ki()D and ho/ to pro$ra% a Microchi& %icroprocessor in the C pro$ra%ing lan$"a$e.