Tutorial and Design of Printed Circuit Board ”Big Blinky”

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Using Net-Software in Design Education

INTERNATIONAL ENGINEERING AND PRODUCT DESIGN EDUCATION CONFERENCE 2-3 SEPTEMBER 2004 DELFT THE NETHERLANDS USING NET-SOFTWARE IN DESIGN EDUCATION Chris Baelus and Guido De Grande ABSTRACT In the early stages of the design process three major activities are involved: designing the concept, resolving the observed critical aspects and modifying the concept as a result of the previous step. This is a circular and iterative process until the final concept is ready for the detailed design phase. It is the purpose of every design method to minimize the total design time and produce well elaborated design concepts. The use of specialized software is of invaluable help in this attempt to reduce design time. A lot of different software is available on the Internet as downloadable freeware, shareware or demo versions. Most of this software has reduced capabilities; however, many software is excellent for educational purposes. We will call this software “Internet Software” or “net-software”. In this presentation two topics with respect to net-software will be discussed: 1. criteria for choosing net-software for educational purposes, and 2. the implementation of net-software in the new bachelor-master curriculum at the Higher Institute of Integrated Product Development (HIIPO) in Antwerp. A major activity in designing products is the early verification of the product concept with respect to structural, thermal and geometrical integrity. This typical verification net-software can be found in different flavours: for different applications, in different levels and with different user interfaces. Finding easy-to-use and efficient net-software is a rather straightforward task, integrating the software in the curriculum is a more difficult task. -

Eagle Tutorial

EAGLE EASILY APPLICABLE GRAPHICAL LAYOUT EDITOR Tutorial Version 5 Schematic – Layout – Autorouter for Linux® Mac® Windows® CadSoft Computer www.cadsoftusa.com 6th Edition 005175100 Copyright © 2010 CadSoft Computer All Rights Reserved CadSoft Computer is a trading division of Newark Corporation. If you have any questions please feel free to contact us: USA and other countries: Phone: +1 (954) 237 0932 Fax: +1 (954) 237 0968 Internet: www.cadsoftusa.com Email: [email protected] Germany and other European countries: Phone: +49 (0)8635 6989-10 Hotline: +49 (0)8635 6989-30 Fax: +49 (0)8635 6989-40 Internet: www.cadsoft.de Email: [email protected] And remember that we offer a free hotline for our customers! Copyright 2010 CadSoft Computer. All rights reserved worldwide. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, scanning, digitizing, or otherwise, without the prior consense of CadSoft Computer. Printing this tutorial for your personal use is allowed. Windows is a registered trademark of Microsoft Corporation. Linux is a registered trademark of Linus Torvalds. Mac is a registered trademark of Apple Computer Inc. Table Of Contents 1 What to expect from this Tutorial...............................................................6 2 Features of EAGLE.......................................................................................7 System Requirements...............................................................................7 -

Metadefender Core V4.12.2

MetaDefender Core v4.12.2 © 2018 OPSWAT, Inc. All rights reserved. OPSWAT®, MetadefenderTM and the OPSWAT logo are trademarks of OPSWAT, Inc. All other trademarks, trade names, service marks, service names, and images mentioned and/or used herein belong to their respective owners. Table of Contents About This Guide 13 Key Features of Metadefender Core 14 1. Quick Start with Metadefender Core 15 1.1. Installation 15 Operating system invariant initial steps 15 Basic setup 16 1.1.1. Configuration wizard 16 1.2. License Activation 21 1.3. Scan Files with Metadefender Core 21 2. Installing or Upgrading Metadefender Core 22 2.1. Recommended System Requirements 22 System Requirements For Server 22 Browser Requirements for the Metadefender Core Management Console 24 2.2. Installing Metadefender 25 Installation 25 Installation notes 25 2.2.1. Installing Metadefender Core using command line 26 2.2.2. Installing Metadefender Core using the Install Wizard 27 2.3. Upgrading MetaDefender Core 27 Upgrading from MetaDefender Core 3.x 27 Upgrading from MetaDefender Core 4.x 28 2.4. Metadefender Core Licensing 28 2.4.1. Activating Metadefender Licenses 28 2.4.2. Checking Your Metadefender Core License 35 2.5. Performance and Load Estimation 36 What to know before reading the results: Some factors that affect performance 36 How test results are calculated 37 Test Reports 37 Performance Report - Multi-Scanning On Linux 37 Performance Report - Multi-Scanning On Windows 41 2.6. Special installation options 46 Use RAMDISK for the tempdirectory 46 3. Configuring Metadefender Core 50 3.1. Management Console 50 3.2. -

Altium's Journey and Its Vision of Industry Transformation

A Winning Strategy for Value-Creation ALTIUM’S JOURNEY AND ITS VISION OF INDUSTRY TRANSFORMATION 18 June 2021 Agenda 1 Altium’s Journey of Transformation 2 Uniqueness of Altium in the Engineering Software Ecosystem 3 Altium’s Confidence in its Ability to Execute 4 Our Flight Path to Dominance Outstanding Value-Creation Track-Record Over Time ALU Set in 2019 and confident of achieving $500M * Stock Price Revenue Target Set in 2016 and fell short with COVID, $189M ** Delivering Value for our Shareholders $200M is a Hallmark of Altium… Revenue Target • A history of setting and over-achieving Set in 2014 and overachieved, $110M $100M aggressive long-term financial targets Revenue Target • Eight consecutive years of double-digit revenue growth & expanding margin ? • Focused execution with the “ingenuity of and” A$41.60 delivering strong operating leverage A$10.15 • Transparency for stakeholders and all-in reporting (no capitalization of R&D expenses) A$4.36 • Value creation at every stage from leadership to dominance to industry transformation A$0.76 Performing Leading Dominating Transforming 2012 2015 2017 2020 2025 * The target revenue of $500M may include 10-20% from future acquisitions. 3 ** Three months out analysts’ consensus pointed to a revenue target of $208M for FY2020 Pursuing Dominance and Transformation from a Position of Strength Financial Altium Designer Altium 365 Performance Dominance Adoption Altium is the fastest growing EDA company Altium Designer is the most widespread The world’s first digital platform for with 8 consecutive -

Circuitmaker 2000 (The Symbol Will Be Replaced by a Rectangle)

CircuitMaker® 2000 the virtual electronics lab™ CircuitMaker User Manual advanced schematic capture mixed analog/digital simulation Revision A Software, documentation and related materials: Copyright © 1988-2000 Protel International Limited. All Rights Reserved. Unauthorized duplication of the software, manual or related materials by any means, mechanical or electronic, including translation into another language, except for brief excerpts in published reviews, is prohibited without the express written permission of Protel International Limited. Unauthorized duplication of this work may also be prohibited by local statute. Violators may be subject to both criminal and civil penalties, including fines and/or imprisonment. CircuitMaker, TraxMaker, Protel and Tango are registered trademarks of Protel International Limited. SimCode, SmartWires and The Virtual Electronics Lab are trademarks of Protel International Limited. Microsoft and Microsoft Windows are registered trademarks of Microsoft Corporation. Orcad is a registered trademark of Cadence Design Systems. PADS is a registered trademark of PADS Software. All other trademarks are the property of their respective owners. Printed by Star Printery Pty Ltd ii Table of Contents Chapter 1: Welcome to CircuitMaker Introduction............................................................................................1-1 Required User Background..............................................................1-1 Required Hardware/Software...........................................................1-1 -

Kretskorsdesign

Kretskorsdesign Schema Nätlista Nätlista Layout Simulering Schema ● Beskriver grafiskt vilka komponenter som finns i kretsen och hur de är sammankopplade. ● Behöver inte ha någon koppling till hur kretsen ser ut fysiskt. Nätlista ● Länken mellan den grafiska beskrivningen i schemat och layout eller simulering. ● Mer eller mindre automatiskt genererad textfil med anslutningarna mellan komponenters pinnar. ● Nät kan ges beskrivande namn i schemat, tex ”GND” ● Nät med samma namn är sammankopplade. Kan användas för att få ett tydligare schema. Layout ● Fysisk beskrivning av kretsen. ● Får information om vilka komponenter(och vilken fysisk kapsel) samt anslutningar mellan dessa från nätlistan. ● Hur komponenterna placeras på kortet och hur de fysiska ledningarna ser ut är upp till den som gör layouten. Vilka program finns det? ● Det finns många alternativ... ● Eagle – Historiskt väldigt populärt. – Gratisversion upp till 2 lager och 80x100mm. – Större kort och/eller kommersiellt bruk numera endast via abonnemang. ● Diptrace – Begränsningar på antalet pinnar, 300 eller 500 för ”non-profit”. – 1000 pinnar för 125$ ”non-profit”, 395$ för motsvarande kommersiella version. Open source ● KiCad – Har utvecklats mycket senaste åren. – Fokus har varit på att förbättra layout-delen. – Nästa version kommer att innehålla b.l.a simulering(ngspice) och förbättringar i schema-delen. ● gEDA/PCB – Lite mer löst sammanhållna verktyg. – PCB är förmodligen det äldsta open-source layoutprogrammet som är aktivt, första versionen kom 1990 för Atari Online ● Easyeda – Schema/layout/simulering. – Tillverkar kort, men genererar även gerberfiler. ● Upverter ● Circuitmaker – Från Altium. – Installeras lokalt, men kräver att man är uppkopplad. Tillverkning Layout Gerber, borr-fil Gerber ● En fil per lager. – Filändelsen brukar indikera vilket lager det ska vara ● En eller två borrfiler(pläterade/opläterade hål). -

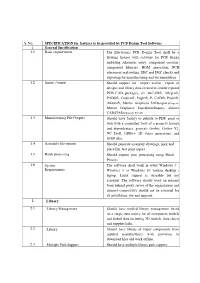

S. No. SPECIFICATION for Features to Be Provided by PCB Design Tool

S. No. SPECIFICATION for features to be provided by PCB Design Tool Software 1 General Specification 1.1 Basic requirements The Electronics PCB Design Tool shall be a floating license with software for PCB design including schematic entry, component creation, component libraries, BOM generation, PCB placement and routing, ERC and DRC checks and exporting for manufacturing and documentation. 1.2 Import / export Should support for import and/or export of designs and library data created in similar reputed PCB CAD packages, viz. OrCAD®, Allegro®, PADS®, Cadstar®, Eagle®, P- CAD®, Protel®, Altium®, Mentor Graphics® DxDesigner®(Import), Mentor Graphics® Expedition(Import), Zuken® CADSTAR®(Import), P-CAD 1.3 Manufacturing File Outputs Should have facility to publish to PDF, print or web with a controlled view of a project's history and dependencies, generate Gerber, Gerber X2, NC Drill, ODB++ 3D video animations, and STEP files. 1.4 Assembly file outputs Should generate assembly drawings, pick and place file, test point report. 1.5 Batch processing Should support post processing using Batch Process 1.6 System The software shall work in 64bit Windows 7 , Requirements Windows 8 or Windows 10 version desktop / laptop. Linux support is desirable but not essential. The software should work on intranet from behind proxy server of the organization and internet connectivity should not be essential for its installation, use and upgrade. 2 Library 2.1 Library Management Should have unified library management based on a single data source for all component models and linked data including 3D models, data sheets and supplier links. 2.2 Library Should have library of major components from reputed manufacturers with provision to download files and work offline. -

Minor Changes and Bug Fixes

List of fixed bugs in DipTrace 4.1.3.1 if compared to 4.1.3.0 PCB Layout 1. If IPC-7351 models are used, STEP export does not work. 2. When entering text into table cells "Shift + U" works as a Hotkey. 3. When importing KiCad 5.1 files, SMD pads on the Bottom layer may be imported incorrectly. Schematics 1. When entering text into table cells "Shift + U" works as a Hotkey.. 2. Back Annotate does not update supplier information. List of fixed bugs in DipTrace 4.1.3.0 if compared to 4.1.2.0 General 1. Snap EDA: multiple clicks for page switching result in a long "freezing". PCB Layout 4. The panelization parameters are reset when opening a schematic file in the PCB Layout after starting. 5. D-shape pads are displayed incorrectly in the Mirror mode. 6. The Highlight Net for the Obround and D-shape pads is displayed incorrectly in the Mirror mode. 7. TrueType text is shifted in BOM HTML. 8. DXF with multilayer blocks is imported incorrectly 9. Export of arcs with a very small angle and extra-large radius to Gerber has been changed. 10. Chamfer of the corners of a rectangular board outline may result in incorrect formation of outlines in Gerber when panelizing with Edge Rails. 11. After changing any of the markings parameters for a group of selected objects, the marking for selected Mounting Hole and Fiducial may appear. 12. Dimension objects are not updated automatically after changing the shape dimensions in the shape properties. -

Manual EAGLE

EAGLE EASILY APPLICABLE GRAPHICAL LAYOUT EDITOR Manual Version4.1 ® 2ndEdition Copyright©2004CadSoftAllRightsReserved ThissoftwareanddocumentationarecopyrightedbyCadSoftComputer, Inc.,doingbusinessunderthetradenameEAGLE.Thesoftwareanddocu- mentationarelicensed,notsold,andmaybeusedorcopiedonlyinaccor- dancewiththeEAGLELicenseAgreementaccompanyingthesoftware and/orreprintedinthisdocument.Thissoftwareembodiesvaluabletradese- cretsproprietarytoCadSoftComputer,Inc. All trademarks referenced in this document are the property of their respec- tive owners. Specifications subject to change without notice. Copyright2004CadSoftComputer,Inc.Allrightsreservedworldwide No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electonic, mechanical, photocopy- ing, recording, scanning, digitizing, or otherwise, without the prior consense ofCadSoft. Printed in the United States of America. Howtoreachus OfficeHoursare: Mon-Thu: 9amto5pmEST Fri: 9amto4pmEST Phone: +1561274-8355 Fax: +1561274-8218 E-mail: [email protected] Web: http://www.cadsoftusa.com CadSoftComputer,Inc. 801SouthFederalHighway,Suite201 DelrayBeach,Florida33483-5185 U.S.A. EAGLELICENSEAGREEMENT Thisisalegalagreementbetweenyou,theenduser,andCadSoftComputer,Inc.,which marketssoftwareproductsunderthetrademarkEAGLE.CadSoftComputer,Inc.shallbe referredtointhisAgreementasCadSoft.IfyoudonotagreetothetermsofthisAgree- ment,promptlyreturnthediskettepackageandaccompanyingitems(includingwritten materialsandcontainers)totheplaceyouobtainedthemforafullrefund.USEOFTHIS -

Metadefender Core V4.17.3

MetaDefender Core v4.17.3 © 2020 OPSWAT, Inc. All rights reserved. OPSWAT®, MetadefenderTM and the OPSWAT logo are trademarks of OPSWAT, Inc. All other trademarks, trade names, service marks, service names, and images mentioned and/or used herein belong to their respective owners. Table of Contents About This Guide 13 Key Features of MetaDefender Core 14 1. Quick Start with MetaDefender Core 15 1.1. Installation 15 Operating system invariant initial steps 15 Basic setup 16 1.1.1. Configuration wizard 16 1.2. License Activation 21 1.3. Process Files with MetaDefender Core 21 2. Installing or Upgrading MetaDefender Core 22 2.1. Recommended System Configuration 22 Microsoft Windows Deployments 22 Unix Based Deployments 24 Data Retention 26 Custom Engines 27 Browser Requirements for the Metadefender Core Management Console 27 2.2. Installing MetaDefender 27 Installation 27 Installation notes 27 2.2.1. Installing Metadefender Core using command line 28 2.2.2. Installing Metadefender Core using the Install Wizard 31 2.3. Upgrading MetaDefender Core 31 Upgrading from MetaDefender Core 3.x 31 Upgrading from MetaDefender Core 4.x 31 2.4. MetaDefender Core Licensing 32 2.4.1. Activating Metadefender Licenses 32 2.4.2. Checking Your Metadefender Core License 37 2.5. Performance and Load Estimation 38 What to know before reading the results: Some factors that affect performance 38 How test results are calculated 39 Test Reports 39 Performance Report - Multi-Scanning On Linux 39 Performance Report - Multi-Scanning On Windows 43 2.6. Special installation options 46 Use RAMDISK for the tempdirectory 46 3. -

![[Amok] S/N: 1299275 a Smaller Note 99 2.08 Firstname](https://docslib.b-cdn.net/cover/4079/amok-s-n-1299275-a-smaller-note-99-2-08-firstname-1924079.webp)

[Amok] S/N: 1299275 a Smaller Note 99 2.08 Firstname

LETRA A A Real Validator 1.01 Name: ubique.daemon [AmoK] s/n: 1299275 A Smaller Note 99 2.08 FirstName: ViKiNG LastName: Crackz Company: private Street: ViKiNG Zip: 11111 City: Crackz Code: 19147950 Order: 97234397 A.I.D 2.1 s/n: AD6778-A2G0 A.I.D. 2.0.2 s/n: AD6778-A2G0T A+ Math 1.0 Name: (Anything) s/n: 8826829 A+ MathMAT 1.0.0 Name: TEAM ElilA s/n: 8826829 A-1 Image Screen Saver 4.1 s/n: B5K7ij49p2 A1 Text Finder 4.02 s/n: PCSLT3248034 ABCPager 1.6.4 Name: Sara s/n: 1DQDSSSSSSSS ABCPager Plus 5.0.5 Name: Sara s/n: M5N5SSSSSSSS Ability Office 2000 2.0.007 Name: Ben Hooks s/n: 12878044-01034-40997 Ability Office 2000 2.0.005 Name:Nemesis] Organization:TNT s/n: 15155445-37898- 08511 Ablaze Quick Viewer 1.6 Name: Hazard s/n: 81261184XXXXXXX Abritus Business 2000 3.02 Name/Company: (Anything) s/n: 1034-314-102 Abritus Business 2000 3.02 Name/Company: (Anything) s/n: 1034-314-102 Absolute Fast Taskbar 1.01 Name: (Anything) s/n: nxpwvy Absolute Security 3.6 Name: Evil Ernie 2K [SCB] s/n: GMKKRAPZBJRRXQP Absolute Security Pro 3.3 Name: C0ke2000 s/n: GPBKTCNKYZKWQPJ Absolute Security Standard 3.4 Name: Hazard 2000 s/n: ECHVNZQRCYEHHBB or Name: PhatAzz [e!] s/n: RBFXPLUMBPGDFYW Absolute Security Standard 3.5 Name: embla of phrozen crew s/n: LTPDTDMAEHNKNTR AbsoluteFTP 1.0 beta 6 Name: CORE/JES Company: CORE s/n: 00-00-000000 Exp: never Key: 1074 2875 9697 3324 3564 AbsoluteFTP 1.0 Final Name: CORE/JES Company: CORE s/n: 00-00-000000 Exp: Never Key: 1074 2875 9697 3324 3564 AbsoluteFTP 1.0 RC 11 Name: _RudeBoy_ Company: Phrozen Crew s/n: 02-01- -

Altium Designer Feature Set Summary

Altium Designer Feature Set Summary Updated March 2013 Altium Designer is available in license options that maximize your choices and make accessing Altium Designer flexible. Whether you are part of a large design team or a consulting engineer operating on your own, Altium Designer presents everything you need to innovate, be competitive and design new products in new ways. Altium Designer 2013 lets designers create a product from concept to manufacture, in a single design environment, embracing hardware, software and programmable hardware (FPGAs). If your design team has engineers who don’t do board implementation but are capturing and verifying the design, implementing systems on FPGAs and specifying the board, choose Altium Designer SE. Altium Designer Altium Designer Altium Designer Altium Designer Feature Description 2013 Viewer 2013 SD 2013 SE 2013 Software integration platform, consistent GUI provided for all supporting editors and viewers, Design DXP Platform Insight for design document preview, design release management, design compiler, file management, P P P version control interface and scripting engine Schematic – Viewer Open, view and print schematic documents and libraries P P P P PCB – Viewer Open, view and print PCB documents, additionally view and navigate 3D PCBs P P P P CAM File – Viewer Open CAM and mechanical files P P P P All schematic and schematic library editing capabilities (except in PCB Projects and Free Documents), Schematic – Soft Design Editing P netlist generation P P VHDL simulation engine, integrated