Cascode Amplifier Figure 1(A) Shows a Cascode Amplifier with Ideal Current Source Load

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

A Review of Electric Impedance Matching Techniques for Piezoelectric Sensors, Actuators and Transducers

Review A Review of Electric Impedance Matching Techniques for Piezoelectric Sensors, Actuators and Transducers Vivek T. Rathod Department of Electrical and Computer Engineering, Michigan State University, East Lansing, MI 48824, USA; [email protected]; Tel.: +1-517-249-5207 Received: 29 December 2018; Accepted: 29 January 2019; Published: 1 February 2019 Abstract: Any electric transmission lines involving the transfer of power or electric signal requires the matching of electric parameters with the driver, source, cable, or the receiver electronics. Proceeding with the design of electric impedance matching circuit for piezoelectric sensors, actuators, and transducers require careful consideration of the frequencies of operation, transmitter or receiver impedance, power supply or driver impedance and the impedance of the receiver electronics. This paper reviews the techniques available for matching the electric impedance of piezoelectric sensors, actuators, and transducers with their accessories like amplifiers, cables, power supply, receiver electronics and power storage. The techniques related to the design of power supply, preamplifier, cable, matching circuits for electric impedance matching with sensors, actuators, and transducers have been presented. The paper begins with the common tools, models, and material properties used for the design of electric impedance matching. Common analytical and numerical methods used to develop electric impedance matching networks have been reviewed. The role and importance of electrical impedance matching on the overall performance of the transducer system have been emphasized throughout. The paper reviews the common methods and new methods reported for electrical impedance matching for specific applications. The paper concludes with special applications and future perspectives considering the recent advancements in materials and electronics. -

Cascode Amplifiers by Dennis L. Feucht Two-Transistor Combinations

Cascode Amplifiers by Dennis L. Feucht Two-transistor combinations, such as the Darlington configuration, provide advantages over single-transistor amplifier stages. Another two-transistor combination in the analog designer's circuit library combines a common-emitter (CE) input configuration with a common-base (CB) output. This article presents the design equations for the basic cascode amplifier and then offers other useful variations. (FETs instead of BJTs can also be used to form cascode amplifiers.) Together, the two transistors overcome some of the performance limitations of either the CE or CB configurations. Basic Cascode Stage The basic cascode amplifier consists of an input common-emitter (CE) configuration driving an output common-base (CB), as shown above. The voltage gain is, by the transresistance method, the ratio of the resistance across which the output voltage is developed by the common input-output loop current over the resistance across which the input voltage generates that current, modified by the α current losses in the transistors: v R A = out = −α ⋅α ⋅ L v 1 2 β + + + vin RB /( 1 1) re1 RE where re1 is Q1 dynamic emitter resistance. This gain is identical for a CE amplifier except for the additional α2 loss of Q2. The advantage of the cascode is that when the output resistance, ro, of Q2 is included, the CB incremental output resistance is higher than for the CE. For a bipolar junction transistor (BJT), this may be insignificant at low frequencies. The CB isolates the collector-base capacitance, Cbc (or Cµ of the hybrid-π BJT model), from the input by returning it to a dynamic ground at VB. -

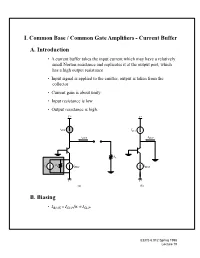

I. Common Base / Common Gate Amplifiers

I. Common Base / Common Gate Amplifiers - Current Buffer A. Introduction • A current buffer takes the input current which may have a relatively small Norton resistance and replicates it at the output port, which has a high output resistance • Input signal is applied to the emitter, output is taken from the collector • Current gain is about unity • Input resistance is low • Output resistance is high. V+ V+ i SUP ISUP iOUT IOUT RL R is S IBIAS IBIAS V− V− (a) (b) B. Biasing = /α ≈ • IBIAS ISUP ISUP EECS 6.012 Spring 1998 Lecture 19 II. Small Signal Two Port Parameters A. Common Base Current Gain Ai • Small-signal circuit; apply test current and measure the short circuit output current ib iout + = β v r gmv oib r − o ve roc it • Analysis -- see Chapter 8, pp. 507-509. • Result: –β ---------------o ≅ Ai = β – 1 1 + o • Intuition: iout = ic = (- ie- ib ) = -it - ib and ib is small EECS 6.012 Spring 1998 Lecture 19 B. Common Base Input Resistance Ri • Apply test current, with load resistor RL present at the output + v r gmv r − o roc RL + vt i − t • See pages 509-510 and note that the transconductance generator dominates which yields 1 Ri = ------ gm µ • A typical transconductance is around 4 mS, with IC = 100 A • Typical input resistance is 250 Ω -- very small, as desired for a current amplifier • Ri can be designed arbitrarily small, at the price of current (power dissipation) EECS 6.012 Spring 1998 Lecture 19 C. Common-Base Output Resistance Ro • Apply test current with source resistance of input current source in place • Note roc as is in parallel with rest of circuit g v m ro + vt it r − oc − v r RS + • Analysis is on pp. -

ECE 255, MOSFET Basic Configurations

ECE 255, MOSFET Basic Configurations 8 March 2018 In this lecture, we will go back to Section 7.3, and the basic configurations of MOSFET amplifiers will be studied similar to that of BJT. Previously, it has been shown that with the transistor DC biased at the appropriate point (Q point or operating point), linear relations can be derived between the small voltage signal and current signal. We will continue this analysis with MOSFETs, starting with the common-source amplifier. 1 Common-Source (CS) Amplifier The common-source (CS) amplifier for MOSFET is the analogue of the common- emitter amplifier for BJT. Its popularity arises from its high gain, and that by cascading a number of them, larger amplification of the signal can be achieved. 1.1 Chararacteristic Parameters of the CS Amplifier Figure 1(a) shows the small-signal model for the common-source amplifier. Here, RD is considered part of the amplifier and is the resistance that one measures between the drain and the ground. The small-signal model can be replaced by its hybrid-π model as shown in Figure 1(b). Then the current induced in the output port is i = −gmvgs as indicated by the current source. Thus vo = −gmvgsRD (1.1) By inspection, one sees that Rin = 1; vi = vsig; vgs = vi (1.2) Thus the open-circuit voltage gain is vo Avo = = −gmRD (1.3) vi Printed on March 14, 2018 at 10 : 48: W.C. Chew and S.K. Gupta. 1 One can replace a linear circuit driven by a source by its Th´evenin equivalence. -

Cascode Techniques

Analysis and Design of Analog Integrated Circuits Lecture 8 Cascode Techniques Michael H. Perrott February 15, 2012 Copyright © 2012 by Michael H. Perrott All rights reserved. M.H. Perrott Review of Large Signal Analysis of Current Mirrors Vdd Δ V2 I I 1 2 1 μ W2 2 λ nCox (VGS2-VTH) (1+ 2Vds2) I2 2 L = 2 I 1 W 2 1 μ C 1(V -V ) (1+λ V ) 2 n ox GS1 TH 1 ds1 M L1 2 ΔV M1 Vds2 > Vdsat2 1 V +ΔV V +ΔV Δ Δ Δ Δ Vss=0 TH 1 TH 2 But, VTH+ V1=VTH+ V2 V1 = V2 λ I2 W2 L1 (1+ 2Vds2) I2 = λ I1 W1 L2 (1+ 1Vds1) M2 in Saturation Current Mismatch setting due to Vds based on difference M2 in Triode geometry Note: for accurate ratio, set L1 = L2 Vds2 Vdsat2 M.H. Perrott 2 The Issue of Vds Mismatch in Current Mirrors V λ dd I2 W2 (1+ 2Vds2) = λ I1 W1 (1+ 1Vds1) I1 I2 Current Mismatch setting due to Vds based on difference geometry V V ds1 ds2 Note: we are assuming L = L M1 M2 1 2 . Issue: Current I2 can vary significantly as a function of the drain voltage of M2 - We often want a tightly controlled current set only by I1 and transistor sizes . How do we improve the current mirror matching performance? M.H. Perrott 3 Cascoded Current Source I Rth R ref d3 thd3 Ibias Vbias V M bias 3 M3 M ro1 2 M1 . Offers increased output resistance - Reduces small signal dependence of output current on the output voltage of the current source - From Lecture 6, we derived: . -

CHAPTER 3 Frequency Response of Basic BJT and MOSFET Amplifiers (Review Materials in Appendices III and V)

CHAPTER 3 Frequency Response of Basic BJT and MOSFET Amplifiers (Review materials in Appendices III and V) In this chapter you will learn about the general form of the frequency domain transfer function of an amplifier. You will learn to analyze the amplifier equivalent circuit and determine the critical frequencies that limit the response at low and high frequencies. You will learn some special techniques to determine these frequencies. BJT and MOSFET amplifiers will be considered. You will also learn the concepts that are pursued to design a wide band width amplifier. Following topics will be considered. Review of Bode plot technique. Ways to write the transfer (i.e., gain) functions to show frequency dependence. Band-width limiting at low frequencies (i.e., DC to fL). Determination of lower band cut-off frequency for a single-stage amplifier – short circuit time constant technique. Band-width limiting at high frequencies for a single-stage amplifier. Determination of upper band cut-off frequency- several alternative techniques. Frequency response of a single device (BJT, MOSFET). Concepts related to wide-band amplifier design – BJT and MOSFET examples. 3.1 A short review on Bode plot technique Example: Produce the Bode plots for the magnitude and phase of the transfer function 10s Ts() , for frequencies between 1 rad/sec to 106 rad/sec. (1ss / 1025 )(1 / 10 ) We first observe that the function has zeros and poles in the numerical sequence 0 (zero), 2 5 2 10 (pole), and 10 (pole). Further at ω=1 rad/sec i.e., lot less than the first pole (at ω=10 rad/sec), Ts() 10 s. -

Optimal High Performance Self Cascode CMOS Current Mirror

View metadata, citation and similar papers at core.ac.uk brought to you by CORE provided by Global Journal of Computer Science and Technology (GJCST) Global Journal of Computer Science and Technology Volume 11 Issue 15 Version 1.0 September 2011 Type: Double Blind Peer Reviewed International Research Journal Publisher: Global Journals Inc. (USA) Online ISSN: 0975-4172 & Print ISSN: 0975-4350 Optimal High Performance Self Cascode CMOS Current Mirror By Vivek Pant, Shweta Khurana Kurukshetra University Kurukshetra Abstract - In this paper the current mirror presented, having low voltage and mixed mode structure has been proposed. The performance of self cascade MOSFET current mirror is optimized with high output impedance and can operate at 1 V or below. Simulation results conform to Analog Mentor tools having Design Architect for schematics and Eldonet for SPICE simulation, with input reference current of 20μA. This review paper presents a comparative performance study of self cascode current mirror with other current mirrors. Keywords : current mirrors, cascode current mirror, low voltage analog circuit. GJCST Classification : I.2.9 Optimal High Performance Self Cascode CMOS Current Mirror Strictly as per the compliance and regulations of: © 2011. Vivek Pant, Shweta Khurana.This is a research/review paper, distributed under the terms of the Creative Commons Attribution-Noncommercial 3.0 Unported License http://creativecommons.org/licenses/by-nc/3.0/), permitting all non commercial use, distribution, and reproduction in any medium, provided the original work is properly cited. Optimal High Performance Self Cascode CMOS Current Mirror Vivek Pantα, Shweta KhuranaΩ Abstract - In this paper the current mirror presented, having I = I (W/L) 2 (1+λVds2) (3) out ref low voltage and mixed mode structure has been proposed. -

JFE150 Ultra-Low Noise, Low Gate Current, Audio, N-Channel JFET Datasheet

JFE150 SLPS732 – JUNE 2021 JFE150 Ultra-Low Noise, Low Gate Current, Audio, N-Channel JFET 1 Features and yields excellent noise performance for currents from 50 μA to 20 mA. When biased at 5 mA, the • Ultra-low noise: device yields 0.8 nV/√Hz of input-referred noise, – Voltage noise: giving ultra-low noise performance with extremely high input impedance (> 1 TΩ). The JFE150 also • 0.8 nV/√Hz at 1 kHz, IDS = 5 mA features integrated diodes connected to separate • 0.9 nV/√Hz at 1 kHz, IDS = 2 mA – Current noise: 1.8 fA/√Hz at 1 kHz clamp nodes to provide protection without the addition • Low gate current: 10 pA (max) of high leakage, nonlinear external diodes. • Low input capacitance: 24 pF at VDS = 5 V The JFE150 can withstand a high drain-to-source • High gate-to-drain and gate-to-source breakdown voltage of 40-V, as well as gate-to-source and gate- voltage: –40 V to-drain voltages down to –40 V. The temperature • High transconductance: 68 mS range is specified from –40°C to +125°C. The device • Packages: Small SC70 and SOT-23 (Preview) is offered in 5-pin SOT-23 and SC-70 packages. 2 Applications Device Information • Microphone inputs PART NUMBER PACKAGE(1) BODY SIZE (NOM) • Hydrophones and marine equipment SOT-23 (5) - Preview 2.90 mm × 1.60 mm JFE150 • DJ controllers, mixers, and other DJ equipment SC-70 (5) 2.00 mm × 1.25 mm • Professional audio mixer or control surface • Guitar amplifier and other music instrument (1) For all available packages, see the package option addendum at the end of the data sheet. -

Lecture 19 Common-Gate Stage

4/7/2008 Lecture 19 OUTLINE • Common‐gate stage • Source follower • Reading: Chap. 7.3‐7.4 EE105 Spring 2008 Lecture 19, Slide 1Prof. Wu, UC Berkeley Common‐Gate Stage AvmD= gR • Common‐gate stage is similar to common‐base stage: a rise in input causes a rise in output. So the gain is positive. EE105 Spring 2008 Lecture 19, Slide 2Prof. Wu, UC Berkeley EE105 Fall 2007 1 4/7/2008 Signal Levels in CG Stage • In order to maintain M1 in saturation, the signal swing at Vout cannot fall below Vb‐VTH EE105 Spring 2008 Lecture 19, Slide 3Prof. Wu, UC Berkeley I/O Impedances of CG Stage 1 R = in λ =0 RRout= D gm • The input and output impedances of CG stage are similar to those of CB stage. EE105 Spring 2008 Lecture 19, Slide 4Prof. Wu, UC Berkeley EE105 Fall 2007 2 4/7/2008 CG Stage with Source Resistance 1 g vv= m Xin1 + RS gm 1 vv g AgR==out x m vmD1 vvxin + RS gm R gR ==D mD 1 1+ gRmS + RS gm • When a source resistance is present, the voltage gain is equal to that of a CS stage with degeneration, only positive. EE105 Spring 2008 Lecture 19, Slide 5Prof. Wu, UC Berkeley Generalized CG Behavior Rgout= (1++g mrR O) S r O • When a gate resistance is present it does not affect the gain and I/O impedances since there is no potential drop across it (at low frequencies). • The output impedance of a CG stage with source resistance is identical to that of CS stage with degeneration. -

Experiment No. 7 - BJT Amplifier Input/Output Impedances

UNIVERSITY OF NORTH CAROLINA AT CHARLOTTE Department of Electrical and Computer Engineering Experiment No. 7 - BJT Amplifier Input/Output Impedances Overview: The purpose of this lab is to familiarize the student with the measurement of the input and output impedances of a Bipolar Junction Transistor single-stage amplifier. In previous experiments the DC biasing and AC amplification in BJT amplifiers has been investigated. This BJT experiment will build upon these previous experiments as well as expand into the investigation of input and output impedances. The amplifier chosen for study is the common-emmitter type as shown in Figure 1. Techniques for properly biasing the BJT amplifier and setting up AC amplification will be further utilized and methods for measuring imput and output impedances will be introduced. While the input impedance of an amplifier is in general a complex quantity, in the midband range it is predominantly resistive. Input impedance is defined as the ratio of imput voltage to input current. It is calculated from the AC equivalent circuit as the equivalent resistance looking into the input with all current cources replaced by an open and all voltage sources replaced by a short. The significance of input impedance is that it provides a measure of the loading effect of the amplifier. A low input impedance translates to a poor low-frequency response and a large input power requirement. For example, Op-Amps have a very large input impedance, and therefore, a good low- frequency response and a low input power requirement. Likewise, output impedance is in general a complex quantity, but is predominantly resistive in the midband range. -

Fundamentals of MOSFET and IGBT Gate Driver Circuits

Application Report SLUA618A–March 2017–Revised October 2018 Fundamentals of MOSFET and IGBT Gate Driver Circuits Laszlo Balogh ABSTRACT The main purpose of this application report is to demonstrate a systematic approach to design high performance gate drive circuits for high speed switching applications. It is an informative collection of topics offering a “one-stop-shopping” to solve the most common design challenges. Therefore, it should be of interest to power electronics engineers at all levels of experience. The most popular circuit solutions and their performance are analyzed, including the effect of parasitic components, transient and extreme operating conditions. The discussion builds from simple to more complex problems starting with an overview of MOSFET technology and switching operation. Design procedure for ground referenced and high side gate drive circuits, AC coupled and transformer isolated solutions are described in great details. A special section deals with the gate drive requirements of the MOSFETs in synchronous rectifier applications. For more information, see the Overview for MOSFET and IGBT Gate Drivers product page. Several, step-by-step numerical design examples complement the application report. This document is also available in Chinese: MOSFET 和 IGBT 栅极驱动器电路的基本原理 Contents 1 Introduction ................................................................................................................... 2 2 MOSFET Technology ...................................................................................................... -

Tabulation of Published Data on Electron Devices of the U.S.S.R. Through December 1976

NAT'L INST. OF STAND ms & TECH R.I.C. Pubii - cations A111D4 4 Tfi 3 4 4 NBSIR 78-1564 Tabulation of Published Data on Electron Devices of the U.S.S.R. Through December 1976 Charles P. Marsden Electron Devices Division Center for Electronics and Electrical Engineering National Bureau of Standards Washington, DC 20234 December 1978 Final QC— U.S. DEPARTMENT OF COMMERCE 100 NATIONAL BUREAU OF STANDARDS U56 73-1564 Buraev of Standard! NBSIR 78-1564 1 4 ^79 fyr *'• 1 f TABULATION OF PUBLISHED DATA ON ELECTRON DEVICES OF THE U.S.S.R. THROUGH DECEMBER 1976 Charles P. Marsden Electron Devices Division Center for Electronics and Electrical Engineering National Bureau of Standards Washington, DC 20234 December 1978 Final U.S. DEPARTMENT OF COMMERCE, Juanita M. Kreps, Secretary / Dr. Sidney Harman, Under Secretary Jordan J. Baruch, Assistant Secretary for Science and Technology NATIONAL BUREAU OF STANDARDS, Ernest Ambler, Director - 1 TABLE OF CONTENTS Page Preface i v 1. Introduction 2. Description of the Tabulation ^ 1 3. Organization of the Tabulation ’ [[ ] in ’ 4. Terminology Used the Tabulation 3 5. Groups: I. Numerical 7 II. Receiving Tubes 42 III . Power Tubes 49 IV. Rectifier Tubes 53 IV-A. Mechanotrons , Two-Anode Diode 54 V. Voltage Regulator Tubes 55 VI. Current Regulator Tubes 55 VII. Thyratrons 56 VIII. Cathode Ray Tubes 58 VIII-A. Vidicons 61 IX. Microwave Tubes 62 X. Transistors 64 X-A-l . Integrated Circuits 75 X-A-2. Integrated Circuits (Computer) 80 X-A-3. Integrated Circuits (Driver) 39 X-A-4. Integrated Circuits (Linear) 89 X- B.