(Bok): Through-Silicon Via Technology

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

ED-7311-20.Pdf

EIAJ ED-7311-20 - 1 - EIAJ ED-7311-20 - 2 - EIAJ ED-7311-20 - 3 - EIAJ ED-7311-20 - 4 - EIAJ ED-7311-20 - 5 - EIAJ ED-7311-20 - 6 - EIAJ ED-7311-20 - 7 - EIAJ ED-7311-20 - 8 - EIAJ ED-7311-20 - 9 - EIAJ ED-7311-20 - 10 - EIAJ ED-7311-20 - 11 - EIAJ ED-7311-20 - 12 - EIAJ ED-7311-20 - 13 - EIAJ ED-7311-20 - 14 - EIAJ ED-7311-20 - 15 - EIAJ ED-7311-20 - 16 - EIAJ ED-7311-20 - 17 - EIAJ ED-7311-20 - 18 - EIAJ ED-7311-20 - 19 - EIAJ ED-7311-20 - 20 - EIAJ ED-7311-20 - 21 - EIAJ ED-7311-20 - 22 - EIAJ ED-7311-20 - 23 - EIAJ ED-7311-20 - 24 - EIAJ ED-7311-20 - 25 - EIAJ ED-7311-20 - 26 - EIAJ ED-7311-20 - 27 - EIAJ ED-7311-20 - 28 - EIAJ ED-7311-20 - 29 - EIAJ ED-7311-20 - 30 - EIAJ ED-7311-20 - 31 - EIAJ ED-7311-20 - 32 - EIAJ ED-7311-20 - 33 - EIAJ ED-7311-20 - 34 - EIAJ ED-7311-20 - 35 - EIAJ ED-7311-20 - 36 - EIAJ ED-7311-20 - 37 - EIAJ ED-7311-20 - 38 - EIAJ ED-7311-20 - 39 - EIAJ ED-7311-20 - 40 - EIAJ ED-7311-20 - 41 - EIAJ ED-7311-20 - 42 - EIAJ ED-7311-20 - 43 - EIAJ ED-7311-20 - 44 - EIAJ ED-7311-20 - 45 - EIAJ ED-7311-20 - 46 - EIAJ ED-7311-20 - 47 - EIAJ ED-7311-20 - 48 - EIAJ ED-7311-20 - 49 - EIAJ ED-7311-20 - 50 - EIAJ ED-7311-20 - 51 - EIAJ ED-7311-20 - 52 - EIAJ ED-7311-20 - 53 - EIAJ ED-7311-20 - 54 - EIAJ ED-7311-20 - 55 - EIAJ ED-7311-20 - 56 - EIAJ ED-7311-20 - 57 - EIAJ ED-7311-20 - 58 - EIAJ ED-7311-20 - 59 - EIAJ ED-7311-20 - 60 - EIAJ ED-7311-20 - 61 - EIAJ ED-7311-20 - 62 - EIAJ ED-7311-20 - 63 - EIAJ ED-7311-20 - 64 - EIAJ ED-7311-20 - 65 - EIAJ ED-7311-20 - 66 - EIAJ ED-7311-20 - 67 - EIAJ ED-7311-20 - 68 - EIAJ -

FY2008 Results Meeting

FY200FY20088 ResultsResults MeetingMeeting FY2008 : Year ended March 31, 2009 May 14, 2009 Ryosan Company, Limited Code : 8140 / Stock listings: Tokyo Stock Exchange (First Section) URL : http://www.ryosan.co.jp/eng/ Notice This presentation contains forward-looking statements regarding business performance, which may differ substantially from actual results, depending on certain risks and uncertainties, the most significant of which are listed below. z Economic conditions in key markets (Japan and the rest of Asia), rapid changes in consumption patterns and supply-demand balance for products z Sharp fluctuations in the ¥/$ exchange rate z Substantial fluctuation in prices in capital markets Consolidated results for FY 2008 FY2007 FY2008 FY2009(Forecasts) Of Total Of Total % Chg. YoY Of Total % Chg. YoY ¥ 100 million% ¥ 100 million%% ¥ 100 million %% Net sales 2,860 2,208 (22.8) 1,700 (23.0) Gross margin 251 8.8 196 8.9 (22.1) 149 8.8 (24.1) SG&A expenses 144 5.0 134 6.1 (6.8) 115 6.8 (14.7) Operating income 107 3.8 61 2.8 (42.8) 34 2.0 (44.7) Ordinary income 112 3.9 72 3.3 (35.6) 38 2.2 (47.7) Net income 67 2.4 39 1.8 (41.8) 22 1.3 (43.9) Earnings per share ¥187.15 ¥111.83 (¥75) ¥63.83 (¥48) 1 Segment results for FY2008 Unit : ¥ 100 million FY2007 FY2008 FY2009(Forecasts) OP OP OP Margin Margin % Chg. YoYMargin % Chg. YoY % % Sales 1,489 1,169 (21.5) 808 (30.9) Semiconductors Operating income 724.9% 48 4.2%(32.7) 28 3.5% (42.7) Electronic Sales 1,031 759 (26.4) 584 (23.1) Components Operating income 444.3 28 3.7 (35.9) 22 3.8 (22.1) -

Advanced MOSFET Structures and Processes for Sub-7 Nm CMOS Technologies

Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies By Peng Zheng A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences in the Graduate Division of the University of California, Berkeley Committee in charge: Professor Tsu-Jae King Liu, Chair Professor Laura Waller Professor Costas J. Spanos Professor Junqiao Wu Spring 2016 © Copyright 2016 Peng Zheng All rights reserved Abstract Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies by Peng Zheng Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences University of California, Berkeley Professor Tsu-Jae King Liu, Chair The remarkable proliferation of information and communication technology (ICT) – which has had dramatic economic and social impact in our society – has been enabled by the steady advancement of integrated circuit (IC) technology following Moore’s Law, which states that the number of components (transistors) on an IC “chip” doubles every two years. Increasing the number of transistors on a chip provides for lower manufacturing cost per component and improved system performance. The virtuous cycle of IC technology advancement (higher transistor density lower cost / better performance semiconductor market growth technology advancement higher transistor density etc.) has been sustained for 50 years. Semiconductor industry experts predict that the pace of increasing transistor density will slow down dramatically in the sub-20 nm (minimum half-pitch) regime. Innovations in transistor design and fabrication processes are needed to address this issue. The FinFET structure has been widely adopted at the 14/16 nm generation of CMOS technology. -

1332:Xtks Nippon Suisan Kaisha Ltd 3 4 1 1334:Xtks Maruha Nichiro Holdings Inc. 3 4 1 1377:Xtks Sakata Seed Corp. 3 5 2 1414:Xtks SHO-BOND Holdings Co

Symbol Code Description Current Rating New rating Diff 1332:xtks Nippon Suisan Kaisha Ltd 3 4 1 1334:xtks Maruha Nichiro Holdings Inc. 3 4 1 1377:xtks Sakata Seed Corp. 3 5 2 1414:xtks SHO-BOND Holdings Co. Ltd 3 6 3 1766:xtks TOKEN Corp. 3 6 3 1801:xtks Taisei Corp. 3 5 2 1803:xtks Shimizu Corp. 3 4 1 1808:xtks Haseko Corp. 3 4 1 1812:xtks Kajima Corp. 3 5 2 1820:xtks Nishimatsu Construction Co. Ltd 3 6 3 1824:xtks Maeda Corp. 3 6 3 1833:xtks Okumura Corp. 3 6 3 1860:xtks Toda Corp. 3 5 2 1861:xtks Kumagai Gumi Co. Ltd 3 8 5 1865:xtks Asunaro Aoki Construction Co. Ltd 3 6 3 1870:xtks Yahagi Construction Co. Ltd 3 4 1 1881:xtks NIPPO Corp. 3 6 3 1883:xtks Maeda Road Construction Co. Ltd 3 6 3 1911:xtks Sumitomo Forestry Co Ltd 3 4 1 1924:xtks PanaHome Corp. 3 4 1 1925:xtks Daiwa House Industry Co. Ltd 3 4 1 1928:xtks Sekisui House Ltd 3 4 1 1934:xtks YURTEC Corp. 3 6 3 1945:xtks Tokyo Energy & Systems Inc. 3 4 1 1961:xtks Sanki Engineering Co. Ltd 3 4 1 1963:xtks JGC Corporation 3 4 1 1968:xtks Taihei Dengyo Kaisha Ltd 3 4 1 1969:xtks Takasago Thermal Engineering Co. Ltd 3 4 1 1973:xtks NEC Networks & System Integration Corp. 3 5 2 1979:xtks Taikisha Ltd 3 4 1 1983:xtks TOSHIBA PLANT SYSTEMS & SERVICES Corp. -

Coverage Layout Design Rules and Insertion Utilities for CMP-Related Processes

Journal of Low Power Electronics and Applications Review Coverage Layout Design Rules and Insertion Utilities for CMP-Related Processes Eitan N. Shauly 1,2,* and Sagee Rosenthal 1 1 Tower Semiconductor, Migdal Ha’Emek 10556, Israel; [email protected] 2 The Faculty of Materials Science and Engineering, Technion-Israel Institute of Technology, Haifa 32000, Israel * Correspondence: [email protected] Abstract: The continuous scaling needed for higher density and better performance has introduced some new challenges to the planarity processes. This has resulted in new definitions of the layout coverage rules developed by the foundry and provided to the designers. In advanced technologies, the set of rules considers both the global and the local coverage of the front-end-of line (FEOL) dielectric layers, to the back-end-of-line (BEOL) Cu layers and Al layers, to support high-k/Metal Gate process integration. For advance technologies, a new set of rules for dummy feature insertion was developed by the integrated circuit (IC) manufacturers in order to fulfill coverage limits. New models and utilities for fill insertion were developed, taking into consideration the design coverage, thermal effects, sensitive signal line, critical analog and RF devices like inductors, and double patterning requirements, among others. To minimize proximity effects, cell insertion was also introduced. This review is based on published data from leading IC manufacturers with a careful integration of new experimental data accumulated by the authors. We aim to present a typical foundry perspective. The review provides a detailed description of the chemical mechanical polishing (CMP) process and the coverage dependency, followed by a comprehensive description of coverage rules needed for dielectric, poly, and Cu layers used in advanced technologies. -

UNO Template

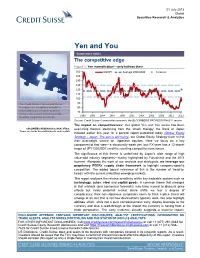

01 July 2013 Global Securities Research & Analytics Yen and You Connections Series The competitive edge Figure 1: Yen 'normalisation'—only halfway there 160 USDJPY Average 1990-2008 Forecast 150 140 130 120 110 100 The Credit Suisse Connections Series 90 leverages our exceptional breadth of 80 macro and micro research to deliver 70 incisive cross-sector and cross-border 1990 1992 1994 1997 1999 2001 2004 2006 2008 2011 2013 thematic insights for our clients. Source: Credit Suisse Commodities research, the BLOOMBERG PROFESSIONAL™ service The impact on competitiveness: Our global Yen and You series has been SECURITIES RESEARCH & ANALYTICS examining themes stemming from the 'shock therapy' the Bank of Japan Please see inside for contributors to each section initiated earlier this year. In a parallel report published today (Global Equity Strategy - Japan: The sun is still rising), our Global Equity Strategy team revisit their overweight stance on Japanese equities. Here we focus on a key component of that view—a structurally weak yen (our FX team has a 12-month target of JPY120/USD1) and the resulting competitiveness issues. The significance of this theme is underlined by Japan's wide range of high value-add industry segments—starkly highlighted by Fukushima and the 2011 tsunami. Alongside the work of our analysts and strategists, we leverage our proprietary PEERs supply chain framework to highlight company-specific competition. The added topical relevance of this is the number of 'head-to- heads' with the current embattled emerging markets. This report analyses the relative sensitivity within key tradeable sectors such as technology, autos, steel and capital goods. -

Division of Investment Department of the Treasury State of New Jersey Pension Fund June 30, 2009 and 2008 (With Independent Auditors’ Report Thereon)

F INANCIAL S TATEMENTS, M ANAGEMENT’ S D ISCUSSION AND A NALYSIS AND S UPPLEMENTAL S CHEDULES Division of Investment Department of the Treasury State of New Jersey Pension Fund June 30, 2009 and 2008 (With Independent Auditors’ Report Thereon) Division of Investment Department of the Treasury State of New Jersey Pension Fund Financial Statements June 30, 2009 and 2008 Contents Independent Auditors’ Report ..........................................................................................................1 Management’s Discussion and Analysis .........................................................................................3 Basic Financial Statements: Statements of Net Assets .................................................................................................................7 Statements of Changes in Net Assets...............................................................................................8 Notes to Financial Statements ..........................................................................................................9 Supplemental Schedules: Schedule 1 – Combining Schedule of Net Assets ..........................................................................31 Schedule 2 – Combining Schedule of Changes in Net Assets .......................................................32 Schedule 3 – Portfolio of Investments – Common Fund A ...........................................................33 Schedule 4 – Portfolio of Investments – Common Fund B ...........................................................57 -

Delaware, 1:11-Cv-00770

IN THE UNITED STATES DISTRICT COURT FOR THE DISTRICT OF DELAWARE HSM PORTFOLIO LLC AND § TECHNOLOGY PROPERTIES § LIMITED LLC, § § Plaintiffs, § § v. § C.A. No. 1:11-cv-00770-RGA § FUJITSU LIMITED, § JURY TRIAL DEMANDED FUJITSU AMERICA, INC., § FUJITSU SEMICONDUCTOR § AMERICA, INC., § § ADVANCED MICRO DEVICES, INC., § § QUALCOMM INCORPORATED, § § ELPIDA MEMORY, INC., § ELPIDA MEMORY (USA) INC., § § SK HYNIX INC., § SK HYNIX AMERICA INC., § HYNIX SEMICONDUCTOR § MANUFACTURING AMERICA INC., § § MICRON TECHNOLOGY, INC., § § PROMOS TECHNOLOGIES INC., § § SANDISK CORPORATION, § § SONY CORPORATION, § SONY CORPORATION OF AMERICA, § SONY ELECTRONICS INC., § SONY COMPUTER § ENTERTAINMENT INC., § SONY COMPUTER § ENTERTAINMENT AMERICA LLC, § § STMICROELECTRONICS N.V., § STMICROELECTRONICS, INC., § § PAGE 1 TOSHIBA CORPORATION, § TOSHIBA AMERICA, INC., § TOSHIBA AMERICA ELECTRONIC § COMPONENTS, INC., § § ON SEMICONDUCTOR § CORPORATION, § § ZORAN CORPORATION, § § Defendants. § PLAINTIFFS’ THIRD AMENDED COMPLAINT Plaintiffs HSM Portfolio LLC and Technology Properties Limited LLC (collectively “Plaintiffs”) by and through their undersigned counsel, file this Third Amended Complaint against Defendants Fujitsu Limited, Fujitsu America, Inc., Fujitsu Semiconductor America, Inc. (collectively “Fujitsu”), Advanced Micro Devices, Inc. (“AMD”), Qualcomm Incorporated (“Qualcomm”), Elpida Memory, Inc., Elpida Memory (USA) Inc. (collectively “Elpida”),1 SK Hynix Inc., SK Hynix America Inc., Hynix Semiconductor Manufacturing America Inc. (collectively “SK Hynix”), -

A Back-End, CMOS Compatible Ferroelectric Field Effect Transistor

A back-end, CMOS compatible ferroelectric Field Effect Transistor for synaptic weights , , Mattia Halter,∗ † ‡ Laura Bégon-Lours,† Valeria Bragaglia,† Marilyne Sousa,† Bert Jan Offrein,† Stefan Abel,† Mathieu Luisier,‡ and Jean Fompeyrine† IBM Research GmbH - Zurich Research Laboratory, CH-8803 RÃijschlikon, Switzerland † Integrated Systems Laboratory, ETH Zurich, CH-8092 Zurich, Switzerland ‡ E-mail: [email protected] Abstract Neuromorphic computing architectures enable the dense co-location of memory and processing elements within a single circuit. This co-location removes the communi- cation bottleneck of transferring data between separate memory and computing units as in standard von Neuman architectures for data-critical applications including ma- chine learning. The essential building blocks of neuromorphic systems are non-volatile synaptic elements such as memristors. Key memristor properties include a suitable non-volatile resistance range, continuous linear resistance modulation and symmetric arXiv:2001.06475v1 [cs.ET] 17 Jan 2020 switching. In this work, we demonstrate voltage-controlled, symmetric and analog po- tentiation and depression of a ferroelectric Hf0.57Zr0.43O2 (HZO) field effect transistor (FeFET) with good linearity. Our FeFET operates with a low writing energy (fJ) and fast programming time (40 ns). Retention measurements have been done over 4-bits depth with low noise (1 %) in the tungsten oxide (WOx) read out channel. By ad- justing the channel thickness from 15nm to 8nm, the on/off ratio of the FeFET can be engineered from 1 % to 200 % with an on-resistance ideally >100 kΩ, depending on the channel geometry. The device concept is using earth-abundant materials, and is 1 compatible with a back end of line (BEOL) integration into complementary metal-oxide- semiconductor (CMOS) processes. -

2008 International Symposium on Semiconductor Manufacturing

2008 International Symposium on Semiconductor Manufacturing (ISSM 2008) Tokyo, Japan 27 – 29 October 2008 IEEE Catalog Number: CFP08SSM-PRT ISBN: 978-1-61284-948-5 ISSM 2008 Program Schedule The 1st day (Monday, October 27) Tutorial Session Room: Century A/B 9:30 Tutorial Session AEC/APC Introduction of AEC/APC's history Mr. Toshihiko Osada, Senior Manager, Fujitsu Microelectronics Limited Manufacturing engineering and AEC/APC Mr. Kensuke Uriga, CEO/President, Dura Systems Corporation Application of control theory for AEC/APC in semiconductor fabrication Mr. Hiroshi Shimizu, Director/Advanced Solution Department, Advance Automation Company, Yamatake Corporation 9:00 Tutorial Session ESH SUSTAINABILITY AND ESH ASPECTS OF ADVANCED SEMICONDUCTOR MANUFACTURING Prof. Farhang Shadman, Regents Professor of Chemical and Environmental Engineering, the University of Arizona Opening Remarks Room: Century 13:00 Keynote Speech Session Room: Century 13:20 Challenges in The DRAM Business Mr.Yukio Sakamoto, President&CEO, Elpida Memory,Inc. 14:10 The New Dynamics of Semiconductor Industry Dr. Tien Wu, Chief Operating Officer, Board of Directors, Advanced Semiconductor Engineering Inc.(ASE) 15:00 Break Oral Session Room: Century A Highlight Session <Advanced Lithography Session> 15:10 PE-O-097 Phenomenology of ArF Photoresist Shrinkage Trends ..........................................................3 Benjamin Bunday, ISMI 15:30 PE-O-044 Lithography Hotspot Discovery at 70nm DRAM 300mm Fab : Process Window Qualification Using Design Based Binning...............................................................................7 -

Design, Fabrication, and Characterization of Three‑Dimensional Embedded Capacitor in Through‑Silicon Via

This document is downloaded from DR‑NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore. Design, fabrication, and characterization of three‑dimensional embedded capacitor in through‑silicon via Lin, Ye 2019 Lin, Y. (2019). Design, fabrication, and characterization of three‑dimensional embedded capacitor in through‑silicon via. Doctoral thesis, Nanyang Technological University, Singapore. https://hdl.handle.net/10356/102666 https://doi.org/10.32657/10220/48586 Downloaded on 28 Sep 2021 02:52:36 SGT ( O n th e S p ine) DESIGN, FA BRICATION, AND CHARACTERIZATION OF 3 DESIGN, FABRICATION, AND CHARACTERIZATION OF THREE-DIMENSIONAL EMBEDDED CAPACITOR IN THROUGH-SILICON VIA - D EMBEDDED CAPACITOR IN TSV LIN YE LIN YE SCHOOL OF ELECTRICAL AND ELECTRONIC ENGINEERING 2019 2019 DESIGN, FABRICATION, AND CHARACTERIZATION OF THREE-DIMENSIONAL EMBEDDED CAPACITOR IN THROUGH-SILICON VIA LIN YE (B. Eng., Nanyang Technological University) SCHOOL OF ELECTRICAL AND ELECTRONIC ENGINEERING A thesis submitted to the Nanyang Technological University in partial fulfillment of the requirement for the degree of Doctor of Philosophy 2019 Statement of Originality I hereby certify that the work embodied in this thesis is the result of original research, is free of plagiarised materials, and has not been submitted for a higher degree to any other University or Institution. 28 May 2019 Date Lin Ye Supervisor Declaration Statement I have reviewed the content and presentation style of this thesis and declare it is free of plagiarism and of sufficient grammatical clarity to be examined. To the best of my knowledge, the research and writing are those of the candidate except as acknowledged in the Author Attribution Statement. -

Top 300 Organizations Granted U.S. Patents in 2007

Top 300 Organizations Granted U.S. Patents in 2007 NOTE: IPO DOES NOT INTEND TO ENCOURAGE MORE PATENTING IN U.S. This annual report listing the organizations that received the most U.S. utility patents is being published by fO kramedarT & tnetaP .S.U eht morf deniatbo atad no desab si tI .raey evitucesnoc ht52 eht rof OPI rof eht ht52 evitucesnoc .raey tI si desab no atad deniatbo morf eht .S.U tnetaP & kramedarT fO fi .ec Patents granted to parent and subsidiary companies are combined in some instances. See the end notes for background on how the report was prepared. IPO does not intend for this report to encourage or discourage patenting. Some critics believe companies are applying for too many patents. In 2007 the U.S. Patent & Trademark Office announced that it would no longer publish its own report on organizations receiving the most patents, because it wanted to discour- age “any perception that we believe more is better.” IPO has opted to continue publishing this IPO report, however, because the number of patents granted is one of the few objective measures of the patent system as a whole and the patenting activities of individual industries and companies. IPO and others are study- ing ways to develop more reliable measures of patent quality. May 21, 2008 Contents: Numerical Listing . 2 Alphabetical Listing . 6 Notes . 10 © Copyright 2008 Intellectual Property Owners Association 1 2007 Patent Owners Numerical Listing Rank Organization Patent Rank Organization Patent 1 International Business Machines Corp. 3,125 45 Sanyo Electric Co., Ltd. 454 2 Samsung Electronics Co., Ltd.