PACKAGING IC Packaging

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Copper Wire Bond Failure Mechanisms

COPPER WIRE BOND FAILURE MECHANISMS Randy Schueller, Ph.D. DfR Solutions Minneapolis, MN ABSTRACT formation with copper wire. Wire bonding a die to a package has traditionally been performed using either aluminum or gold wire. Gold wire If copper were an easy drop-in replacement for gold the provides the ability to use a ball and stitch process. This industry would have made the change long ago. technique provides more control over loop height and bond Unfortunately copper has a few mechanical property placement. The drawback has been the increasing cost of the differences that make it more difficult to use as a wire bond gold wire. Lower cost Al wire has been used for wedge- material. Cu has a higher Young’s Modulus (13.6 vs. 8.8 2 wedge bonds but these are not as versatile for complex N/m ), thus it is harder than gold and, more significantly, package assembly. The use of copper wire for ball-stitch copper work hardens much more rapidly than gold. This bonding has been proposed and recently implemented in means that during the compression of the ball in the bonding high volume to solve the cost issues with gold. As one operation, the copper ball becomes much harder while the would expect, bonding with copper is not as forgiving as gold remains soft and deforms more easily. A thin layer of with gold mainly due to oxide growth and hardness oxide on the copper also makes bonding more challenging, differences. This paper will examine the common failure especially on the stitch side of the bond. -

Lecture 9: More About Wires and Wire Models

Lecture 9: More about wires and wire models Computer Systems Laboratory Stanford University [email protected] Copyright © 2007 Ron Ho, Mark Horowitz R Ho EE371 Lecture 9 Spring 2006-2007 1 Introduction • Readings • Today’s topics – Wires become more important with scaling • Smaller features mean faster devices but not faster wires. – Different kinds of wires have different scaled performance • Wires that scale in length • Wires that are fixed-length – How to deal with and estimate wire performance R Ho EE371 Lecture 9 Spring 2006-2007 2 A modern technology is mostly wires • Cross-section, Intel’s 65nm tech – 8 metal layers – Low-κr dielectrics (κr = 2.7) – Wires are 2x taller than wide • Wires are here • Transistors are here P. Bai, et al., “A 65nm logic technology featuring 35nm gate lengths, enhanced channel strain, 8 Cu interconnect…,” IEDM 2004. R Ho EE371 Lecture 9 Spring 2006-2007 3 Resistance, revisited… Resistance is resistivity/area, but… • Copper needs a diffusion barrier that reduces its cross-section – Also, barrier may not be evenly deposited • Copper can be overpolished – Can cause dishing (less thick) • Electrons can scatter off the edges – Happens more for thinner wires – Increases the base resistivity t w P. Kapur, “Technology and reliability constrained future copper interconnects: Resistance modeling,” IEEE Trans. Electron Devices, April 2002. R Ho EE371 Lecture 9 Spring 2006-2007 4 Capacitance, revisited… Model capacitance by four plates, each κ(A/d) • Plus a near-constant fringe term 0.1fF/um (fringe scales slowly) • Relative dielectrics differ, with low-κ within a layer – SiOF (3.5) or SiOC (2.5) – Reduces (dominant) sidewall cap – Wires are taller than they are wide κr2 •No low-κ between wire layers κr1 κr1 – For material strength κr2 s ILD A “sandwich” model R. -

Thermosonic Wire Bonding

Thermosonic Wire Bonding General Guidelines Application Note – AN1002 1. Introduction 1.1. Wire Bonding Methods Wire bonding is a solid state welding process, where two metallic materials are in intimate contact, and the rate of metallic interdiffusion is a function of temperature, force, ultrasonic power, and time. There are three wire bonding technologies: thermocompression bonding, thermosonic bonding, and ultrasonic bonding. Thermocompression bonding is performed using heat and force to deform the wire and make bonds. The main process parameters are temperature, bonding force, and time. The diffusion reactions progress exponentially with temperature. So, small increases in temperature can improve bond process significantly. In general, thermocompression bonding requires high temperature (normally above 300°C), high force, and long bonding time for adequate bonding. The high temperature and force can damage some sensitive dies. In addition, this process is very sensitive to bonding surface contaminants. Thermocompression is, therefore, seldom used now in optoelectronic and IC applications. Thermosonic bonding is performed using a heat, force, and ultrasonic power to bond a gold (Au) wire to either an Au or an aluminum (Al) surface on a substrate. Heat is applied by placing the package on a heated stage. Some bonders also have heated tool, which can improve the wire bonding performance. Force is applied by pressing the bonding tool into the wire to force it in contact with the substrate surface. Ultrasonic energy is applied by vibrating the bonding tool while it is in contact with the wire. Thermosonic process is typically used for Au wire/ribbon. Ultrasonic bonding is done at room temperature and performed by a combination of force and ultrasonic power. -

Copper Wire Bonding

Copper Wire Bonding Preeti S. Chauhan • Anupam Choubey ZhaoWei Zhong • Michael G. Pecht Copper Wire Bonding Preeti S. Chauhan Anupam Choubey Center for Advanced Life Cycle Industry Consultant Engineering (CALCE) Marlborough, MA, USA University of Maryland College Park, MD, USA Michael G. Pecht Center for Advanced Life Cycle ZhaoWei Zhong Engineering (CALCE) School of Mechanical University of Maryland & Aerospace Engineering College Park, MD, USA Nanyang Technological University Singapore ISBN 978-1-4614-5760-2 ISBN 978-1-4614-5761-9 (eBook) DOI 10.1007/978-1-4614-5761-9 Springer New York Heidelberg Dordrecht London Library of Congress Control Number: 2013939731 # Springer Science+Business Media New York 2014 This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher’s location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. -

For Copper Wire Bonds E

Body of Knowledge (BOK) for Copper Wire Bonds E. Rutkowski1 and M. J. Sampson2 1. ARES Technical Services Corporation, 2. NASA Goddard Space Flight Center Executive Summary Copper wire bonds have replaced gold wire bonds in the majority of commercial semiconductor devices for the latest technology nodes. Although economics has been the driving mechanism to lower semiconductor packaging costs for a savings of about 20% by replacing gold wire bonds with copper, copper also has materials property advantages over gold. When compared to gold, copper has approximately: 25% lower electrical resistivity, 30% higher thermal conductivity, 75% higher tensile strength and 45% higher modulus of elasticity. Copper wire bonds on aluminum bond pads are also more mechanically robust over time and elevated temperature due to the slower intermetallic formation rate – approximately 1/100th that of the gold to aluminum intermetallic formation rate. However, there are significant tradeoffs with copper wire bonding - copper has twice the hardness of gold which results in a narrower bonding manufacturing process window and requires that the semiconductor companies design more mechanically rigid bonding pads to prevent cratering to both the bond pad and underlying chip structure. Furthermore, copper is significantly more prone to corrosion issues. The semiconductor packaging industry has responded to this corrosion concern by creating a palladium coated copper bonding wire, which is more corrosion resistant than pure copper bonding wire. Also, the selection of the device molding compound is critical because use of environmentally friendly green compounds can result in internal CTE (Coefficient of Thermal Expansion) mismatches with the copper wire bonds that can eventually lead to device failures during thermal cycling. -

Chapter 9 Chip Bonding At

9 CHIP BONDING AT THE FIRST LEVEL The I/O interface to the die primarily interconnects electrical power, ground and signals. It must provide for low impedance for the power distribution system, so as to keep switching noise within specification, and controlled impedance for the signal leads to allow adequate signal integrity. In addition it must accommodate all the I/O and power and ground leads required, and at the same time, minimize the cost for high volume assembly. The secondary role of chip bonding is to be mechanically robust, not interfere with thermal man- agement and be the geometrical transformer from the die features to the next level of packaging features. There are many options for the next level of interconnect, including: ¥ leadframe in a single chip package ¥ ceramic substrate in a single chip package ¥ laminate substrate in a single chip package ¥ ceramic substrate in a multichip module ¥ laminate substrate in a multichip module ¥ glass substrate, such as an LCD (liquid crystal display) ¥ laminate substrate, such as a circuit board ¥ ceramic substrate, such as a circuit board For all of these first level interfaces, the chip bonding options are the same. Illustrated in Figure 9-1, they are: ¥ wirebond ¥ TAB (tape automated bonding) ¥ flip chip; either with a solder interface, a polymer adhesive or a welded joint Because of the parallel efforts in widely separated applications involving similar, but slightly dif- ferent variations of chip attach techniques, seemingly confusing names have historically evolved to describe some of the attach technologies. COG (chip on glass) refers to assembly of bare die onto LCD panels. -

Brass Wire Safety Data Sheet S

Brass Wire Safety Data Sheet s SECTION 1: Identification of the substance/mixture and of the company/undertaking 1.1. Product identifier Product name : Brass Wire 1.2. Relevant identified uses of the substance or mixture and uses advised against Use of the substance/mixture : Manufacturing 1.3. Details of the supplier of the safety data sheet Weiler Corporation 1 Weiler Drive Cresco, PA 18326 1.4. Emergency telephone number Emergency number : 570-595-7495 SECTION 2: Hazards identification 2.1. Classification of the substance or mixture This product as manufactured is defined as an article per 29 CFR 1910.1200. No exposure hazards are anticipated during normal product handling conditions. In most cases, the material(s) removed from the workpiece may present a greater hazard than material released by the product. Based upon the materials that are contained within the working portion of this product it is possible that some dust particles from this product may be generated. The following safety data is presented for potential exposure hazards as associated with the dust particles that are related to this product. Classification (GHS-US) Not classified 2.2. Label elements GHS-US labeling This product as manufactured is defined as an article, therefore no labeling is required for the product as manufactured. 2.3. Other hazards No additional information available 2.4. Unknown acute toxicity (GHS US) Not applicable SECTION 3: Composition/information on ingredients 3.1. Substance Not applicable 3.2. Mixture Name Product identifier % Classification (GHS-US) Copper (CAS No) 7440-50-8 69 - 70 Not classified Zinc (CAS No) 7440-66-6 29 - 31 Not classified Lead (CAS No) 7439-92-1 <= 0.07 Carc. -

PDF Package Information

This version: Apr. 2001 Previous version: Jun. 1997 PACKAGE INFORMATION 1. PACKAGE CLASSIFICATIONS This document is Chapter 1 of the package information document consisting of 8 chapters in total. PACKAGE INFORMATION 1. PACKAGE CLASSIFICATIONS 1. PACKAGE CLASSIFICATIONS 1.1 Packaging Trends In recent years, marked advances have been made in the electronics field. One such advance has been the progression from vacuum tubes to transistors and finally, to ICs. ICs themselves have been more highly integrated into LSIs, VLSIs, and now, ULSIs. With increased functions and pin counts, IC packages have had to change significantly in the last few years in order to keep-up with the advancement in semiconductor development. Functions required for conventional IC packages are as follows: 1) To protect IC chips from the external environment 2) To facilitate the packaging and handling of IC chips 3) To dissipate heat generated by IC chips 4) To protect the electrical characteristics of the IC Standard dual-in-line packages (DIP), which fulfill these basic requirements, have enjoyed wide usage in the electronics industry for a number of years. With increasing integration and higher speed ICs, and with the miniaturization of electronic equipment, newer packages have been requested by the industry which incorporate the functions listed below: 1) Multi-pin I/O 2) Ultra-miniature packages 3) Packages suited to high density ICs 4) Improved heat resistance for use with reflow soldering techniques 5) High throughput speed 6) Improved heat dissipation 7) Lower cost per pin In response to these requests, OKI has developed a diversified family of packages to meet the myriad requirements of today’s burgeoning electronics industry. -

Technical Information Handbook Wire and Cable

Technical Information Handbook Wire and Cable Fifth Edition Copyright © 2018 Trademarks and Reference Information The following registered trademarks appear in this handbook: Information in this handbook has been drawn from many Alumel® is a registered trademark of Concept Alloys, LLC publications of the leading wire and cable companies in the industry and authoritative sources in their latest available Chromel® is a registered trademark of Concept Alloys, LLC editions. Some of these include: Copperweld® is a registered trademark of Copperweld Steel Company CSA® is a registered trademark of the Canadian Standards Association • American Society for Testing and Materials (ASTM) CCW® is a registered trademark of General Cable Corporation • Canadian Standards Association (CSA) ® DataTwist is a registered trademark of Belden • Institute of Electrical and Electronics Engineers (IEEE) Duofoil® is a registered trademark of Belden Flamarrest® is a registered trademark of Belden • Insulated Cable Engineers Association (ICEA) Halar® is a registered trademark of Solvay Solexis • International Electrotechnical Commission (IEC) Hypalon® is a registered trademark of E. I. DuPont de Nemours & Company • National Electrical Manufacturers Association (NEMA) Hypot® is a registered trademark of Associated Research, Inc. • National Fire Protection Association (NFPA) IBM® is a registered trademark of International Business Machines Corporation Kapton® is a registered trademark of E. I. DuPont de Nemours & Company • Naval Ship Engineering Center (NAVSEC) Kevlar® is a registered trademark of E. I. DuPont de Nemours & Company • Telecommunications Industry Association (TIA) ® K FIBER is a registered trademark of General Cable Corporation • Underwriters Laboratories (UL). Kynar® is a registered trademark of Arkema, Inc. Loc-Trac® is a registered trademark of Alpha Wire Note: National Electrical Code (NEC) is a registered trademark of the National Fire Protection Association, Quincy, MA. -

Building Your Prototype

Building Your Prototype Prototype Construction Techniques Part Numbers Package Types Specification Sheets Schematic Diagrams Practical Advice T. Grotjohn, [email protected] Prototype Construction Techniques 1) Protoboard Use DIP components Keep your wires neat and color coded Prone to bad connections Maximum operating speed: ~ few MHz 2) Wire Wrap Often done using wire wrap sockets on a vector board Use DIP components Wire used is good for digital signals Be careful with high current lines because the wire is small. Typical wire: 30 gauge 0.34 Ω/m 28 gauge 0.21 Ω/m 3) Soldered Board Single solder points board Tied solder points board (Your mini project #1) PCB: printed circuit board PCB can be made for ECE 480 projects in the ECE Shop: See the shop’s web page. (Also see the next page) . Printed Circuit Board System General Information T-Tech Protyping Machine ECE 482 Student Project Design Department of Electrical and Computer Engineering, 1999 Michigan State University, East Lansing, Michigan, USA Part Numbers Typical Part Number: DM8095N Prefix: Indicates the manufacture of the part. See two pages in Attachment 1. Suffixes: Indicates temperature range: “military”, “industrial”, “commercial” Also the suffixes are used to indicate package types. The ECE shop deals most often with the following electronic part suppliers. Allied Electronics (www.alliedelec.com) Digi Key (www.digikey.com) Newark Electronics (www.newark.com) For other (non-electronic) supplies, suppliers often used are Grainger (www.grainger.com) McMaster Carr (www.mcmaster.com) Package Types DIP: Dual Inline Package Easiest to use. Works in protoboards, solder boards, wire wrapping, easiest to solder components to PCB This is your choice for ECE 480. -

1.Catalog of Tungsten Wire

Black Tungsten Wire Black tungsten wire is tungsten wire with graphite coated. The important applications of black tungsten wire are for the production of coiled incandescent lamp filaments, cathode and support structures for power tubes, heating elements for high temperature furnaces and evaporation sources in metalizing processes. Thicker wire sizes, straightened, finish-ground and cut into rod pieces are widely used for glass-to-metal seal lead parts in the lighting and electronic industries. Cleaned Tungsten Wire Cleaned Tungsten Wireis raised foreign elements and graphite from black tungsten wire. Cleaned Tungsten Wire is the surface of electrolytic polished tungsten wire, and it shall be smooth, clean, gray silver with metal luster. The tungsten wire features excellent formability, long life and super lighting efficiency. Cleaned tungsten wire is mainly applied for making various electron tubes, H series auto lamp, halogen lamp and other special lamp. Tungsten Rhenium Wire Tungsten rhenium wireis used for heating elements in high temperature furnaces, thermocouples and in electronics. Its advantage is its ability to maintain greater ductility compared to tungsten after exposure to extremely high temperatures. Tungsten wire has fiber structure, when the temperature reaches 1500-1600 ℃, the tungsten filament would turn, and cause high-temperature sag. To improve the quality of tungsten wire, it is always mixed some additives during sintering procession, such as Na2O, K2O, SiO2, ThO to enhance the capacity of high-temperature creep resistance and high temperature anti-sag of tungsten wire. In order to improve the tenacity of tungsten wire and prevent the deformation under high temperature, it usually added some oxides, such as silica, alumina, and potassium and so on. -

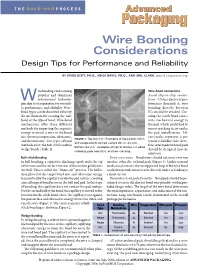

Wire Bonding Considerations Design Tips for Performance and Reliability

THE b a c k - e n d PROCESS Wire Bonding Considerations Design Tips for Performance and Reliability BY VIVEK DIXIT, PH.D., HEIDI DAVIS, PH.D., AND MEL CLARK, Maxtek Components Corp. ire bonding ranks among Wire-bond Connections popular and dominant Avoid chip-to-chip connec- W interconnect technolo- tions – Unless electrical per- gies due to its reputation for versatili- formance demands it, wire ty, performance, and reliability. Wire- bonding directly between bond types can be described either by ICs should be avoided. Cre- the mechanism for creating the wire ating the stitch bond trans- bond or the type of bond. Wire-bond mits mechanical energy to mechanisms offer three different the pad, which could lead to methods for imparting the requisite micro-cracking in, or under, energy to attach a wire to the bond the pad metallization. Mi- site: thermocompression, ultrasonic, cro-cracks represent a po- FIGURE 1. Top row (l-r) – Examples of typical ball, stitch, and thermosonic. Two types of bond and wedge bonds formed using 0.001-in. Au wire. tential reliability risk; there- methods exist: the ball-stitch and the Bottom row (l-r) – examples of typical failures, including fore, intermediate bond pads wedge bonds (Table 1). cratering, poor heel stick, and heel cracking. should be designed into the substrate. Ball-stitch Bonding Don’t cross wires – Bond wires should not cross over one In ball bonding, a capacitive discharge spark melts the tip another, other die, or bond pads (Figure 3). Under external of the wire and the surface tension of the molten gold forms mechanical stresses, the unsupported loop of the wire bond the ball.