Design and Implementation of High Speed DDR SDRAM Controller on FPGA

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Memory & Devices

Memory & Devices Memory • Random Access Memory (vs. Serial Access Memory) • Different flavors at different levels – Physical Makeup (CMOS, DRAM) – Low Level Architectures (FPM,EDO,BEDO,SDRAM, DDR) • Cache uses SRAM: Static Random Access Memory – No refresh (6 transistors/bit vs. 1 transistor • Main Memory is DRAM: Dynamic Random Access Memory – Dynamic since needs to be refreshed periodically (1% time) – Addresses divided into 2 halves (Memory as a 2D matrix): • RAS or Row Access Strobe • CAS or Column Access Strobe Random-Access Memory (RAM) Key features – RAM is packaged as a chip. – Basic storage unit is a cell (one bit per cell). – Multiple RAM chips form a memory. Static RAM (SRAM) – Each cell stores bit with a six-transistor circuit. – Retains value indefinitely, as long as it is kept powered. – Relatively insensitive to disturbances such as electrical noise. – Faster and more expensive than DRAM. Dynamic RAM (DRAM) – Each cell stores bit with a capacitor and transistor. – Value must be refreshed every 10-100 ms. – Sensitive to disturbances. – Slower and cheaper than SRAM. Semiconductor Memory Types Static RAM • Bits stored in transistor “latches” à no capacitors! – no charge leak, no refresh needed • Pro: no refresh circuits, faster • Con: more complex construction, larger per bit more expensive transistors “switch” faster than capacitors charge ! • Cache Static RAM Structure 1 “NOT ” 1 0 six transistors per bit 1 0 (“flip flop”) 0 1 0/1 = example 0 Static RAM Operation • Transistor arrangement (flip flop) has 2 stable logic states • Write 1. signal bit line: High à 1 Low à 0 2. address line active à “switch” flip flop to stable state matching bit line • Read no need 1. -

DDR and DDR2 SDRAM Controller Compiler User Guide

DDR and DDR2 SDRAM Controller Compiler User Guide 101 Innovation Drive Software Version: 9.0 San Jose, CA 95134 Document Date: March 2009 www.altera.com Copyright © 2009 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending ap- plications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. UG-DDRSDRAM-10.0 Contents Chapter 1. About This Compiler Release Information . 1–1 Device Family Support . 1–1 Features . 1–2 General Description . 1–2 Performance and Resource Utilization . 1–4 Installation and Licensing . 1–5 OpenCore Plus Evaluation . 1–6 Chapter 2. Getting Started Design Flow . 2–1 SOPC Builder Design Flow . 2–1 DDR & DDR2 SDRAM Controller Walkthrough . -

AXP Internal 2-Apr-20 1

2-Apr-20 AXP Internal 1 2-Apr-20 AXP Internal 2 2-Apr-20 AXP Internal 3 2-Apr-20 AXP Internal 4 2-Apr-20 AXP Internal 5 2-Apr-20 AXP Internal 6 Class 6 Subject: Computer Science Title of the Book: IT Planet Petabyte Chapter 2: Computer Memory GENERAL INSTRUCTIONS: • Exercises to be written in the book. • Assignment questions to be done in ruled sheets. • You Tube link is for the explanation of Primary and Secondary Memory. YouTube Link: ➢ https://youtu.be/aOgvgHiazQA INTRODUCTION: ➢ Computer can store a large amount of data safely in their memory for future use. ➢ A computer’s memory is measured either in Bits or Bytes. ➢ The memory of a computer is divided into two categories: Primary Memory, Secondary Memory. ➢ There are two types of Primary Memory: ROM and RAM. ➢ Cache Memory is used to store program and instructions that are frequently used. EXPLANATION: Computer Memory: Memory plays a very important role in a computer. It is the basic unit where data and instructions are stored temporarily. Memory usually consists of one or more chips on the mother board, or you can say it consists of electronic components that store instructions waiting to be executed by the processor, data needed by those instructions, and the results of processing the data. Memory Units: Computer memory is measured in bits and bytes. A bit is the smallest unit of information that a computer can process and store. A group of 4 bits is known as nibble, and a group of 8 bits is called byte. -

Solving High-Speed Memory Interface Challenges with Low-Cost Fpgas

SOLVING HIGH-SPEED MEMORY INTERFACE CHALLENGES WITH LOW-COST FPGAS A Lattice Semiconductor White Paper May 2005 Lattice Semiconductor 5555 Northeast Moore Ct. Hillsboro, Oregon 97124 USA Telephone: (503) 268-8000 www.latticesemi.com Introduction Memory devices are ubiquitous in today’s communications systems. As system bandwidths continue to increase into the multi-gigabit range, memory technologies have been optimized for higher density and performance. In turn, memory interfaces for these new technologies pose stiff challenges for designers. Traditionally, memory controllers were embedded in processors or as ASIC macrocells in SoCs. With shorter time-to-market requirements, designers are turning to programmable logic devices such as FPGAs to manage memory interfaces. Until recently, only a few FPGAs supported the building blocks to interface reliably to high-speed, next generation devices, and typically these FPGAs were high-end, expensive devices. However, a new generation of low-cost FPGAs has emerged, providing the building blocks, high-speed FPGA fabric, clock management resources and the I/O structures needed to implement next generation DDR2, QDR2 and RLDRAM memory controllers. Memory Applications Memory devices are an integral part of a variety of systems. However, different applications have different memory requirements. For networking infrastructure applications, the memory devices required are typically high-density, high-performance, high-bandwidth memory devices with a high degree of reliability. In wireless applications, low-power memory is important, especially for handset and mobile devices, while high-performance is important for base-station applications. Broadband access applications typically require memory devices in which there is a fine balance between cost and performance. -

Semiconductor Memories

Semiconductor Memories Prof. MacDonald Types of Memories! l" Volatile Memories –" require power supply to retain information –" dynamic memories l" use charge to store information and require refreshing –" static memories l" use feedback (latch) to store information – no refresh required l" Non-Volatile Memories –" ROM (Mask) –" EEPROM –" FLASH – NAND or NOR –" MRAM Memory Hierarchy! 100pS RF 100’s of bytes L1 1nS SRAM 10’s of Kbytes 10nS L2 100’s of Kbytes SRAM L3 100’s of 100nS DRAM Mbytes 1us Disks / Flash Gbytes Memory Hierarchy! l" Large memories are slow l" Fast memories are small l" Memory hierarchy gives us illusion of large memory space with speed of small memory. –" temporal locality –" spatial locality Register Files ! l" Fastest and most robust memory array l" Largest bit cell size l" Basically an array of large latches l" No sense amps – bits provide full rail data out l" Often multi-ported (i.e. 8 read ports, 2 write ports) l" Often used with ALUs in the CPU as source/destination l" Typically less than 10,000 bits –" 32 32-bit fixed point registers –" 32 60-bit floating point registers SRAM! l" Same process as logic so often combined on one die l" Smaller bit cell than register file – more dense but slower l" Uses sense amp to detect small bit cell output l" Fastest for reads and writes after register file l" Large per bit area costs –" six transistors (single port), eight transistors (dual port) l" L1 and L2 Cache on CPU is always SRAM l" On-chip Buffers – (Ethernet buffer, LCD buffer) l" Typical sizes 16k by 32 Static Memory -

Double-Data Rate DDR Memory Review

International Journal of Advanced Engineering and Nano Technology (IJAENT) ISSN: 2347-6389, Volume-2 Issue-2, January 2015 Double-Data Rate DDR Memory Review Ahmed Shamil Mustafa, Mohammed Jabbar Mohammed, Muthana Najim Abdulleh technique became DDR. The technology, synchronous Abstract —Computer is one most important twenty-first century dynamic random access memory (SDRAM) was discovered technology, the large volume of data and store it makes of old in the beginning 1990s to make the computer more powerful, memories are not enough. In this paper we offer a historical in that time was used Traditional DRAM an asynchronous overview of Double Data Rate (DDR) memory being play a key interface it means work independently of the processor. With role in the development of computer with also who passed him in the end of the nineties of the last century and the beginning of addition to the basics of their work and develop in the future. 2000s, specifically in 2000 became a priority for developers Index Terms —Double-Data Rate DDR, Synchronous Dynamic and manufacturers is to produce or something development Random Access Memory (SDRAM) new to increase the performance of the computer, DDR double data rate ( also called DDR 1) is a new interface I. INTRODUCTION method was developed, this made data transfer on both the In the twenty-first century with technology developments, rising and falling edges of the clock signal it has the ability to the entry of the computer at all areas of scientific and social transfer data twice faster than earlier versions, such as life. With the increased demand for computer and the large SDRAM, the had used lower clock rate (100-200MHz), less volume of data has become the task of manufacturing power (2.5v) and high speed(1600-3200 MB/s). -

Technical Note Is to Provide an Figure 9: DQS WRITE Postamble and Preamble

TN-46-05 GENERAL DDR SDRAM FUNCTIONALITY TECHNICAL GENERAL DDR SDRAM NOTE FUNCTIONALITY INTRODUCTION The migration from single data rate synchronous Table of Contents DRAM (SDR) to double data rate synchronous DRAM DDR vs. SDR Functionality ............................... 2 (DDR) memory is upon us. Although there are many Table 1: SDR to DDR Quick Reference ................. 1 similarities, DDR technology also provides notable Figure 1: Functional Block Diagram .................... 2 product enhancements. Figure 4: Example of DDR Command Bus .......... 3 In general, double data rate memory provides 2n-Prefetch Architecture ................................. 3 source-synchronous data capture at a rate of twice the Figure 2: Block Diagram 2n-Prefetch READ ........ 3 clock frequency. Therefore, a DDR266 device with a Figure 3: Block Diagram 2n-Prefetch WRITE ....... 3 clock frequency of 133 MHz has a peak data transfer rate of 266 Mb/s or 2.1 GB/s for a x64 DIMM. This is Minimum Time Slots ........................................ 3 accomplished by utilizing a 2n-prefetch architecture Figure 5: 2n-Prefetch READ Slot Timing ............. 4 where the internal data bus is twice the width of the Figure 6: 2n-Prefetch WRITE Slot Timing ............ 5 external data bus and data capture occurs twice per Figure 7: READ Command Slots ........................... 6 clock cycle. To provide high-speed signal integrity, the Strobe-Based Data Bus ..................................... 4 DDR SDRAM utilizes a bidirectional data strobe, Preamble and Postamble ................................. 7 SSTL_2 interface with differential inputs and clocks. Figure 8: DQS READ Postamble and Preamble ... 7 The objective of this technical note is to provide an Figure 9: DQS WRITE Postamble and Preamble . 8 overview of the 2n-prefetch architecture, a strobe-based SSTL_2 Interface .............................................. -

AN-371, Interfacing RC32438 with DDR SDRAM Memory

Interfacing the RC32438 with Application Note DDR SDRAM Memory AN-371 By Kasi Chopperla and Harold Gomard Notes Revision History July 3, 2003: Initial publication. October 23, 2003: Added DDR Loading section. October 29, 2003: Added Passive DDR Termination Scheme for Lightly Loaded Systems section. Introduction The RC32438 is a high performance, general-purpose, integrated processor that incorporates a 32-bit CPU core with a number of peripherals including: – A memory controller supporting DDR SDRAM – A separate memory/peripheral controller interfacing to EPROM, flash and I/O peripherals – Two Ethernet MACs – 32-bit v.2.2 compatible PCI interface – Other generic modules, such as two serial ports, I2C, SPI, interrupt controller, GPIO, and DMA. Internally, the RC32438 features a dual bus system. The CPU bus interfaces directly to the memory controller over a 32-bit bus running at CPU pipeline speed. Since it is not possible to run an external bus at the speed of the CPU, the only way to provide data fast enough to keep the CPU from starving is to use either a wider DRAM or a double data rate DRAM. As the memory technology used on PC motherboards transitions from SDRAM to DDR, the steep ramp- up in the volume of DDR memory being shipped is driving pricing to the point where DDR-based memory subsystems are primed to drop below those of traditional SDRAM modules. Anticipating this, IDT opted to incorporate a double data rate DRAM interface on its RC32438 integrated processor. DDR memory requires a VDD/2 reference voltage and combination series and parallel terminations that SDRAM does not have. -

Bioshock Infinite

SOUTH AFRICA’S LEADING GAMING, COMPUTER & TECHNOLOGY MAGAZINE VOL 15 ISSUE 10 Reviews Call of Duty: Black Ops II ZombiU Hitman: Absolution PC / PLAYSTATION / XBOX / NINTENDO + MORE The best and wors t of 2012 We give awards to things – not in a traditional way… BioShock Infi nite Loo k! Up in the sky! Editor Michael “RedTide“ James [email protected] Contents Features Assistant editor 24 THE BEST AND WORST OF 2012 Geoff “GeometriX“ Burrows Regulars We like to think we’re totally non-conformist, 8 Ed’s Note maaaaan. Screw the corporations. Maaaaan, etc. So Staff writer 10 Inbox when we do a “Best of [Year X]” list, we like to do it Dane “Barkskin “ Remendes our way. Here are the best, the worst, the weirdest 14 Bytes and, most importantly, the most memorable of all our Contributing editor 41 home_coded gaming experiences in 2012. Here’s to 2013 being an Lauren “Guardi3n “ Das Neves 62 Everything else equally memorable year in gaming! Technical writer Neo “ShockG“ Sibeko Opinion 34 BIOSHOCK INFINITE International correspondent How do you take one of the most infl uential, most Miktar “Miktar” Dracon 14 I, Gamer evocative experiences of this generation and make 16 The Game Stalker it even more so? You take to the skies, of course. Contributors 18 The Indie Investigator Miktar’s played a few hours of Irrational’s BioShock Rodain “Nandrew” Joubert 20 Miktar’s Meanderings Infi nite, and it’s left him breathless – but fi lled with Walt “Shryke” Pretorius 67 Hardwired beautiful, descriptive words. Go read them. Miklós “Mikit0707 “ Szecsei 82 Game Over Pippa -

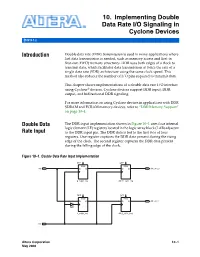

10. Implementing Double Data Rate I/O Signaling in Cyclone Devices

10. Implementing Double Data Rate I/O Signaling in Cyclone Devices C51010-1.2 Introduction Double data rate (DDR) transmission is used in many applications where fast data transmission is needed, such as memory access and first-in first-out (FIFO) memory structures. DDR uses both edges of a clock to transmit data, which facilitates data transmission at twice the rate of a single data rate (SDR) architecture using the same clock speed. This method also reduces the number of I/O pins required to transmit data. This chapter shows implementations of a double data rate I/O interface using Cyclone® devices. Cyclone devices support DDR input, DDR output, and bidirectional DDR signaling. For more information on using Cyclone devices in applications with DDR SDRAM and FCRAM memory devices, refer to “DDR Memory Support” on page 10–4. Double Data The DDR input implementation shown in Figure 10–1 uses four internal logic element (LE) registers located in the logic array block (LAB) adjacent Rate Input to the DDR input pin. The DDR data is fed to the first two of four registers. One register captures the DDR data present during the rising edge of the clock. The second register captures the DDR data present during the falling edge of the clock. Figure 10–1. Double Data Rate Input Implementation DFF DFF PRN PRN ddr DQ DQ ddr_out_h p_edge_reg ddr_h_sync_reg DFF DFF PRN PRN DQ DQ ddr_out_l NOT n_edge_reg ddr_l_sync_reg clk Altera Corporation 10–1 May 2008 Preliminary Cyclone Device Handbook, Volume 1 The third and fourth registers synchronize the two data streams to the rising edge of the clock. -

Memory Devices

Memory Devices CEN433 King Saud University Dr. Mohammed Amer Arafah 1 Types of Memory Devices Two main types of memory: ROM Read Only Memory Non Volatile data storage (remains valid after power off) For permanent storage of system software and data Can be PROM, EPROM or EEPROM (Flash) memory RAM Random Access Memory Volatile data storage (data disappears after power off) For temporary storage of application software and data Can be SRAM (static) or DRAM (dynamic) CEN433 - King Saud University 2 Mohammed Amer Arafah Memory Pin Connections Address Inputs: Select the required location in memory. Memory A0 Address lines are numbered from A1 A0 to as many as required to A2 Address . O0 address all memory locations Connections . O1 Output . Or O2 . Input/Output Example: 12-bit address: A0-A11 . Connections 12 . 2 = 4K memory locations AN OM Today’s memory devices range in capacities upto 1G locations (30 CE/ address lines) OE/ WE/ Example: 4K memory: 12 bits: 000H-FFFH. e.g. from 40000H to 40FFFH. Decode this part for CS CEN433 - King Saud University 3 Mohammed Amer Arafah Memory Pin Connections Data Inputs/Outputs (RAM) Data Outputs (ROM) Number of lines = width of data Memory A storage, usually a byte D0-D7 0 A (M=7) 1 A2 Address . O0 Connections . Wider processor data buses use . O1 Output . O Or multiple of such byte-wide . 2 . Input/Output memory devices, e.g. 64-bit . Connections AN . O 8 x 8-bit devices M CE/ Sometimes the total memory capacity is expressed in bits, e.g. OE/ a 64K x 8-bit = 512 Kbit WE/ CEN433 - King Saud University 4 Mohammed Amer Arafah Memory Pin Connections Control Inputs: Chip Enable (CE/), or Chip Select (CS/), or simply Select (S/): Select the memory device for READ or Memory WRITE operations. -

"Low-Power Support Using Texas Instruments SN74SSTV16857 and SN74SSTV16859"

Application Report SCEA020 - February 2001 Low-Power Support Using Texas Instruments SN74SSTV16857 and SN74SSTV16859 DDR-DIMM Registers Stephen M. Nolan Standard Linear & Logic ABSTRACT The Texas Instruments SN74SSTV16857 and SN74SSTV16859 registers support the low-power mode of the DDR-DIMM. This application report explains the low-power mode and the features of the registers that support the low-power mode. Also, the considerations that the system designer must be aware of when implementing the low-power state of a registered memory module are explained. The sequence that must be followed to utilize the register properly is detailed, including the interpretation of the associated register timing specifications. Finally, the different static- and dynamic-current specifications are analyzed, along with examples of how to calculate the dynamic operating current requirement of the registers. Contents Introduction . 2 Background and Features of Registers. 5 Sequence of Entering and Exiting the Low-Power State. 6 Considerations of Register. 6 How tinact and tact Are Characterized. 9 Dynamic- and Static-Current Specifications. 9 ICC Static Standby Current. 9 ICC Static Operating Current. 10 ICCD Dynamic Operating Current – Clock Only. 10 ICCD Dynamic Operating Current – Each Data Input. 11 Calculating Power Consumption in the Application. 11 Summary . 12 Glossary . 12 List of Figures 1 SN74SSTV16857 . 3 2 SN74SSTV16859 . 4 3 Parameter Measurement Information (VDD = 2.5 V ± 0.2 V). 9 1 SCEA020 Introduction The widespread demand for more main-memory capacity and bandwidth in computer systems has lead to the development of the JEDEC standard for DDR-SDRAM-based, 184-pin, registered memory modules. These DDR DIMMs provide twice the data-bus bandwidth of previous-generation single-data-rate (SDR) memory systems.