Cycles per instruction

Top View

- Acctee: a Webassembly-Based Two-Way Sandbox for Trusted Resource Accounting

- Calculation of CPI (Cycles Per Instruction)

- Application Note 93

- 6 Measuring Performance

- A Characterization of Processor Performance in the VAX-11/780

- Computer Performance

- Processor Pipelines and Static Worst-Case Execution Time Analysis

- NVIDIA CUDA Programming Guide

- Computer Architecture

- A Single-Cycle MIPS Processor

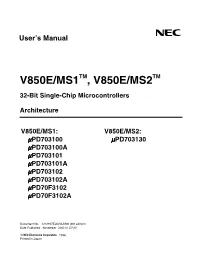

- • Uniform Instruction Format, Using a Single Word with the Opcode in The

- Performance and ISA Survey

- Sgx-Lego.Pdf

- Integrated Circuits, Performance, Power

- 45-Year CPU Evolution: One Law and Two Equations Daniel Etiemble

- CIS 501 Computer Architecture This Unit Readings Review

- Hyperflow: a Processor Architecture for Nonmalleable, Timing-Safe Information Flow Security

- CSE 30321 – Lecture 04 – in Class Example Handout