Counter (digital)

Top View

- Review Questions for Chapter 5 Computer Components

- Stored Program Concept Parts of a CPU: ! Arithmetic Logic Unit (ALU) Circuitry for Arithmetic and Logic Operations

- Computer Architecture

- Verilog Tutorial And

- A Multiplexer-Based Digital Passive Linear Counter (PLINCO)

- The Challenges, Pitfalls, and Perils of Using Hardware Performance

- Systems I: Computer Organization and Architecture

- Central Processing Unit (CPU) Or Processor – Arithmetic/Logic Unit Versus Control Unit – Registers • General Purpose • Special Purpose • Bus • Motherboard

- PART of the PICTURE: Computer Architecture 1

- Understanding Network Processors

- X86-64 Programming I CSE351, Winter 2019 X86-64 Programming I CSE 351 Winter 2019

- Instruction Set Architecture

- Efficient Memoryless Cordic for FFT Computation

- Design and Implementation of a Low Cost Digital Bus Passenger Counter

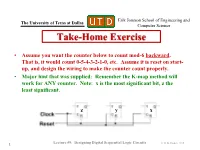

- A Random Counter in Using Shift Register and Encoder

- Processor Performance Counter Monitoring

- ABSTRACT a Common Architecture for Processing Data from Thin Film

- APMT: an Automatic Hardware Counter-Based Performance Modeling Tool