ON a GENERAL PROPERTY of MEMORY MAPPING TABLES Karl

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Latest Results from the Procedure Calling Test, Ackermann's Function

Latest results from the procedure calling test, Ackermann’s function B A WICHMANN National Physical Laboratory, Teddington, Middlesex Division of Information Technology and Computing March 1982 Abstract Ackermann’s function has been used to measure the procedure calling over- head in languages which support recursion. Two papers have been written on this which are reproduced1 in this report. Results from further measurements are in- cluded in this report together with comments on the data obtained and codings of the test in Ada and Basic. 1 INTRODUCTION In spite of the two publications on the use of Ackermann’s Function [1, 2] as a mea- sure of the procedure-calling efficiency of programming languages, there is still some interest in the topic. It is an easy test to perform and the large number of results ob- tained means that an implementation can be compared with many other systems. The purpose of this report is to provide a listing of all the results obtained to date and to show their relationship. Few modern languages do not provide recursion and hence the test is appropriate for measuring the overheads of procedure calls in most cases. Ackermann’s function is a small recursive function listed on page 2 of [1] in Al- gol 60. Although of no particular interest in itself, the function does perform other operations common to much systems programming (testing for zero, incrementing and decrementing integers). The function has two parameters M and N, the test being for (3, N) with N in the range 1 to 6. Like all tests, the interpretation of the results is not without difficulty. -

FEBRUARY 1981 R

THE ISSN 004-8917 AUSTRALIAN COMPUTER JOURNAL VOLUME 13, NUMBER 1, FEBRUARY 1981 r CONTENTS INVITED PAPER 1-6 Software and Hardware Technology for the ICL Distributed Array Processor R.W. GOSTICK ADVANCED TUTORIALS 7-12 On Understanding Binary Search B.P. KIDMAN 13-23 Some Trends in System Design Methodologies I.T. HAWRYSZKIEWYCZ SHORT COMMUNICATIONS 24-25 NEBALL and FINGRP: New Programs for Multiple Nearest- Neighbour Analysis D.J. ABEL and W.T. WILLIAMS 26 Program INVER Revisited D.J. ABEL and W.T. WILLIAMS 27-28 A Comparison between PASCAL, FORTRAN and PL/1 D.J. KEWLEY SPECIAL FEATURES 29 Book Reviews 30-31 Letters to the Editor 32 Call for Papers V J Published for Australian Computer Society Incorporated Registered for Posting as a Publication — Category B “This wouldn't have happened, Fenwick, with a Tandem NonStop™ System," When your computers down, are you out or business? You can bank on it. Timing couldn’t be worse. No question about it. Your busiest season. Customers pounding for service. When you’re on a Tandem NonStop™ System, your information All it takes is one small failure somewhere in the system. One files and your processes are protected from contamination in a disc or disc controller. One input/output channel. way no other system can match. We’ve built in safeguards other For want of an alternative, the system is down and business is suppliers can only dream about. You’ve heard the war stories about lost. Sometimes forever. restart and restore data base on other systems. They’re not exaggerations, but they can be a thing of the past. -

July 9Th Leader

Navigator browser [Sept 18] America", after the owner of the soon became the industry Seattle business park housing July 9th leader. Nintendo’s US operation, Mario Segale, demanded payment of a Andreessen authored a popular late rental bill. op-ed piece for The Wall Street ICL Formed Journal in August 2011, “Why There is, of course, no donkey in July 9, 1968 Software Is Eating the World”. “Donkey Kong”, so why “donkey”? Miyamoto apparently International Computers wanted to include “donkey” to Limited (ICL) was a large British convey stubbornness. When he computer company created first suggested it, he was through the merger of several laughed at, but the name stuck. companies, including International Computers and Tabulators (ICT [Feb 27]), English Electric Leo Marconi Tron Released (EELM), and Elliott Automation July 9, 1982 [Oct 00]. EELM was itself a merger of the computer Tron (or TRON) is a 1982 sci-fi divisions of English Electric film directed by Steven [May 10], LEO [Sept 5], and Lisberger, and partly inspired by Marconi [Dec 11]. his love of Pong [Nov 29]. Jeff Bridges, a loveably roguish The hope of the UK’s Labour programmer, is transported into Government was that ICL could the nightmarish software world compete with major world of a mainframe. manufacturers like IBM, and for Marc Andreessen (2008). Photo a while it did quite well. by Joi. CC BY 2.0. Tron was one of the first movies to make ‘extensive’ use of Its most successful product line computer animation – about 20 was the ICL 2900 series A 2015 New Yorker piece, minutes worth, CGI was used for announced on October 9, 1974. -

Principles and Practice of Database Systems Macmillan Computer Science Series Consulting Editor Professor F

Principles and Practice of Database Systems Macmillan Computer Science Series Consulting Editor Professor F. H. Sumner, University of Manchester S. T. Allworth, Introduction to Real-time Software Design Ian O. Angell, A Practical Introduction to Computer Graphics R. E. Berry and B. A. E. Meekings, A Book on C G. M. Birtwistle, Discrete Event Modelling on Simula T. B. Boffey, Graph Theory in Operations Research Richard Bornat, Understanding and Writing Compilers J. K. Buckle, The ICL 2900 Series J. K. Buckle, Software Configuration Management J. C. Cluley, Interfacing to Microprocessors Robert Cole, Computer Communications Derek Coleman, A Structured Programming Approach to Data Andrew J. T. Colin, Fundamentals ofComputer Science Andrew J. T. Colin, Programming and Problem-solving in Algol 68 S. M. Deen, Principles and Practice ofDatabase Systems P. M. Dew and K. R. James, Introduction to Numerical Computation in Pascal M. R. M. Dunsmuir and G. J. Davies, Programming the UNIX System K. C. E. Gee, Introduction to Local Area Computer Networks J. B. Gosling, Design ofArithmetic Units for Digital Computers Roger Hutty, Fortran for Students Roger Hutty, Z80 Assembly Language Programming for Students Roland N. Ibbett, The Architecture ofHigh Performance Computers P. Jaulent, The 68000 - Hardware and Software M. J. King and J. P. Pardoe, Program Design UsingJSP - A Practical Introduction H. Kopetz, Software Reliability , E. V. Krishnamurthy, Introductory Theory ofComputer Science Graham Lee, From Hardware to Software: an introduction to computers A. M. Lister, Fundamentals ofOperating Systems, third edition G. P. McKeown and V. J. Rayward-Smith,Mathematicsfor Computing Brian Meek, Fortran, PL/1 and the Algols Derrick Morris, An Introduction to System Programming - Based on the PDP11 Derrick Morris and Roland N. -

Dyalog at 25

Dyalog at 25 A special supplement to Vector Dyalog at 25 Dyalog at 25: A special supplement to Vector Published September 2008 Copyright © 2008 Dyalog Ltd Dyalog at 25 Table of Contents First Quarter ......................................................................................... 1 How we got here ................................................................................... 3 Dyadic Systems ............................................................................. 5 Dyalog (Europe) Ltd ..................................................................... 10 Writing the interpreter .................................................................. 12 Going to the show ........................................................................ 17 Ports on call ................................................................................ 19 The disappearing future ................................................................ 26 Living with Lynwood ................................................................... 29 On the road again ........................................................................ 38 Dyalog’s new face ........................................................................ 40 The ducks ................................................................................... 44 Sixty four bits .............................................................................. 45 Parting company ......................................................................... 45 The coming of the consortium ....................................................... -

E4. Catalogue of Historical Computer

Version 1: 4th March 2016. Catalogue E, for box-files E1 – E4. Catalogue of historical computer documents donated by Professor D B G Edwards. Scope. These items, donated by Professor Edwards in December 2015, cover the design of computer systems within the University of Manchester, the people involved in the projects and the growth of a Department of Computer Science. A large number of photographs is included, both of equipment, of people and of buildings. The main period covered is from 1948 – 1988, with some additional material dating from 1935 and some up to 1998. Box-files E1 & E2 contain documents and manuals. Box-files E3 & E4 (catalogued from page 10 onwards below) contain photographs. Background. David Beverley George Edwards, known to colleagues as Dai, was born in Tonteg, South Wales in 1928. In 1945 he went to Manchester University to read Physics. In his third year he specialised in Electronics and came under the influence of Professor F.C. Williams. Dai graduated in Physics in July 1948. In September of that year he became a research student working under F.C. Williams in the Department of Electro-Technics on the expansion of the ‘Baby’ (SSEM) digital computer. He obtained his MSc in December 1949 and joined the University staff as an Assistant Lecturer. Dai remained a member of the academic staff all his working life, first within Electrical Engineering and then (from 1964) within the Department of Computer Science. He was promoted to Lecturer in 1954 and gained his PhD for the design and construction of MEG. In 1959 he became a Senior Lecturer, leading the engineering team for the MUSE/Atlas project. -

Annotated Slides

ContinuingContinuing thethe ManchesterManchester ConnectionConnection Brian Procter, ICL Fellow, Chief Architect ICL High Performance Systems, West Gorton, Manchester Copyright © ICL 1998 bjp slide 1 ❑ This talk follows on from the talk given by Keith Lonsdale this morning in which he described how the Ferranti Company worked with the University to produce commercial versions of the Baby/Mk1 and its successors. ❑ The co-operation between the University and industry has been continued with the successors of Ferranti - firstly ICT and then ICL. ❑ The emphasis on “Manchester” in the title arises because the successor companies have continued to operate development facilities on the (now modernised) site occupied by Ferranti and situated a few minutes away from the University. The site is now the home of ICL High Performance Systems - the modern counterpart of the Ferranti Computer Department. Copyright © ICL 1998 1 Overview ❑ From Ferranti to ICL ❑ ICL’s 1974 New Range - VME2900 Series – Planning the 2900 – The University influence – The architecture lives on! ❑ Parallel Processing ❑ The Wider Relationship ❑ Conclusions Copyright © ICL 1998 bjp slide 2 ❑ The first part of the presentation traces the history of the formation of ICL and identifies some experiences which were to influence subsequent decisions. ❑ The main part of the presentation is devoted to a look at ICL’s VME2900 Series and its successors, and the influence the work in the University had on it. ❑ Jumping forward a decade there is a short summary of the activities on Parallel Processing described earlier by Professor Ian Watson. ❑ Before the conclusions, there is a brief reminder of the broader relationship between the University and ICL. -

THE ENGLISH ELECTRIC KDF9 by BILL FINDLAY

THE ENGLISH ELECTRIC KDF9 by BILL FINDLAY 1: KDF9 1.1: BACKGROUND AND OVERVIEW Announced in 1960, the English Electric KDF9 [Davis60] was one of the most successful products of the early UK computer industry. It still inspires great affection in former users. KDF9 offered about a third of the power of a Ferranti Atlas for about an eighth of the cost. (So much for Grosch’s Law!) Much more cost-effective than Atlas, it was also more successful in the marketplace, selling about 30 systems against a handful of the Ferranti machines. This paper presents a synoptic description of KDF9, concentrating on the system-level architecture of the English Electric (EE) hardware and software. For the nearest we have to a KDF9 programming reference manual, see [EEC69]. A relatively digestible summary of the English Electric hardware documentation can be found in [FindlayHW], and a more detailed description of the KDF9’s various software systems is given by [FindlaySW]. Even in an era of architectural experimentation, the designers of the KDF9 were bold and innovative. The CPU used separate hardware stacks for expression evaluation and for subroutine linkage. Its three concurrently running units shared the work of fetching, decoding, and executing machine-code instructions, synchronized by a variety of hardware interlocks. The KDF9 was one of the earliest fully hardware-secured multiprogramming systems. Up to four programs could be run at once under the control of its elegantly simple operating system, the Time Sharing Director. (In the UK computer parlance of the era, a ‘timesharing’ system implements multiprogramming, not multi-user interactivity.) Each program was confined to its own core area by hardware relocation, and had its own sets of working registers, which were activated when the program was dispatched, so that context switching was efficient. -

Durham E-Theses

Durham E-Theses Raster data structures and topographic data Adams, Timothy A. How to cite: Adams, Timothy A. (1982) Raster data structures and topographic data, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/7689/ Use policy The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-prot purposes provided that: • a full bibliographic reference is made to the original source • a link is made to the metadata record in Durham E-Theses • the full-text is not changed in any way The full-text must not be sold in any format or medium without the formal permission of the copyright holders. Please consult the full Durham E-Theses policy for further details. Academic Support Oce, Durham University, University Oce, Old Elvet, Durham DH1 3HP e-mail: [email protected] Tel: +44 0191 334 6107 http://etheses.dur.ac.uk University of Durham Department of Geography Raster data structures and topographic data A thesis submitted for the degree of Doctor of Philosophy in the Faculty of Science by Timothy A. Adams B.Sc, M.Sc. Graduate Society June 1982 The copyright of this thesis rests with the author. No quotation from it should be published without his prior written consent and information derived from it should be acknowledged. ABSTRACT The use of computers to assist in map-making has been growing for two decades; their speed of operation, large data storage capacity and flexibility of usage have been major factors in establishing many development and working computer mapping systems throughout the world. -

ICL Technical Journal Volume 6 Issue 1

iCl TECHNICAL JOURNAL Volume 6 Issue 1 May 1988 Published by INTERNATIONAL COMPUTERS LIMITED at OXFORD UNIVERSITY PRESS iC L - r r p u |\ |i p / \ | The ICL Technical Journal is published twice a year by ■ PV.nX.. International Computers Limited at Oxford University JOURNAL Press. Editor J. Howlett ICL House, Putney, London SW15 ISW, UK Editorial Board W.S. Harbison J. Howlett (Editor) F.F. Land H.M. Cropper (F International) (London Business School) D.W. Davies, FRS K.H. Macdonald G.E. Felton M R. Miller M.D. Godfrey (British Telecom Research (Imperial College, Fondon Laboratories) University) J.M.M. Pinkerton C.H.L. Goodman E.C.P. Portman (STLTechnology Ltd B.C. Warboys (University and King’s College,) of Manchester) London) All correspondence and papers to be considered for publication should be addressed to the Editor. The views expressed in the papersare those of the authors and do not necessarily represent ICE policy. 1987 subscription rates: annual subscription £32 UK, £40 rest of world, US $72 N. America; single issues £17 UK, £22 rest of world, US $38 N. America. Orders with remittances should be sent to the Journals Subscriptions Department, Oxford University Press, Walton Street, Oxford 0X2 6DP, UK. This publication is copyright under the Berne Convention and the Inter national Copyright Convention. All rights reserved. Apart from any copying under the UK Copyright Act 1956, part 1, section 7, whereby a single copy of an article may be supplied, under certain conditions, for the purposes of research or private study, by a library of a class prescribed by the UK Board of Trade Regulations (Statutory Instruments 1957, No. -

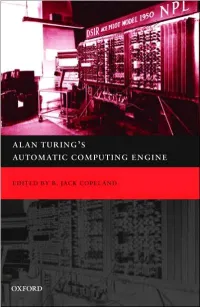

Alan Turing's Automatic Computing Engine

Alan Turing’s Automatic Computing Engine This page intentionally left blank Alan Turing’s Automatic Computing Engine The Master Codebreaker’s Struggle to Build the Modern Computer Edited by B. Jack Copeland 1 3 Great Clarendon Street, Oxford ox2 6dp Oxford University Press is a department of the University of Oxford. It furthers the University’s objective of excellence in research, scholarship, and education by publishing worldwide in Oxford NewYork Auckland CapeTown Dar es Salaam Hong Kong Karachi Kuala Lumpur Madrid Melbourne Mexico City Nairobi New Delhi Shanghai Taipei Toronto With offices in Argentina Austria Brazil Chile Czech Republic France Greece Guatemala Hungary Italy Japan Poland Portugal Singapore South Korea Switzerland Thailand Turkey Ukraine Vietnam Oxford is a registered trade mark of Oxford University Press in the UK and in certain other countries Published in the United States by Oxford University Press Inc., New York © Oxford University Press 2005 The moral rights of the author have been asserted Database right Oxford University Press (maker) First published 2005 All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, without the prior permission in writing of Oxford University Press, or as expressly permitted by law, or under terms agreed with the appropriate reprographics rights organization. Enquiries concerning reproduction outside the scope of the above should be sent to the Rights Department, Oxford University Press, at the address above You must not circulate this book in any other binding or cover and you must impose this same condition on any acquirer British Library Cataloguing in Publication Data Data available Library of Congress Cataloging in Publication Data Data available Typeset by Newgen Imaging Systems (P) Ltd., Chennai, India Printed in Great Britain on acid-free paper by Biddles Ltd., King’s Lynn, Norfolk ISBN 0 19 856593 3 (Hbk) 10987654321 This is only a foretaste of what is to come, and only the shadow of what is going to be. -

The Implementation of a Production Gold Ore Reserve System (GORS)

MILLER, S.L., BECKETT, S.A., BRA VERMAN, E. and THOMSON, P.J. The implementation of a production gold ore reserve system (GORS). APCOM 87. Proceedings of the Twentieth International Symposium on the Application of Computers and Mathematics in the Mineral Industries. Volume 3: Geostatistics. Johannesburg, SAIMM, 1987. pp. 43-51. The Implementation of a Production Gold Ore Reserve System (GORS) S.L. MILLER, S.A. BECKETT. E. BRAVERMAN and P.J. THOMSON Gold Fields of South Africa Limited, Johannesburg The development of a pilot gold geostatistical ore reserve system proved that geostatistical methods worked well for the routine production of annual ore reserves on gold mines of the Gold Fields of South Africa (GFSA) group, and that the techniques could also be practically implemented, understood and accepted by Survey Department personnel. Many side benefits of the pilot system became apparent, and a variety of useful management information was provided by manipulating the data values that were already captured. It was decided that it was a priority computing project to develop a standard production system (GORS) for routine use by all the GFSA gold mines. Ex perience with the pilot system enabled detailed functional specifications for GORS to be laid down. These, together with group computing policy deter mined the terms of reference and constraints for the GORS development. System design could not be finalized until new and appropriate mainframe database software and graphics workstation equipment and software had been found. With these in place the basic system was structured to take best ad vantage of the interactive features of the workstation, the number-crunching power of the mainframe and the flexibility offered by a relational database and associated 4GL tools.