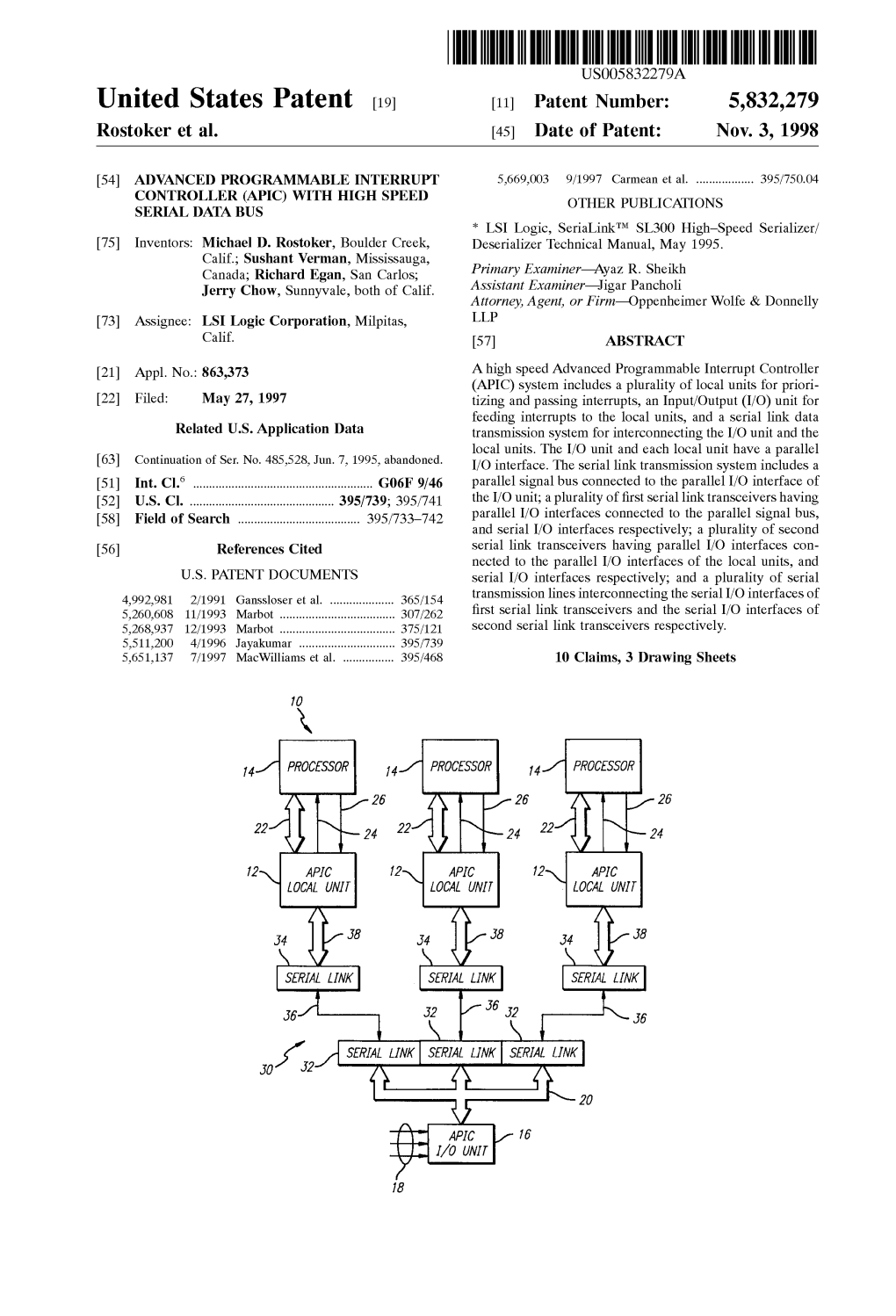

T——I- a Apic 16 I/O UNII 18 U.S

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Space Station Freedom Data Management System Growth and Evolution Report

NASA Technical Memorandum 103869 Space Station Freedom Data Management System Growth and Evolution Report R. Bartlett, G. Davis, T. L. Grant, J. Gibson, R. Hedges, M. J. Johnson, Y. K. Liu, A. Patterson-Hine, N. Sliwa, H. Sowizral, and J. Yan N93-15k77 (NASA-TM- I03869) SPACE STATION FREEDOM DATA MANAGEMENT SYSTEM GROWTH ANO EVOLU TIr}N REPORT (NASA) Uncl as September 1992 66 P G3/17 0178407 National Aeronautics and Space Administration Z NASA Technical Memorandum 103869 Space Station Freedom Data Management System Growth and Evolution Report T. L. Grant and J. Yan, Ames Research Center, Moffett Field, California September 1992 RIASA National Aeronauticsand Space Administration Ames Research Center MoffettField, CaJifomia94035-1000 The Study Team The Data Management System (DMS) analysis team Digital Equipment Corporation, Moffett Field, CA consists of civil servants and contractors at NASA Ames Roger Bartlett Research Center, Information Sciences Division. Prof. Joanne Bechta Dugan provided the reliability Intelligent Systems Technology Branch, Ames analysis of the DMS network reported in appendix B; she Research Center, Moffett Field, CA used the HARP code and the work was sponsored by Gloria Davis Langley Research Center (LaRC). Members of the Failure Terry Grant Tolerance/Redundancy Management Working Group Bob Hedges provided network failure information and preliminary Y. K. Liu models that aided our study of the failure tolerance of the Dr. Ann Patterson-Hine DMS network. Nancy Sliwa We also acknowledge the following individuals for Sterling Federal Systems, Inc., Palo Alto, CA reviewing early versions of the manuscripts: Dr. Jerry Yah Gregg Swietek (NASA Headquarters), Mike Pasciuto (NASA), Donald Woods (McDonnell Douglas Space Research Institute for Advanced Computational Systems Company (MDSSC)) and George Ganoe Science, Moffett Field, CA (NASA LaRC). -

FWB's Guide to Storage

GtoS 2nd Ed. Book Page i Friday, March 27, 1998 12:05 PM FWB’s Guide to Storage Second Edition GtoS 2nd Ed. Book Page ii Friday, March 27, 1998 12:05 PM Copyright Notice This manual is copyrighted by FWB Software, LLC (FWB) with all rights reserved. Your rights with regard to this manual are subject to the restrictions and limitations imposed by the copyright laws of the United States of Amer- ica. Under the copyright laws, this manual may not be copied, reproduced, translated, transmitted or reduced to any printed or electronic medium or to any machine-readable form, in whole or in part, without the written consent of FWB. © 1991, 1996 By FWB Software, LLC December 1996 Part No.: 07-00841-201 GtoS 2nd Ed. Book Page iii Friday, March 27, 1998 12:05 PM Trademarks Hard Disk ToolKit, RAID ToolKit, SpaceMaker ToolKit, and CD-ROM Tool- Kit are trademarks of FWB Software, LLC. FWB is a registered trademark of FWB Software, LLC. All brand and product names are trademarks or registered trademarks of their respective holders. Credits This guide was written by Norman Fong with help from Joan Carter, Steve Dalton, Bruce Dundas, Eric Herzog, Al Pierce, Stuart Saraquse, and Fred Swan. It was designed, edited, and composed by Joan Carter with help from Allan Levite. Illustrations were produced by Deane Morris. The original version of this manual was written in 1991 by Leslie Feldman, Norman Fong, Kevin Kachadourian, Neil Strudwick, and Paul Worthington as part of FWB’s Hard Disk ToolKit 1.x manual. Dedication This book is dedicated to my family and friends who put up with the long hours put into this effort. -

PC Hardware Contents

PC Hardware Contents 1 Computer hardware 1 1.1 Von Neumann architecture ...................................... 1 1.2 Sales .................................................. 1 1.3 Different systems ........................................... 2 1.3.1 Personal computer ...................................... 2 1.3.2 Mainframe computer ..................................... 3 1.3.3 Departmental computing ................................... 4 1.3.4 Supercomputer ........................................ 4 1.4 See also ................................................ 4 1.5 References ............................................... 4 1.6 External links ............................................. 4 2 Central processing unit 5 2.1 History ................................................. 5 2.1.1 Transistor and integrated circuit CPUs ............................ 6 2.1.2 Microprocessors ....................................... 7 2.2 Operation ............................................... 8 2.2.1 Fetch ............................................. 8 2.2.2 Decode ............................................ 8 2.2.3 Execute ............................................ 9 2.3 Design and implementation ...................................... 9 2.3.1 Control unit .......................................... 9 2.3.2 Arithmetic logic unit ..................................... 9 2.3.3 Integer range ......................................... 10 2.3.4 Clock rate ........................................... 10 2.3.5 Parallelism ......................................... -

LVDS(Low Voltage Differential Signaling)

Low Voltage Differential Signaling (LVDS) THE MAGAZINE FOR COMPUTER APPLICATIONS Circuit Cellar Online offers articles illustrating creative solutions and unique applications through complete projects, practical tutorials, and useful design techniques. RESOURCE PAGES A Guide to online information about: LVDS (Low Voltage Differential Signaling) by Bob Paddock At my day job, I had a project where I needed to scan almost 100 switches that covered a span of almost six feet. Complicating the matter, I did not have control over the enclosure this project would end up in. Most likely it would be a wooden box with poor ventilation. I needed a high speed technology so I would not miss multiple simultaneous switch closures when the switches where scanned, but I also needed a low-EMI technology to meet FCC part 15 guidelines (pdf), and as always the cost had to be kept low. Traditional signaling technologies like TTL/CMOS, RS-442/423, RS-485, and PECL could not move the data fast enough while maintaining low power, noise, and cost. I found Low Voltage Differential Signaling (LVDS) is the only signaling technology to meet all four criteria. The key to LVDS technology is to use a differential data-transmission scheme. Instead of designating a precise voltage level for a logic one or zero, the LVDS standard specifies a voltage differential. This approach ensures outstanding common-mode-noise immunity. Any noise introduced into the medium is seen by the receivers as common-mode modulations and is rejected. The receivers respond only to differential voltages. It is well recognized that the benefits of balanced data transmission begin http://www.chipcenter.com/circuitcellar/february00/c0200r28.htm?PRINT=true (1 of 10) [8/24/2001 7:55:23 AM] Low Voltage Differential Signaling (LVDS) to outweigh the costs over single-ended techniques when signal transition times approach 10 ns. -

Introduction to Parallel Processing : Algorithms and Architectures

Introduction to Parallel Processing Algorithms and Architectures PLENUM SERIES IN COMPUTER SCIENCE Series Editor: Rami G. Melhem University of Pittsburgh Pittsburgh, Pennsylvania FUNDAMENTALS OF X PROGRAMMING Graphical User Interfaces and Beyond Theo Pavlidis INTRODUCTION TO PARALLEL PROCESSING Algorithms and Architectures Behrooz Parhami Introduction to Parallel Processing Algorithms and Architectures Behrooz Parhami University of California at Santa Barbara Santa Barbara, California KLUWER ACADEMIC PUBLISHERS NEW YORK, BOSTON , DORDRECHT, LONDON , MOSCOW eBook ISBN 0-306-46964-2 Print ISBN 0-306-45970-1 ©2002 Kluwer Academic Publishers New York, Boston, Dordrecht, London, Moscow All rights reserved No part of this eBook may be reproduced or transmitted in any form or by any means, electronic, mechanical, recording, or otherwise, without written consent from the Publisher Created in the United States of America Visit Kluwer Online at: http://www.kluweronline.com and Kluwer's eBookstore at: http://www.ebooks.kluweronline.com To the four parallel joys in my life, for their love and support. This page intentionally left blank. Preface THE CONTEXT OF PARALLEL PROCESSING The field of digital computer architecture has grown explosively in the past two decades. Through a steady stream of experimental research, tool-building efforts, and theoretical studies, the design of an instruction-set architecture, once considered an art, has been transformed into one of the most quantitative branches of computer technology. At the same time, better understanding of various forms of concurrency, from standard pipelining to massive parallelism, and invention of architectural structures to support a reasonably efficient and user-friendly programming model for such systems, has allowed hardware performance to continue its exponential growth. -

A Bibliography of Publications in Byte Magazine: 1990–1994

A Bibliography of Publications in Byte Magazine: 1990{1994 Nelson H. F. Beebe University of Utah Department of Mathematics, 110 LCB 155 S 1400 E RM 233 Salt Lake City, UT 84112-0090 USA Tel: +1 801 581 5254 FAX: +1 801 581 4148 E-mail: [email protected], [email protected], [email protected] (Internet) WWW URL: http://www.math.utah.edu/~beebe/ 05 September 2013 Version 2.12 Title word cross-reference 100 [Ano94-129, Bry93b, HK94]. 100-Mbps [Bry93b]. 100-MHz [Ano94-129, HK94]. 1000 [Ano91u]. 10A [Ano92-73]. 110 [Nad90a]. 1120NX [Ano91e]. 1200C /Views [Api94b]. [Rei93b]. 13-pound [Nad90d]. 144 [Tho93b]. 14th [Ano92-185]. 15-to 040/120 [Ano93-60]. 040/200 [Ano93-60]. [Ano94-89]. 15th [Ano90m]. 16 [Tho90e]. 16-and [Gre94e]. 16-bit 1 [Ano90w, Ano90-51, Ano90a, Ano90-110, [Ano93-48, Ano94-88, Ano94-119, Gla90b, Ano90-113, Ano91-29, Ano93-61, Ano93-130, Sha94b, Tho94b, Wsz90]. 16-Million-Color Ano94a, Del93a, Del93b, Die90b, Far90, [Tho90e]. 16.7 [Ano91-131]. Nan90b, Pep91, Ref94]. 1-2-3 16.7-Million-Color [Ano91-131]. 165c [AR91, Gas93, Ano90-51, Ano90-110, [Tho93a]. 17-ppm [Ano93-92]. 180 Ano90-113, Ano91-29, Ano93-61, Ano94a, [Ano93-93]. 180-MBps [Ano93-93]. 1954 Del93a, Del93b, Die90b, Far90, Pep91]. [Hal94d]. 1954-1994 [Hal94d]. 1990s 1-2-3/G [Ano90-51, Die90b]. 1-megabyte [Cra91k, Lip90b, Osm90, Ras91b, Ras91o, [Tho90d, Ano90a]. 1/2 [Ano92-45]. Tho90f, VC90s, Woo91b]. 1994 [Hal94d]. 1/2-inch [Ano92-45]. 10 [Ano94-165, Nan94b]. 10-Mbps 2 [Ano91-117, Ano91-76, Ano91-131, [Ano94-165, Nan94b]. -

Solution Microcap 5 Reviewed Nulling Coil Interaction Analogue Filters Alternative Balanced Amplifier Analysing Fm Noise

EW+WW exclusivea0% off virtual instruments ELECTRONICS Denmark DKr. 65.00 Germany DM 15.00 Greece Dra.950 Holland Dfl. 14 Italy L. 8000 IR £3.30 Singapore 5S12.60 WORLD Spain Pts. 750 USA $4.94 A REED BUSINESS PUBLICATION +WIRELESS WORLD SOR DISTRIBUTION September 1995£2.10 New audio power solution MicroCap 5 reviewed Nulling coil interaction Analogue filters Alternative balanced amplifier Analysing fm noise 20% discountumaudio analyser UK launch MICROMASTER LV PROGRAMMER by marl manufActurers111(10611g AMD MICROCHIP ATMEL from only £495 THE ONLY PROGRAMMERS WITH TRUE 3 VOLT SUPPORT The Only True 3V and 5V FEATURES Widest ever device support Universal Programmers including EPROMs, EEPROMs, Flash, Serial PROMs, BPROMs, ce Technology's universal programming solutions are designed with the future in mind. In PALs, MACH, MAX, MAPL, PEELs, addition totheir comprehensive, ever widening device support, they arethe only EPLDs, Microcontrollers etc. programmers ready to correctly programme and verify 3 volt devices NOW. Operating from battery or mains power, they are flexible enough for any programming needs. Correct programming and verification of 3 volt devices. The Speedmaster LV and Micromaster LV have been rigorously tested and approved by some of the most well known names in semiconductor manufacturing today, something that very few Approved by major manufacturers. programmers can claim, especially at this price level! High speed: programmes and Not only that, we give free software upgrades so you can dial up our bulletin board any time for verifies National 27C512 in under the very latest in device support. II seconds. Speedmaster LV and Micromaster LV - they're everything you'll need for programming, chip Full range of adaptors availab e for testing and ROM emulation, now and in the future. -

AN-413 Disk Interface Design Guide and Users Manual

COP820CJ,COP840CJ,COP880C,COP884BC, COP888CF,COP888CL,COP888EK,COP888FH, COP888GW,COP8ACC5,COP8AME9,COP8CBE9, COP8CBR9,COP8CCE9,COP8CCR9,COP8CDR9, COP8SAA7,COP8SAC7,COP8SBR9,COP8SCR9, COP8SDR9,COP8SGE5,COP8SGE7,COP8SGG5, COP8SGH5,COP8SGK5,COP8SGR5,COP8SGR7, COP912C AN-413 Disk Interface Design Guide and Users Manual Literature Number: SNOA710 Disk Interface Design Guide and Users Manual AN-413 National Semiconductor Disk Interface Application Note 413 Design Guide and James Cecil Ramachandran Gopalan Users Manual William Llewellyn Shakeel Masood Pat Tucci Larry Wakeman January 1986 CHAPTER 1 DISK DRIVE TECHNOLOGYÐOVERVIEW 1.0 INTRODUCTIONÐWINCHESTER sectoring: hard sectored discs and soft sectored discs. The DRIVES hard sectored discs have sectors demarcated by the manu- facturer and are identified by a sector pulse at the start of From the start, digital computers have required some form each sector while the soft sectored discs have only an index of data storage as an adjunct to their relatively sparse main- pulse signifying the start of a track. storage facilities. Some of the early forms of storage were The more recent hard disk drives have a number of platters punched cards, paper tape and the magnetic tape storage. on the same spindle, with one head per surface. In such This was the principal storage medium, until faster-transfer, cases similar track position on each platter constitutes a higher-capacity media became available and a direct link cylinder, e.g. cylinder 0 is the cylinder corresponding to was established between the computer's main memory and track 0 on both sides of all the platters. The reading or writ- the mass storage device. This link was the rotating memo- ing of data is accomplished by the read/write head. -

LIGHTWAVE 3D RELEASE 4 Hl

Direttore Res~onsabilePerantono Palerma p Coordinamento editoriale , I I , Coordinamento Tecnico e Redazionale I i ' (te 02166034 260) DITORIALE Redazione Marna Risani (te 02166034 319) E- P p Carlo Santagostno (On~Disk) Segreteria di redazione Roberta Bottini (te1 O2166034 257) (fax 02166034 238) Coordinamento Grafico Marco Passoni Impaginazione elettronica Laura Guardnceri Copertina Sivana Cocchi ORIZZONTI Grafica pubblicitaria Renata Lavi7zari Collaboratori Roberto Attas Hnter Brnger. Paolo Canali. Roberto Cappuccio (servizi fotografici). Rocco Coluccelli. Il dado è tratto: il prossimo Amiga userà un chip Power PC. Amiga segue Antonio De Lorenzo. Fabrizio Farenga. Diego Galarate. Alberto Geneetti. Vincenzo Gervas E C Klarnm. Apple e IBM sulla strada dei RISC e si appresta a far migrare il proprio Marco e Sergio Ruocco sistema operativo anche verso altre piattaforme. La nuova macchina avrà un nuovo chipset e sarà compatibile verso il basso. Questo il succo dell'annuncio fatto in USA dal presidente di Amiga Technologies. Per vedere il Power Amiga bisognerà attendere il primo trimestre del 1997: è un tempo ragionevole, se si pensa ai problemi che comporta il porting di un IL NUMERO UNO NEM RIVISE SPECIAUZZAiE sistema operativo da CISC a RISC. Nel frattempo, per permettere anche a Presidente Peter F Tordoir tutta I'utenza Amiga di non restare tagliata fuori dallo sviluppo della macchi- Amministratore Delegato Pterantono Pacrma na, saranno messe a punto schede acceleratrici con Power PC per i modelli Periodici e Pubblicita Peter Godsten Publisher Itao Cattaneo esistenti, 1200 compreso. Tale compito è stato affidato da AT alla tedesca Coordinamento Operativo Antonio Parmendola Phase 5, che ha già presentato un prototipo alla fiera di Colonia. -

Coherent Data Collectors: a Hardware Perspective

COHERENT DATA COLLECTORS: A HARDWARE PERSPECTIVE Coherent Data Collectors: A Hardware Perspective Russell Rzemien For more than 15 years, the Applied Physics Laboratory has been designing and operating coherent radar data-collection instrumentation. In this article, the engineer- ing challenges and design approaches used to meet analysis requirements are described, examples of collectors are provided, and the nature of future development efforts is outlined. (Keywords: Coherent signal processing, Radar analysis, Radar instrumentation, Radar systems, Test and evaluation.) INTRODUCTION Radar1–3 is an acronym derived from the words radio processors that only use amplitude information may fail detection and ranging. The term reveals much about to detect these targets in such environments. the operation and use of early radars. Those first devices Far better performance is achieved by coherent ra- used radio waves to detect the presence of objects and dars, i.e., radars that use the phase or frequency infor- to measure the ranges of those objects. Modern radars mation of the return echoes and not just the amplitude frequently provide additional information, such as of the return signal. An echo’s phase (or frequency) angular position and inbound velocity of an approach- remains constant for stationary objects like clutter, ing target. However, the primary function of radar is whereas the phase varies for moving objects. It is this target detection; all else follows from this. The detec- changing phase, along with the amplitude of the echo, tion problem remains a challenge, particularly with the that the signal processors in coherent radars use to development of stealth design techniques that signif- discriminate targets from background clutter. -

Moving Media Storage Technologies Applications & Workflows for Video and Media Server Platforms

Moving Media Storage Technologies Applications & Workflows for Video and Media Server Platforms Karl Paulsen CONTENTS Acknowledgments xv Introduction xvii Chapter 1 Information, Data, and Video 1 Data Structure 1 Information 2 Storing the Moving Image 3 Digital Video Recording 4 Analog Component Video 5 Colorimetry and Conversion 11 A Digital Media World: Going Forward 12 Further Readings 13 Chapter 2 Digital Disk Recording 15 Recording Moving Images 16 Dawn of the Video Disk 17 Fundamentals of Digital Disk Recording 18 Core Technologies for Digital Disk Recording 21 DDR, DVR, or VideoServer 28 Comparing DDRs to VideoServers 31 Clip Servers 32 DVR Marketplaces 35 Home Media Network Disk Recorders 36 Audio 37 Further Readings 38 Chapter 3 Video Media Servers 39 Carrying Over from the DDR 39 Universal Server Approach 41 VideoServers as Media Servers 46 The Future of VideoServers 66 Communications Protocols Used in Video Serving Platforms 66 Further Readings 71 Chapter 4 Hard Drive Anatomy 73 Magnetic Recording History 74 Drive Components 77 Disk Performance Optimization 85 Disk Scheduling 85 Access Time Components 87 Servicing and Scheduling Criteria 88 Capacity Factors, Transfer Time and Obstacles 95 Read-Write Heads 97 Advanced Format Sector Technology 102 Superparamagnetic Limit 106 Heat-Assisted Magnetic Recording. 107 Further Reading 108 Chapter 5 Buses, Ports, and Interfaces 109 Carrying and Transferring Data 110 Bus Types 110 Storage Bus Standards 112 Storage Module Device 112 Serial Storage Architecture 114 High-Performance Parallel -

Portovi Personalnih Računara 50

Elektronski fakultet u Nišu Katedra za elektroniku Portovi i magistrale Student: Mentor: Vladimir Stefanović 11422 prof. dr Mile Stočev Milan Jovanović10236 Sadržaj Uvod 3 1.Magistrale 4 2.Portovi dati alfabetnim redom 36 3.Portovi personalnih računara 50 4.Poređenja i opisi PC interfejsa i portova 59 5.Hardver – mehaničke komponente 126 2 Uvod Sam rad se sastoji iz 5 dela u kojima su detaljno opisani PC portovi, magistrale, kao i razlike i sličnosti koje među njima postoje. U prvom poglavlju data je opšta podela magistrala, ukratko je opisan njihov način funkcionisanja, dati su odgovarajući standardi, generacije, a ukratko su opisane i suerbrze magistrale. U drugom poglavlju dat je alfabetni spisak portova, od kojih je većina obuhvaćena ovim radom. Treće poglavlje odnosi se na portove personalnih računara, kako Pentium tako i Apple i Mackintosh. Četvrti deo odnosi se na opisane portove i interfejse i njihovo međusobno poređenje. U ovom poglavlju date su i detaljne tabele u kojima su navedene i opisane neke od najvažnijih funkcija. I konačno, peto poglavlje se odnosi na hardver – USB portove, memorijske kartice SCSI portove. U Nišu, 03.10.2008. godine 3 1. Magistrale Prilagodljivost personalnog računara - njegova sposobnost da se proširi pomoću više vrsta interfejsa dozvoljavajući priključivanje mnogo različitih klasa dodatnih sastavnih delova i periferijskih uredjaja - bila je jedan od ključnnih razloga njegovog uspeha. U suštini, moderni PC računarski sistem malo se razlikuje od originalne IBM konstrukcije - to je skup komponenata, kako unutrašnjih tako i spoljašnjih, medjusobno povezanih pomoću elektronskih magistrala, preko kojih podaci putuju, dok se obavlja ciklus obrade koji ih pretvara od podataka ulaza u podatke izlaza.