Intel® Server Board SE7320EP2 / Intel® Server Board SE7525RP2

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

SAMPLE CHAPTER 1 Chapter Personal Computer 1 System Components the FOLLOWING COMPTIA A+ ESSENTIALS EXAM OBJECTIVES ARE COVERED in THIS CHAPTER

SAMPLE CHAPTER 1 Chapter Personal Computer 1 System Components THE FOLLOWING COMPTIA A+ ESSENTIALS EXAM OBJECTIVES ARE COVERED IN THIS CHAPTER: Ûß1.2 Explain motherboard components, types and features Nß Form Factor Nß ATX / BTX, Nß micro ATX Nß NLX Nß I/O interfaces Material Nß Sound Nß Video Nß USB 1.1 and 2.0 Nß Serial Nß IEEE 1394 / FireWire Nß Parallel Nß NIC Nß Modem Nß PS/2 Nß Memory slots Nß RIMM Nß DIMM Nß SODIMM CopyrightedNß SIMM Nß Processor sockets Nß Bus architecture 86498book.indb 1 7/22/09 5:37:17 AM Nß Bus slots Nß PCI Nß AGP Nß PCIe Nß AMR Nß CNR Nß PCMCIA Chipsets Nß BIOS / CMOS / Firmware Nß POST Nß CMOS battery Nß Riser card / daughterboard Nß [Additional subobjectives covered in chapter 2] Ûß1.4 Explain the purpose and characteristics of CPUs and their features Nß Identify CPU types Nß AMD Nß Intel Nß Hyper threading Nß Multi core Nß Dual core Nß Triple core Nß Quad core Nß Onchip cache Nß L1 Nß L2 Nß Speed (real vs. actual) Nß 32 bit vs. 64 bit Ûß1.5 Explain cooling methods and devices Nß Heat sinks Nß CPU and case fans 86498book.indb 2 7/22/09 5:37:18 AM Nß Liquid cooling systems Nß Thermal compound Ûß1.6 Compare and contrast memory types, characteristics and their purpose Nß Types Nß DRAM Nß SRAM Nß SDRAM Nß DDR / DDR2 / DDR3 Nß RAMBUS Nß Parity vs. Non-parity Nß ECC vs. non-ECC Nß Single sided vs. double sided Nß Single channel vs. -

VX97 User's Manual ASUS CONTACT INFORMATION Asustek COMPUTER INC

R VX97 Pentium Motherboard USER'S MANUAL USER'S NOTICE No part of this manual, including the products and softwares described in it, may be repro- duced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means, except documentation kept by the purchaser for backup pur- poses, without the express written permission of ASUSTeK COMPUTER INC. (“ASUS”). ASUS PROVIDES THIS MANUAL “AS IS” WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OR CONDITIONS OF MERCHANTABILITY OR FITNESS FOR A PAR- TICULAR PURPOSE. IN NO EVENT SHALL ASUS, ITS DIRECTORS, OFFICERS, EMPLOYEES OR AGENTS BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDEN- TAL, OR CONSEQUENTIAL DAMAGES (INCLUDING DAMAGES FOR LOSS OF PROFITS, LOSS OF BUSINESS, LOSS OF USE OR DATA, INTERRUPTION OF BUSI- NESS AND THE LIKE), EVEN IF ASUS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES ARISING FROM ANY DEFECT OR ERROR IN THIS MANUAL OR PRODUCT. Products and corporate names appearing in this manual may or may not be registered trade- marks or copyrights of their respective companies, and are used only for identification or explanation and to the owners’ benefit, without intent to infringe. • Intel, LANDesk, and Pentium are registered trademarks of Intel Corporation. • IBM and OS/2 are registered trademarks of International Business Machines. • Symbios is a registered trademark of Symbios Logic Corporation. • Windows and MS-DOS are registered trademarks of Microsoft Corporation. • Sound Blaster AWE32 and SB16 are trademarks of Creative Technology Ltd. • Adobe and Acrobat are registered trademarks of Adobe Systems Incorporated. -

Lista Sockets.Xlsx

Data de Processadores Socket Número de pinos lançamento compatíveis Socket 0 168 1989 486 DX 486 DX 486 DX2 Socket 1 169 ND 486 SX 486 SX2 486 DX 486 DX2 486 SX Socket 2 238 ND 486 SX2 Pentium Overdrive 486 DX 486 DX2 486 DX4 486 SX Socket 3 237 ND 486 SX2 Pentium Overdrive 5x86 Socket 4 273 março de 1993 Pentium-60 e Pentium-66 Pentium-75 até o Pentium- Socket 5 320 março de 1994 120 486 DX 486 DX2 486 DX4 Socket 6 235 nunca lançado 486 SX 486 SX2 Pentium Overdrive 5x86 Socket 463 463 1994 Nx586 Pentium-75 até o Pentium- 200 Pentium MMX K5 Socket 7 321 junho de 1995 K6 6x86 6x86MX MII Slot 1 Pentium II SC242 Pentium III (Cartucho) 242 maio de 1997 Celeron SEPP (Cartucho) K6-2 Socket Super 7 321 maio de 1998 K6-III Celeron (Socket 370) Pentium III FC-PGA Socket 370 370 agosto de 1998 Cyrix III C3 Slot A 242 junho de 1999 Athlon (Cartucho) Socket 462 Athlon (Socket 462) Socket A Athlon XP 453 junho de 2000 Athlon MP Duron Sempron (Socket 462) Socket 423 423 novembro de 2000 Pentium 4 (Socket 423) PGA423 Socket 478 Pentium 4 (Socket 478) mPGA478B Celeron (Socket 478) 478 agosto de 2001 Celeron D (Socket 478) Pentium 4 Extreme Edition (Socket 478) Athlon 64 (Socket 754) Socket 754 754 setembro de 2003 Sempron (Socket 754) Socket 940 940 setembro de 2003 Athlon 64 FX (Socket 940) Athlon 64 (Socket 939) Athlon 64 FX (Socket 939) Socket 939 939 junho de 2004 Athlon 64 X2 (Socket 939) Sempron (Socket 939) LGA775 Pentium 4 (LGA775) Pentium 4 Extreme Edition Socket T (LGA775) Pentium D Pentium Extreme Edition Celeron D (LGA 775) 775 agosto de -

Intel® Server Board SE7505VB2

Intel® Server Board SE7505VB2 Technical Product Specification Intel part number C32194-002 Revision 1.2 April 2004 Enterprise Platforms and Services Marketing Revision History Intel® Server Board SE7505VB2 Revision History Date Revision Number Modifications January 2003 1.0 Initial Release Added memory cooling duct information, added section on BIOS event March 2003 1.1 log, incorporated Technology Leadership terminology, and corrected miscellaneous minor technical details. April 2004 1.2 New graphics for Mechanical Changes. ii Revision 1.2 Intel part number C32194-002 Intel® Server Board SE7505VB2 Disclaimers Disclaimers Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The SE7505VB2 server system may contain design defects or errors known as errata that may cause the product to deviate from published specifications. -

Socket E Slot Per

Socket e Slot per CPU Socket e Slot per CPU Socket 1 Socket 2 Socket 3 Socket 4 Socket 5 Socket 6 Socket 7 e Super Socket 7 Socket 8 Slot 1 (SC242) Slot 2 (SC330) Socket 370 (PGA-370) Slot A Socket A (Socket 462) Socket 423 Socket 478 Socket 479 Socket 775 (LGA775) Socket 603 Socket 604 PAC418 PAC611 Socket 754 Socket 939 Socket 940 Socket AM2 (Socket M2) Socket 771 (LGA771) Socket F (Socket 1207) Socket S1 A partire dai processori 486, Intel progettò e introdusse i socket per CPU che, oltre a poter ospitare diversi modelli di processori, ne consentiva anche una rapida e facile sostituzione/aggiornamento. Il nuovo socket viene definito ZIF (Zero Insertion Force ) in quanto l'inserimento della CPU non richiede alcuna forza contrariamente ai socket LIF ( Low Insertion Force ) i quali, oltre a richiedere una piccola pressione per l'inserimento del chip, richiedono anche appositi tool per la sua rimozione. Il modello di socket ZIF installato sulla motherboard è, in genere, indicato sul socket stesso. Tipi diversi di socket accettano famiglie diverse di processori. Se si conosce il tipo di zoccolo montato sulla scheda madre è possibile sapere, grosso modo, che tipo di processori può ospitare. Il condizionale è d'obbligo in quanto per sapere con precisione che tipi di processore può montare una scheda madre non basta sapere solo il socket ma bisogna tenere conto anche di altri fattori come le tensioni, il FSB, le CPU supportate dal BIOS ecc. Nel caso ci si stia apprestando ad aggiornare la CPU è meglio, dunque, attenersi alle informazioni sulla compatibilità fornite dal produttore della scheda madre. -

Intel® Server Board S2600 Family BIOS Setup User Guide

Intel® Server Board S2600 Family BIOS Setup User Guide For the Intel® Server Board S2600 family supporting the Intel® Xeon processor Scalable family and 2nd Generation Intel® Xeon processor Scalable family. Rev 1.1 November 2019 Intel® Server Products and Solutions Intel® Server Board BIOS Setup Specification Document Revision History Date Revision Changes October 2017 1.0 First release based on Intel® Server Board S2600 Family BIOS Setup Utility Specification. November 2019 1.1 Update based on Intel Xeon Processor Scalable Family Refresh BIOS Setup Specification 1_13 2 Intel® Server Board BIOS Setup Specification Disclaimers Intel technologies’ features and benefits depend on system configuration and may require enabled hardware, software, or service activation. Learn more at Intel.com, or from the OEM or retailer. You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein. No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document. The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade. -

Instituto De Formación Técnica Profesional “INFOTEP” 2012/2014

Instituto De Formación Técnica Profesional “INFOTEP” 2012/2014 Características del Computador: Una computadora o computador (del inglés computer y este del latín computare -calcular), también denominada ordenador (del francés ordinateur, y este del latín ordinator), es una máquina electrónica que recibe y procesa datos para convertirlos en información útil. Una computadora es una colección de circuitos integrados y otros componentes electronicos relacionados que puede ejecutar con exactitud, rapidez y de acuerdo a lo indicado por un usuario o automáticamente por otro programa, una gran variedad de secuencias o rutinas de instrucciones que son ordenadas, organizadas y sistematizadas en función a una amplia gama de aplicaciones prácticas y precisamente determinadas, proceso al cual se le ha denominado con el nombre de programación y al que lo realiza se le llama programador. La computadora, además de la rutina o programa informático, necesita de datos específicos (a estos datos, en conjunto, se les conoce como "Input" en inglés o de entrada) que deben ser suministrados, y que son requeridos al momento de la ejecución, para proporcionar el producto final del procesamiento de datos, que recibe el nombre de "output" o de salida. La información puede ser entonces utilizada, reinterpretada, copiada, transferida, o retransmitida a otra(s) persona(s), computadora(s) o componente(s) electrónico(s) local o remotamente usando diferentes sistemas de telecomunicación, pudiendo ser grabada, salvada o almacenada en algún tipo de dispositivo o unidad de almacenamiento. WWW.INFOTEP.CREATUPROPIAWEB.COM PROF: ROQUE CARDENAS 0416-8764700 1 Instituto De Formación Técnica Profesional “INFOTEP” 2012/2014 Placa madre/Mainboard/Motherboard: La placa base, también conocida como placa madre o tarjeta madre (del inglés motherboard o mainboard) es una tarjeta de circuito impreso a la que se conectan los componentes que constituyen la computadora u ordenador. -

Quad-Core Intel® Xeon® Processor 5400 Series

Quad-Core Intel® Xeon® Processor 5400 Series Datasheet August 2008 318589-005 INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The Quad-Core Intel® Xeon® Processor 5400 Series may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. 64-bit computing on Intel architecture requires a computer system with a processor, chipset, BIOS, operating system, device drivers and applications enabled for Intel® 64 architecture. Processors will not operate (including 32-bit operation) without an Intel® 64 architecture-enabled BIOS. Performance will vary depending on your hardware and software configurations. Consult with your system vendor for more information. -

Intel Xeon Processor 7200 Series and 7300 Series and Dual-Core Intel® Xeon® Processor 7200 Series

Intel® Xeon® Processor 7200 Series and 7300 Series Datasheet September 2008 Notice: The Intel® Xeon® Processor 7200 Series and 7300 Series may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Document Number: 318080-002 INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The Intel® Xeon® Processor 7200 Series and 7300 Series may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. -

AP1600R Dual Intel¨ Xeonª 1U Rackmount Server

AP1600R Dual Intel® Xeon™ 1U Rackmount Server User Guide Disclaimer/Copyrights No part of this manual, including the products and software described in it, may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means, except documentation kept by the purchaser for backup purposes, without the express written permission of ASUSTeK COMPUTER INC. (“ASUS”). ASUS PROVIDES THIS MANUAL “AS IS” WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OR CONDITIONS OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. IN NO EVENT SHALL ASUS, ITS DIRECTORS, OFFICERS, EMPLOYEES OR AGENTS BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES (INCLUDING DAMAGES FOR LOSS OF PROFITS, LOSS OF BUSINESS, LOSS OF USE OR DATA, INTERRUPTION OF BUSINESS AND THE LIKE), EVEN IF ASUS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES ARISING FROM ANY DEFECT OR ERROR IN THIS MANUAL OR PRODUCT. Product warranty or service will not be extended if: (1) the product is repaired, modified or altered, unless such repair, modification of alteration is authorized in writing by ASUS; or (2) the serial number of the product is defaced or missing. Products and corporate names appearing in this manual may or may not be registered trademarks or copyrights of their respective companies, and are used only for identification or explanation and to the owners’ benefit, without intent to infringe. The product name and revision number are both printed on the product itself. Manual revisions are released for each product design represented by the digit before and after the period of the manual revision number. -

Typy Gniazd I Procesorów

TYPY GNIAZD I PROCESORÓW AMD Socket • Socket 5 - AMD K5. • Socket 7 - AMD K6. • Super Socket 7 - AMD K6-2, AMD K6-III. • Socket 462 (zwany tak Ŝe Socket A) - AMD Athlon, Duron, Athlon XP, Athlon XP-M, Athlon MP, i Sempron. • Socket 463 (zwany tak Ŝe Socket NexGen) - NexGen Nx586. • Socket 563 - AMD Athlon XP-M (µ-PGA Socket). • Socket 754 - AMD Athlon 64, Sempron, Turion 64. Obsługa pojedynczego kanału pami ęci DDR-SDRAM, tzw. single-channel. • Socket 939 - AMD Athlon 64, Athlon 64 FX, Athlon 64 X2, Sempron, Turion 64, Opteron (seria 100). Obsługa podwójnego kanału pami ęci DDR-SDRAM, tzw. dual-channel. • Socket 940 - AMD Opteron (seria 100, 200, 800), Athlon 64 FX. Obsługa podwójnego kanału pami ęci DDR-SDRAM, tzw. dual- channel. • Socket 1207 (zwane tak Ŝe Socket F) - Supports AMD Opteron (seria 200, 800). Zast ąpił Socket 940. Obsługa dual-channel DDR2- SDRAM. • Socket AM2 - AMD Athlon 64 FX, Athlon 64 X2, Sempron, Turion 64, Opteron (seria 100). Obsługa dual-channel DDR2-SDRAM. Posiada 940 pinów. • Socket AM2+ - AMD Athlon X2, Athlon X3, Athlon X4, Phenom X2, Phenom X3, Phenom X4, Sempron, Phenom II. Obsługa dual- channel DDR2-SDRAM, oraz Obsługa dual-channel DDR3-SDRAM i HyperTransport 3 z mniejszym zapotrzebowaniem na energi ę. Posiada 940 pinów. • Socket AM3 - gniazdo pod procesor AMD, charakteryzuj ący si ę obsług ą dual-channel DDR3-SDRAM, oraz HyperTransport 3. Phenom II X2, Phenom X3, Phenom X4, Phenom X6, Athlon II X2, Athlon X3, Athlon X4, Sempron. • Socket FM1 - gniazdo pod procesor AMD Vision z nowej serii APU, wykonany w w 32 nanometrowym procesie produkcyjnym. -

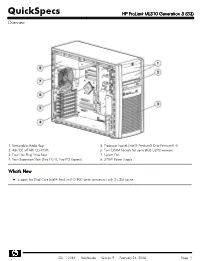

HP Proliant ML310 Generation 3 (G3) Overview

QuickSpecs HP ProLiant ML310 Generation 3 (G3) Overview 1. Removable Media Bays 5. Processor Socket (Intel® Pentium® D or Pentium® 4) 2. 48x IDE (ATAPI) CD-ROM 6. Four DIMM Sockets for up to 8GB DDR2 memory 3. Four Hot-Plug Drive Bays 7. System Fan 4. Four Expansion Slots (Two PCI-X, Two PCI Express) 8. 370W Power Supply What's New Support for Dual Core Intel® Pentium® D 900 Series processors with 2 x 2M cache DA - 12364 Worldwide — Version 9 — February 24, 2006 Page 1 QuickSpecs HP ProLiant ML310 Generation 3 (G3) Overview At A Glance Supports a single Intel® Pentium® D 800 or 900 Series, Pentium® 4 600 Series, or Celeron D® 300 Series processor Intel E7230 Chipset - 800MHz front side bus PC2-4200 533MHz unbuffered DDR2 SDRAM with advanced ECC capabilities and optional interleaving (expandable to 8 GB) Embedded NC320i PCI Express 10/100/1000T Gigabit network adapter Four Expansion Slots: Two PCI-X 64-bit/100MHz, Two PCI Express Supports four hot plug SCSI, SAS, or SATA hard drives for up to 2TB internal storage. SCSI models support U320 SCSI drives. Serial models support SAS and SATA hard drives Single Channel U320 SCSI Adapter in PCI-X slot (SCSI models) or four Channel embedded SATA Controller (SATA models) Integrated Lights-Out 2 (iLO 2) management controller Four USB 2.0 ports - Two front, two rear ROM Based Setup Utility (RBSU) and PXE support Protected by HP Services and a worldwide network of resellers and service providers. One year, Next Business Day, on-site limited global warranty.