Timeline of Computer History

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

1 Oral History Interview with Brian Randell January 7, 2021 Via Zoom

Oral History Interview with Brian Randell January 7, 2021 Via Zoom Conducted by William Aspray Charles Babbage Institute 1 Abstract Brian Randell tells about his upbringing and his work at English Electric, IBM, and Newcastle University. The primary topic of the interview is his work in the history of computing. He discusses his discovery of the Irish computer pioneer Percy Ludgate, the preparation of his edited volume The Origins of Digital Computers, various lectures he has given on the history of computing, his PhD supervision of Martin Campbell-Kelly, the Computer History Museum, his contribution to the second edition of A Computer Perspective, and his involvement in making public the World War 2 Bletchley Park Colossus code- breaking machines, among other topics. This interview is part of a series of interviews on the early history of the history of computing. Keywords: English Electric, IBM, Newcastle University, Bletchley Park, Martin Campbell-Kelly, Computer History Museum, Jim Horning, Gwen Bell, Gordon Bell, Enigma machine, Curta (calculating device), Charles and Ray Eames, I. Bernard Cohen, Charles Babbage, Percy Ludgate. 2 Aspray: This is an interview on the 7th of January 2021 with Brian Randell. The interviewer is William Aspray. We’re doing this interview via Zoom. Brian, could you briefly talk about when and where you were born, a little bit about your growing up and your interests during that time, all the way through your formal education? Randell: Ok. I was born in 1936 in Cardiff, Wales. Went to school, high school, there. In retrospect, one of the things I missed out then was learning or being taught Welsh. -

Validated Products List, 1995 No. 3: Programming Languages, Database

NISTIR 5693 (Supersedes NISTIR 5629) VALIDATED PRODUCTS LIST Volume 1 1995 No. 3 Programming Languages Database Language SQL Graphics POSIX Computer Security Judy B. Kailey Product Data - IGES Editor U.S. DEPARTMENT OF COMMERCE Technology Administration National Institute of Standards and Technology Computer Systems Laboratory Software Standards Validation Group Gaithersburg, MD 20899 July 1995 QC 100 NIST .056 NO. 5693 1995 NISTIR 5693 (Supersedes NISTIR 5629) VALIDATED PRODUCTS LIST Volume 1 1995 No. 3 Programming Languages Database Language SQL Graphics POSIX Computer Security Judy B. Kailey Product Data - IGES Editor U.S. DEPARTMENT OF COMMERCE Technology Administration National Institute of Standards and Technology Computer Systems Laboratory Software Standards Validation Group Gaithersburg, MD 20899 July 1995 (Supersedes April 1995 issue) U.S. DEPARTMENT OF COMMERCE Ronald H. Brown, Secretary TECHNOLOGY ADMINISTRATION Mary L. Good, Under Secretary for Technology NATIONAL INSTITUTE OF STANDARDS AND TECHNOLOGY Arati Prabhakar, Director FOREWORD The Validated Products List (VPL) identifies information technology products that have been tested for conformance to Federal Information Processing Standards (FIPS) in accordance with Computer Systems Laboratory (CSL) conformance testing procedures, and have a current validation certificate or registered test report. The VPL also contains information about the organizations, test methods and procedures that support the validation programs for the FIPS identified in this document. The VPL includes computer language processors for programming languages COBOL, Fortran, Ada, Pascal, C, M[UMPS], and database language SQL; computer graphic implementations for GKS, COM, PHIGS, and Raster Graphics; operating system implementations for POSIX; Open Systems Interconnection implementations; and computer security implementations for DES, MAC and Key Management. -

Technical Details of the Elliott 152 and 153

Appendix 1 Technical Details of the Elliott 152 and 153 Introduction The Elliott 152 computer was part of the Admiralty’s MRS5 (medium range system 5) naval gunnery project, described in Chap. 2. The Elliott 153 computer, also known as the D/F (direction-finding) computer, was built for GCHQ and the Admiralty as described in Chap. 3. The information in this appendix is intended to supplement the overall descriptions of the machines as given in Chaps. 2 and 3. A1.1 The Elliott 152 Work on the MRS5 contract at Borehamwood began in October 1946 and was essen- tially finished in 1950. Novel target-tracking radar was at the heart of the project, the radar being synchronized to the computer’s clock. In his enthusiasm for perfecting the radar technology, John Coales seems to have spent little time on what we would now call an overall systems design. When Harry Carpenter joined the staff of the Computing Division at Borehamwood on 1 January 1949, he recalls that nobody had yet defined the way in which the control program, running on the 152 computer, would interface with guns and radar. Furthermore, nobody yet appeared to be working on the computational algorithms necessary for three-dimensional trajectory predic- tion. As for the guns that the MRS5 system was intended to control, not even the basic ballistics parameters seemed to be known with any accuracy at Borehamwood [1, 2]. A1.1.1 Communication and Data-Rate The physical separation, between radar in the Borehamwood car park and digital computer in the laboratory, necessitated an interconnecting cable of about 150 m in length. -

IBM Thinkpad Notebooks 1992 to 2001 - Withdrawn January 2001 - Version 214 IBM Thinkpad 240 - Withdrawn

IBM PC Institute IBM Personal Systems Reference IBM ThinkPad Notebooks 1992 to 2001 - withdrawn January 2001 - Version 214 IBM ThinkPad 240 - withdrawn IBM ThinkPad Processor Intel Mobile Celeron 300, 366, or 400MHz1 / 66MHz system bus Processor features No upgrade / processor on Ball Grid Array (H-PBGA) L2 cache 128KB / onboard (full speed) / synchronous pipelined burst / ECC / write-back Diskette drive External 3.5" 1.44MB / connects to left side with FDD port / includes case and cable CD-ROM Option: External CD-ROM / via Portable Drive Bay and 24X-10X5 CD-ROM UltraslimBay Drive DVD-ROM Option: External DVD-ROM / via Portable Drive Bay and DVD-ROM UltraslimBay Drive Type-model ✂ 2609-21U ✂ 2609-31U ✂ 2609-41U Processor Celeron 300MHz Celeron 366MHz Celeron 400MHz Disk - size / ms 6.4GB4 / 13ms read / Ultra DMA/33 or PIO Mode 4 12.0GB / 12ms read / ATA-66 or PIO4 Preload (see side) Windows 987 Windows 987 SE Windows 987 SE Avail / withdrawn date June 1999 / February 2000 November 1999 / February 2000 February 2000 / February 2001 Display - size and type 10.4" TFT color (264.16mm) / Active Matrix Display - technology SVGA / 800x600 / 15ms refresh (typical) / 50 to 110 nits 16.7 million simultaneous colors / 250 to 1 contrast (typical) Graphics - controller NeoMagic MagicMedia128XD (NM2160C) / 128-bit accelerator / DDC2B / 2MB / SGRAM (embedded) / color space conversion Graphics - features Simultaneous LCD and CRT26 / 180 degree tilt / no multiple-monitor support / ext SVGA to 1024x768 with 65,536 colors Memory - std / max 64MB / 192MB33 -

AIX® Version 6.1 Performance Toolbox Guide Limiting Access to Data Suppliers

AIX Version 6.1 Performance Toolbox Version 3 Guide and Reference AIX Version 6.1 Performance Toolbox Version 3 Guide and Reference Note Before using this information and the product it supports, read the information in Appendix G, “Notices,” on page 431. This edition applies to AIX Version 6.1 and to all subsequent releases and modifications until otherwise indicated in new editions. (c) Copyright AT&T, 1984, 1985, 1986, 1987, 1988, 1989. All rights reserved. Copyright Sun Microsystems, Inc., 1985, 1986, 1987, 1988. All rights reserved. The Network File System (NFS) was developed by Sun Microsystems, Inc. This software and documentation is based in part on the Fourth Berkeley Software Distribution under license from The Regents of the University of California. We acknowledge the following institutions for their role in its development: the Electrical Engineering and Computer Sciences Department at the Berkeley Campus. The Rand MH Message Handling System was developed by the Rand Corporation and the University of California. Portions of the code and documentation described in this book were derived from code and documentation developed under the auspices of the Regents of the University of California and have been acquired and modified under the provisions that the following copyright notice and permission notice appear: Copyright Regents of the University of California, 1986, 1987, 1988, 1989. All rights reserved. Redistribution and use in source and binary forms are permitted provided that this notice is preserved and that due credit is given to the University of California at Berkeley. The name of the University may not be used to endorse or promote products derived from this software without specific prior written permission. -

The Power Manager

HW 24 - Little PowerBook in Slumberland Page: 1 NOTE: This Technical Note has been retired. Please see the Technical Notes page for current documentation. CONTENTS The purpose of this Note is to describe the ramifications of resting, sleeping, and The Power Manager power-saving modes in the PowerBook family of Macintosh computers, how they may References affect your application, and the appropriate Downloadables ways to defeat them, when appropriate. It also describes some nonintuitive ramifications of working with a battery-powered computer. [Oct 01 192] The Power Manager In each PowerBook is a separate processor called the Power Manager. Its function is to monitor and control the power consumption and battery charging of the system. In doing this, it turns on and off various hardware subsystems, changes or stops the CPU's clock speed, watches the battery voltage, and, when charging, sets the bulk charge or trickle charge modes of the battery charging circuit. As you can see, the power draw of the system is a dynamically changing value, depending on which subsystems are currently in use, the speed of the processor, and whether or not charger circuit power is available. The Power Manager is designed to optimize for the maximum battery life and controls the various operating modes in response to user preferences that allow the user to override or push back in time the onset of these modes. The Many Faces of the Power Manager The PowerBook 100 (just like the original portable) has four operating modes: normal, rest, sleep, and shutdown. The PowerBook 140 has four operating modes: normal, rest (power cycling), sleep, and shutdown. -

Ebook - Informations About Operating Systems Version: August 15, 2006 | Download

eBook - Informations about Operating Systems Version: August 15, 2006 | Download: www.operating-system.org AIX Internet: AIX AmigaOS Internet: AmigaOS AtheOS Internet: AtheOS BeIA Internet: BeIA BeOS Internet: BeOS BSDi Internet: BSDi CP/M Internet: CP/M Darwin Internet: Darwin EPOC Internet: EPOC FreeBSD Internet: FreeBSD HP-UX Internet: HP-UX Hurd Internet: Hurd Inferno Internet: Inferno IRIX Internet: IRIX JavaOS Internet: JavaOS LFS Internet: LFS Linspire Internet: Linspire Linux Internet: Linux MacOS Internet: MacOS Minix Internet: Minix MorphOS Internet: MorphOS MS-DOS Internet: MS-DOS MVS Internet: MVS NetBSD Internet: NetBSD NetWare Internet: NetWare Newdeal Internet: Newdeal NEXTSTEP Internet: NEXTSTEP OpenBSD Internet: OpenBSD OS/2 Internet: OS/2 Further operating systems Internet: Further operating systems PalmOS Internet: PalmOS Plan9 Internet: Plan9 QNX Internet: QNX RiscOS Internet: RiscOS Solaris Internet: Solaris SuSE Linux Internet: SuSE Linux Unicos Internet: Unicos Unix Internet: Unix Unixware Internet: Unixware Windows 2000 Internet: Windows 2000 Windows 3.11 Internet: Windows 3.11 Windows 95 Internet: Windows 95 Windows 98 Internet: Windows 98 Windows CE Internet: Windows CE Windows Family Internet: Windows Family Windows ME Internet: Windows ME Seite 1 von 138 eBook - Informations about Operating Systems Version: August 15, 2006 | Download: www.operating-system.org Windows NT 3.1 Internet: Windows NT 3.1 Windows NT 4.0 Internet: Windows NT 4.0 Windows Server 2003 Internet: Windows Server 2003 Windows Vista Internet: Windows Vista Windows XP Internet: Windows XP Apple - Company Internet: Apple - Company AT&T - Company Internet: AT&T - Company Be Inc. - Company Internet: Be Inc. - Company BSD Family Internet: BSD Family Cray Inc. -

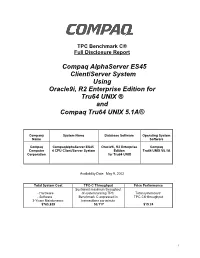

Compaq Alphaserver ES45 Client/Server System Using Oracle9i, R2 Enterprise Edition for Tru64 UNIX ® and Compaq Tru64 UNIX 5.1A®

TPC Benchmark C® Full Disclosure Report Compaq AlphaServer ES45 Client/Server System Using Oracle9i, R2 Enterprise Edition for Tru64 UNIX ® and Compaq Tru64 UNIX 5.1A® Company System Name Database Software Operating System Name Software Compaq CompaqAlphaServer ES45 Oracle9i, R2 Enterprise Compaq Computer 4 CPU Client/Server System Edition Tru64 UNIX V5.1A Corporation for Tru64 UNIX Availability Date: May 9, 2002 Total System Cost TPC-C Throughput Price Performance Sustained maximum throughput - Hardware of systemrunning TPC Total systemcost/ - Software Benchmark C expressed in TPC-C® throughput 3-Years Maintenance transactions per minute $763,829 50,117 $15.24 I First Printing - January 2002 Compaq Computer Corporation believes that the information in this document is accurate as of its publication date; such information is subject to change without notice. Compaq Computer Corporation is not responsible for any inadvertent errors. Compaq conducts its business in a manner that conserves the environment and protects the safety and health of its employees, customers, and the community. The performance information in this document is for guidance only. System performance is highly dependent on many factors, including systemhardware, systemand user software, and user application characteristics. Customerapplications must be carefully evaluated before estimating performance. Compaq Computer Corporation does not warrant or represent that a user can or will achieve similar performance expressed in transactions per minute (tpmC) or normalized price/performance ($/tpmC). No warranty on system performance or price/performance is expressed or implied in this document. Copyright © 2002 Compaq Computer Corporation All Rights Reserved. Printed in U.S.A. Permission is hereby granted to reproduce this document in whole or in part provided the copyright notice printed above is set forth in full text on the title page of each itemreproduced. -

4010, 237 8514, 226 80486, 280 82786, 227, 280 a AA. See Anti-Aliasing (AA) Abacus, 16 Accelerated Graphics Port (AGP), 219 Acce

Index 4010, 237 AIB. See Add-in board (AIB) 8514, 226 Air traffic control system, 303 80486, 280 Akeley, Kurt, 242 82786, 227, 280 Akkadian, 16 Algebra, 26 Alias Research, 169 Alienware, 186 A Alioscopy, 389 AA. See Anti-aliasing (AA) All-In-One computer, 352 Abacus, 16 All-points addressable (APA), 221 Accelerated Graphics Port (AGP), 219 Alpha channel, 328 AccelGraphics, 166, 273 Alpha Processor, 164 Accel-KKR, 170 ALT-256, 223 ACM. See Association for Computing Altair 680b, 181 Machinery (ACM) Alto, 158 Acorn, 156 AMD, 232, 257, 277, 410, 411 ACRTC. See Advanced CRT Controller AMD 2901 bit-slice, 318 (ACRTC) American national Standards Institute (ANSI), ACS, 158 239 Action Graphics, 164, 273 Anaglyph, 376 Acumos, 253 Anaglyph glasses, 385 A.D., 15 Analog computer, 140 Adage, 315 Anamorphic distortion, 377 Adage AGT-30, 317 Anatomic and Symbolic Mapper Engine Adams Associates, 102 (ASME), 110 Adams, Charles W., 81, 148 Anderson, Bob, 321 Add-in board (AIB), 217, 363 AN/FSQ-7, 302 Additive color, 328 Anisotropic filtering (AF), 65 Adobe, 280 ANSI. See American national Standards Adobe RGB, 328 Institute (ANSI) Advanced CRT Controller (ACRTC), 226 Anti-aliasing (AA), 63 Advanced Remote Display Station (ARDS), ANTIC graphics co-processor, 279 322 Antikythera device, 127 Advanced Visual Systems (AVS), 164 APA. See All-points addressable (APA) AED 512, 333 Apalatequi, 42 AF. See Anisotropic filtering (AF) Aperture grille, 326 AGP. See Accelerated Graphics Port (AGP) API. See Application program interface Ahiska, Yavuz, 260 standard (API) AI. -

A Survey of Distributed File Systems

A Survey of Distributed File Systems M. Satyanarayanan Department of Computer Science Carnegie Mellon University February 1989 Abstract Abstract This paper is a survey of the current state of the art in the design and implementation of distributed file systems. It consists of four major parts: an overview of background material, case studies of a number of contemporary file systems, identification of key design techniques, and an examination of current research issues. The systems surveyed are Sun NFS, Apollo Domain, Andrew, IBM AIX DS, AT&T RFS, and Sprite. The coverage of background material includes a taxonomy of file system issues, a brief history of distributed file systems, and a summary of empirical research on file properties. A comprehensive bibliography forms an important of the paper. Copyright (C) 1988,1989 M. Satyanarayanan The author was supported in the writing of this paper by the National Science Foundation (Contract No. CCR-8657907), Defense Advanced Research Projects Agency (Order No. 4976, Contract F33615-84-K-1520) and the IBM Corporation (Faculty Development Award). The views and conclusions in this document are those of the author and do not represent the official policies of the funding agencies or Carnegie Mellon University. 1 1. Introduction The sharing of data in distributed systems is already common and will become pervasive as these systems grow in scale and importance. Each user in a distributed system is potentially a creator as well as a consumer of data. A user may wish to make his actions contingent upon information from a remote site, or may wish to update remote information. -

The HP Garage—The Birthplace of Silicon Valley 367 Addison Avenue, Palo Alto, California

Brochure A home for innovation The HP Garage—the Birthplace of Silicon Valley 367 Addison Avenue, Palo Alto, California HP Corporate Archives Brochure A home for innovation Tucked away on a quiet, tree-lined residential street near Stanford University, the HP Garage stands today as the enduring symbol of innovation and the entrepreneurial spirit. It was in this humble 12x18-foot building that college friends Bill Hewlett and Dave Packard first pursued the dream of a company of their own. Guided by an unwavering desire to develop innovative and useful products, the two men went on to blaze a trail at the forefront of the electronics revolution. The history of the HP Garage The HP Garage in 1939 (top) and The garage stands behind a two-story Shingle restored in 2005 (bottom). Style home built for Dr. John C. Spencer about 1905. The exact construction date of the garage is unknown, but while there is no evidence of its presence on insurance maps dated 1908, by 1924 it is clearly denoted on updated documents as a private garage. In 1938, Bill Hewlett and Dave Packard decided to “make a run for it” in business. Dave left his job at General Electric in Schenectady, New York, and returned to Palo Alto while Bill scouted rentals. The garage was dedicated as the Birthplace of Silicon Valley in 1989, and HP acquired the He found one perfect for their needs on Addison property in 2000. HP is proud to have worked Avenue. Chosen specifically because of a garage closely with the City of Palo Alto to return the he and Dave could use as their workshop, the house, garage, and shed to conditions much property also offered a three-room, ground- as they were in 1939. -

Microprocessors in the 1970'S

Part II 1970's -- The Altair/Apple Era. 3/1 3/2 Part II 1970’s -- The Altair/Apple era Figure 3.1: A graphical history of personal computers in the 1970’s, the MITS Altair and Apple Computer era. Microprocessors in the 1970’s 3/3 Figure 3.2: Andrew S. Grove, Robert N. Noyce and Gordon E. Moore. Figure 3.3: Marcian E. “Ted” Hoff. Photographs are courtesy of Intel Corporation. 3/4 Part II 1970’s -- The Altair/Apple era Figure 3.4: The Intel MCS-4 (Micro Computer System 4) basic system. Figure 3.5: A photomicrograph of the Intel 4004 microprocessor. Photographs are courtesy of Intel Corporation. Chapter 3 Microprocessors in the 1970's The creation of the transistor in 1947 and the development of the integrated circuit in 1958/59, is the technology that formed the basis for the microprocessor. Initially the technology only enabled a restricted number of components on a single chip. However this changed significantly in the following years. The technology evolved from Small Scale Integration (SSI) in the early 1960's to Medium Scale Integration (MSI) with a few hundred components in the mid 1960's. By the late 1960's LSI (Large Scale Integration) chips with thousands of components had occurred. This rapid increase in the number of components in an integrated circuit led to what became known as Moore’s Law. The concept of this law was described by Gordon Moore in an article entitled “Cramming More Components Onto Integrated Circuits” in the April 1965 issue of Electronics magazine [338].