Opencore and Other Soft Core Processors up Cores Test Folder

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

L'universite BORDEAUX 1 DOCTEUR Ahmed BEN ATITALLAH

N° d’ordre 3409 THESE présentée à L’UNIVERSITE BORDEAUX 1 ECOLE DOCTORALE DES SCIENCES PHYSIQUES ET DE L’INGENIEUR POUR OBTENIR LE GRADE DE DOCTEUR SPECIALITE : ELECTRONIQUE Par Ahmed BEN ATITALLAH Etude et Implantation d’Algorithmes de Compression d’Images dans un Environnement Mixte Matériel et Logiciel Soutenue le : 11 Juillet 2007 Après avis de : M. Noureddine ELLOUZE Professeur à l’ENIT, Tunis, Tunisie Rapporteur M. Patrick GARDA Professeur à l’Université Paris VI Rapporteur Devant la Commission d’examen formée de : M. Lotfi KAMOUN Professeur à l’ENIS, Sfax, Tunisie Président M. Patrick GARDA Professeur à l’Université Paris VI Rapporteur M. Noureddine ELLOUZE Professeur à l’ENIT, Tunis, Tunisie Rapporteur M. Philippe MARCHEGAY Professeur à l’ENSEIRB M. Nouri MASMOUDI Professeur à l’ENIS, Sfax, Tunisie M. Patrice KADIONIK Maître de Conférences à l’ENSEIRB M. Patrice NOUEL Maître de Conférences à l’ENSEIRB -2007- A mes parents A ma famille A tous ceux qui me tiennent à cœur REMERCIEMENTS Cette thèse s’est effectuée en cotutelle entre l’équipe circuits et systèmes du Laboratoire d'Electronique et des Technologies de l'Information (LETI) de l’ENIS à Sfax, Tunisie ainsi que dans l’équipe Circuits Intégrés Numériques du Laboratoire de l’Intégration du Matériau au Système (IMS) de l’Université de Bordeaux et de l’ENSEIRB. Je remercie Monsieur le Professeur Nouri MASMOUDI ainsi que Monsieur le Professeur Philippe MARCHEGAY pour m’avoir accueilli au sein de leur équipe et pour l’intérêt qu’ils ont porté au déroulement de mes travaux. Je tiens à présenter ma vive gratitude à Monsieur Patrice KADIONIK, Maître de conférences à l’ENSEIRB, co-encadrant de ma thèse et Monsieur Patrice NOUEL, Maître de conférences à l’ENSEIRB, qui ont contribué activement à la réalisation de mes travaux, d’une part pour leurs conseils efficaces, leurs grandes compétences mais aussi pour leurs grandes qualités humaines. -

Debugging System for Openrisc 1000- Based Systems

Debugging System for OpenRisc 1000- based Systems Nathan Yawn [email protected] 05/12/09 Copyright (C) 2008 Nathan Yawn Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license should be included with this document. If not, the license may be obtained from www.gnu.org, or by writing to the Free Software Foundation. This document is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. History Rev Date Author Comments 1.0 20/7/2008 Nathan Yawn Initial version Contents 1.Introduction.............................................................................................................................................5 1.1.Overview.........................................................................................................................................5 1.2.Versions...........................................................................................................................................6 1.3.Stub-based methods.........................................................................................................................6 2.System Components................................................................................................................................7 -

Embedded Processors on FPGA: Hard-Core Vs Soft-Core Vivek J

Grand Valley State University ScholarWorks@GVSU Masters Theses Graduate Research and Creative Practice 5-19-2017 Embedded processors on FPGA: Hard-core vs Soft-core Vivek J. Vazhoth Kanhiroth Grand Valley State University Follow this and additional works at: http://scholarworks.gvsu.edu/theses Part of the Engineering Commons Recommended Citation Vazhoth Kanhiroth, Vivek J., "Embedded processors on FPGA: Hard-core vs Soft-core" (2017). Masters Theses. 845. http://scholarworks.gvsu.edu/theses/845 This Thesis is brought to you for free and open access by the Graduate Research and Creative Practice at ScholarWorks@GVSU. It has been accepted for inclusion in Masters Theses by an authorized administrator of ScholarWorks@GVSU. For more information, please contact [email protected]. Embedded processors on FPGA: Hard-core vs Soft-core Vivek Jayakrishnan Vazhoth Kanhiroth A Thesis submitted to the Graduate Faculty of GRAND VALLEY STATE UNIVERSITY In Partial Fulfilment of the Requirements For the Degree of Master of Science in Electrical Engineering Padnos College of Engineering and Computing April 2017 DEDICATION To my parents Jayakrishnan and Jayalakshmi who are my biggest inspiration and to my mentor Rajesh without whose help I would never have come out of my shell. 3 ACKNOWLEDGEMENTS I would like to thank my Thesis Advisor Dr. Chirag Parikh without whose patience, guidance and understanding I would not have finished this thesis. I would also like to thank my Thesis committee members Dr. Christian Trefftz and Dr. Azizur Rahman for their valuable inputs and feedback about my thesis. I am indebted to Dr. Shabbir Choudhuri for always being approachable and helping me on innumerable occasions over the last 3 years. -

A Superscalar Out-Of-Order X86 Soft Processor for FPGA

A Superscalar Out-of-Order x86 Soft Processor for FPGA Henry Wong University of Toronto, Intel [email protected] June 5, 2019 Stanford University EE380 1 Hi! ● CPU architect, Intel Hillsboro ● Ph.D., University of Toronto ● Today: x86 OoO processor for FPGA (Ph.D. work) – Motivation – High-level design and results – Microarchitecture details and some circuits 2 FPGA: Field-Programmable Gate Array ● Is a digital circuit (logic gates and wires) ● Is field-programmable (at power-on, not in the fab) ● Pre-fab everything you’ll ever need – 20x area, 20x delay cost – Circuit building blocks are somewhat bigger than logic gates 6-LUT6-LUT 6-LUT6-LUT 3 6-LUT 6-LUT FPGA: Field-Programmable Gate Array ● Is a digital circuit (logic gates and wires) ● Is field-programmable (at power-on, not in the fab) ● Pre-fab everything you’ll ever need – 20x area, 20x delay cost – Circuit building blocks are somewhat bigger than logic gates 6-LUT 6-LUT 6-LUT 6-LUT 4 6-LUT 6-LUT FPGA Soft Processors ● FPGA systems often have software components – Often running on a soft processor ● Need more performance? – Parallel code and hardware accelerators need effort – Less effort if soft processors got faster 5 FPGA Soft Processors ● FPGA systems often have software components – Often running on a soft processor ● Need more performance? – Parallel code and hardware accelerators need effort – Less effort if soft processors got faster 6 FPGA Soft Processors ● FPGA systems often have software components – Often running on a soft processor ● Need more performance? – Parallel -

Implementation, Verification and Validation of an Openrisc-1200

(IJACSA) International Journal of Advanced Computer Science and Applications, Vol. 10, No. 1, 2019 Implementation, Verification and Validation of an OpenRISC-1200 Soft-core Processor on FPGA Abdul Rafay Khatri Department of Electronic Engineering, QUEST, NawabShah, Pakistan Abstract—An embedded system is a dedicated computer system in which hardware and software are combined to per- form some specific tasks. Recent advancements in the Field Programmable Gate Array (FPGA) technology make it possible to implement the complete embedded system on a single FPGA chip. The fundamental component of an embedded system is a microprocessor. Soft-core processors are written in hardware description languages and functionally equivalent to an ordinary microprocessor. These soft-core processors are synthesized and implemented on the FPGA devices. In this paper, the OpenRISC 1200 processor is used, which is a 32-bit soft-core processor and Fig. 1. General block diagram of embedded systems. written in the Verilog HDL. Xilinx ISE tools perform synthesis, design implementation and configure/program the FPGA. For verification and debugging purpose, a software toolchain from (RISC) processor. This processor consists of all necessary GNU is configured and installed. The software is written in C components which are available in any other microproces- and Assembly languages. The communication between the host computer and FPGA board is carried out through the serial RS- sor. These components are connected through a bus called 232 port. Wishbone bus. In this work, the OR1200 processor is used to implement the system on a chip technology on a Virtex-5 Keywords—FPGA Design; HDLs; Hw-Sw Co-design; Open- FPGA board from Xilinx. -

Openpiton: an Open Source Manycore Research Framework

OpenPiton: An Open Source Manycore Research Framework Jonathan Balkind Michael McKeown Yaosheng Fu Tri Nguyen Yanqi Zhou Alexey Lavrov Mohammad Shahrad Adi Fuchs Samuel Payne ∗ Xiaohua Liang Matthew Matl David Wentzlaff Princeton University fjbalkind,mmckeown,yfu,trin,yanqiz,alavrov,mshahrad,[email protected], [email protected], fxiaohua,mmatl,[email protected] Abstract chipset Industry is building larger, more complex, manycore proces- sors on the back of strong institutional knowledge, but aca- demic projects face difficulties in replicating that scale. To Tile alleviate these difficulties and to develop and share knowl- edge, the community needs open architecture frameworks for simulation, synthesis, and software exploration which Chip support extensibility, scalability, and configurability, along- side an established base of verification tools and supported software. In this paper we present OpenPiton, an open source framework for building scalable architecture research proto- types from 1 core to 500 million cores. OpenPiton is the world’s first open source, general-purpose, multithreaded manycore processor and framework. OpenPiton leverages the industry hardened OpenSPARC T1 core with modifica- Figure 1: OpenPiton Architecture. Multiple manycore chips tions and builds upon it with a scratch-built, scalable uncore are connected together with chipset logic and networks to creating a flexible, modern manycore design. In addition, build large scalable manycore systems. OpenPiton’s cache OpenPiton provides synthesis and backend scripts for ASIC coherence protocol extends off chip. and FPGA to enable other researchers to bring their designs to implementation. OpenPiton provides a complete verifica- tion infrastructure of over 8000 tests, is supported by mature software tools, runs full-stack multiuser Debian Linux, and has been widespread across the industry with manycore pro- is written in industry standard Verilog. -

A Pythonic Approach for Rapid Hardware Prototyping and Instrumentation

A Pythonic Approach for Rapid Hardware Prototyping and Instrumentation John Clow, Georgios Tzimpragos, Deeksha Dangwal, Sammy Guo, Joseph McMahan and Timothy Sherwood University of California, Santa Barbara, CA, 93106 USA Email: fjclow, gtzimpragos, deeksha, sguo, jmcmahan, [email protected] Abstract—We introduce PyRTL, a Python embedded hardware To achieve these goals, PyRTL intentionally restricts users design language that helps concisely and precisely describe to a set of reasonable digital design practices. PyRTL’s small digital hardware structures. Rather than attempt to infer a and well-defined internal core structure makes it easy to add good design via HLS, PyRTL provides a wrapper over a well- defined “core” set of primitives in a way that empowers digital new functionality that works across every design, including hardware design teaching and research. The proposed system logic transforms, static analysis, and optimizations. Features takes advantage of the programming language features of Python such as elaboration-through-execution (e.g. introspection), de- to allow interesting design patterns to be expressed succinctly, and sign and simulation without leaving Python, and the option encourage the rapid generation of tooling and transforms over to export to, or import from, common HDLs (Verilog-in via a custom intermediate representation. We describe PyRTL as a language, its core semantics, the transform generation interface, Yosys [1] and BLIF-in, Verilog-out) are also supported. More and explore its application to several different design patterns and information about PyRTL’s high level flow can be found in analysis tools. Also, we demonstrate the integration of PyRTL- Figure 1. generated hardware overlays into Xilinx PYNQ platform. -

Implementation of PS2 Keyboard Controller IP Core for on Chip Embedded System Applications

The International Journal Of Engineering And Science (IJES) ||Volume||2 ||Issue|| 4 ||Pages|| 48-50||2013|| ISSN(e): 2319 – 1813 ISSN(p): 2319 – 1805 Implementation of PS2 Keyboard Controller IP Core for On Chip Embedded System Applications 1, 2, Medempudi Poornima, Kavuri Vijaya Chandra 1,M.Tech Student 2,Associate Proffesor. 1,2,Prakasam Engineering College,Kandukuru(post), Kandukuru(m.d), Prakasam(d.t). -----------------------------------------------------------Abstract----------------------------------------------------- In many case on chip systems are used to reduce the development cycles. Mostly IP (Intellectual property) cores are used for system development. In this paper, the IP core is designed with ALTERA NIOSII soft-core processors as the core and Cyclone III FPGA series as the digital platform, the SOPC technology is used to make the I/O interface controller soft-core such as microprocessors and PS2 keyboard on a chip of FPGA. NIOSII IDE is used to accomplish the software testing of system and the hardware test is completed by ALTERA Cyclone III EP3C16F484C6 FPGA chip experimental platform. The result shows that the functions of this IP core are correct, furthermore it can be reused conveniently in the SOPC system. ---------------------------------------------------------------------------------------------------------------------------------------- Date of Submission: 8 April 2013 Date Of Publication: 25, April.2013 --------------------------------------------------------------------------------------------------------------------------------------- -

Application-Specific Customization of Soft Processor Microarchitecture

Application-Specific Customization of Soft Processor Microarchitecture Peter Yiannacouras, J. Gregory Steffan, and Jonathan Rose The Edward S. Rogers Sr. Department of Electrical and Computer Engineering University of Toronto {yiannac,steffan,jayar}@eecg.utoronto.ca ABSTRACT processors on their FPGA die, there has been significant up- A key advantage of soft processors (processors built on an take [15,16] of soft processors [3,4] which are constructed in FPGA programmable fabric) over hard processors is that the programmable fabric itself. While soft processors can- they can be customized to suit an application program’s not match the performance, area, or power consumption of specific software. This notion has been exploited in the past a hard processor, their key advantage is the flexibility they principally through the use of application-specific instruc- present in allowing different numbers of processors and spe- tions. While commercial soft processors are now widely de- cialization to the application through special instructions. ployed, they are available in only a few microarchitectural Specialization can also occur by selecting a different micro- variations. In this work we explore the advantage of tuning architecture for a specific application, and that is the focus the processor’s microarchitecture to specific software appli- of this paper. We suggest that this kind of specialization cations, and show that there are significant advantages in can be applied in two different contexts: doing so. 1. When an embedded processor is principally -

Latticemico8 Soft Core 8-Bit Microcontroller Optimized for Lattice Programmable Devices

O P E N S O U R C E S O F T C O R E M I C R O C ont R O LL E R LatticeMico8 Soft Core 8-Bit Microcontroller Optimized for Lattice Programmable Devices The LatticeMico8™ is an 8-bit “soft” microcontroller core for the LatticeECP™, LatticeEC™ and LatticeXP™ families of Field Programmable Gate Arrays (FPGAs), as well as the MachXO™ family of Crossover Programmable Logic Devices. Combining a full 18-bit wide instruction set with 32 general purpose registers, the LatticeMico8 is a flexible reference design suitable for a wide variety of markets, including com- munications, consumer, computer, medical, industrial, and automotive. The core consumes minimal device resources, less than 200 Look Up Tables (LUTs) in the smallest configu- ration, while maintaining a broad feature set. In order to encourage user experimentation, development and contributions, Lattice is providing a new open intellec- tual property (IP) core license, the first such license offered Key Features and Benefits by any FPGA supplier. The license applies many of the concepts of the successful open source movement to IP cores Optimized for LatticeECP, LatticeEC, LatticeXP, and MachXO Families targeted for programmable logic applications. Efficient Architecture – Utilizes <200 LUTs Broad Feature Set LatticeMico8 Block Diagram • 8-bit data path • 18-bit wide instructions • 32 general purpose registers 16 Deep Call Stack • 32 bytes of internal scratch pad memory Program Interrupt Ack • Input/Output is performed using ports (up to 256 port Address Program Flow Control & PC -

Day 2, 1640: Leveraging Opensparc

Leveraging OpenSPARC ESA Round Table 2006 on Next Generation Microprocessors for Space Applications G.Furano, L.Messina – TEC-EDD OpenSPARC T1 • The T1 is a new-from-the-ground-up SPARC microprocessor implementation that conforms to the UltraSPARC architecture 2005 specification and executes the full SPARC V9 instruction set. Sun has produced two previous multicore processors: UltraSPARC IV and UltraSPARC IV+, but UltraSPARC T1 is its first microprocessor that is both multicore and multithreaded. • The processor is available with 4, 6 or 8 CPU cores, each core able to handle four threads. Thus the processor is capable of processing up to 32 threads concurrently. • Designed to lower the energy consumption of server computers, the 8-cores CPU uses typically 72 W of power at 1.2 GHz. G.Furano, L.Messina – TEC-EDD 72W … 1.2 GHz … 90nm … • Is a cutting edge design, targeted for high-end servers. • NOT FOR SPACE USE • But, let’s see which are the potential spin-in … G.Furano, L.Messina – TEC-EDD Why OPEN ? On March 21, 2006, Sun made the UltraSPARC T1 processor design available under the GNU General Public License. The published information includes: • Verilog source code of the UltraSPARC T1 design, including verification suite and simulation models • ISA specification (UltraSPARC Architecture 2005) • The Solaris 10 OS simulation images • Diagnostics tests for OpenSPARC T1 • Scripts, open source and Sun internal tools needed to simulate the design and to do synthesis of the design • Scripts and documentation to help with FPGA implementation -

Up Cores T Est Folder Opencores Name Status Author Style / Clone

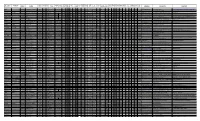

_uP_cores_t opencores style / data inst repor com LUTs blk F tool MIPS clks/ KIPS src # src tool fltg Ha max max byte # # pipe start last status author FPGA top file doc reference note worthy comments date LUT? est folder name clone size size ter ment ALUT mults ram max ver /clk inst /LUT code files chain pt vd data inst adrs inst reg len year revis cray1 alpha Christopher Fenton cray1 64 16 kintex-7-3 James Brakefield13463 6 19 10 127 ## 14.7 6.00 1.0 56.6 verilog 46 cray_sys_topyes yes Y N 4M 4M N 512 2010 CRAY data sheets homebrew Cray1 www.chrisfenton.com/homebrew-cray-1a/ fpgammix stable Tommy Thorn MMIX 64 32 arria-2 James Brakefield11605 A 8 10 94 ## q13.1 1.50 4.0 3.0 system verilog2 core yes yes Y Y 4G 4G Y 256 288 2006 2008 clone of Knuth's MMIX micro-coded s1_core S1 Core stable Fabrizio Fazzino etal SPARC 64 32 kintex-7-3 James Brakefield52845 6 8 59 56 ## v14.1 2.00 1.0 2.1 verilog 136 s1_top yes yes Y N 4G 4G Y 32 2007 2012 SPARC data sheets reduced version of OpenSPARC T1 Vivado run microblaze proprietaryXilinx uBlaze 32 32 kintex-7 Xilinx 546 6 1 320 1.03 1.0 603.7 not avail yes yes opt 4G 4G Y 86 32 3 2002 www.xilinx.com/tools/microblaze.htmMicroBlaze MCS, smallest configuration70 configuration options, MMU optional ARM_Cortex_A9 ASIC ARM ARM a9 32 16 arria V altera 4500 A 1050 2.50 1.0 583.3 asic yes yes Y 4G 4G Y 80 16 10 2012 altera data sheets uses pro-rated LC area dual issue, includes fltg-pt & MMU & caches nios2 proprietaryAltera Nios II 32 32 stratix-5 Altera 895 A 310 1.13 1.0 389.7 not avail yes yes opt 4G 4G