Use Video Standards for Eye-Opening Data Transmission: Mega-Bits @ Many

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Iagrams TH EW)

iagrams TH EW) TP07 TP10 TP08 TP09 TP09 TP01 TP06 TP10 TP08 TP05 TP07 TP03 TP02 TP04 : Power Lin : Signal Lin TP12 TP13 TP15 TP11 TP14 TP22 TP23 TP23 TP22 TP24 TP16 TP18 TP17 TP25 TP21 TP19 TP24 TP20 TP25 TP32 TP33 TP35 TP26 TP33 TP34 TP34 TP27 TP32 TP35 TP31 TP28 TP29 TP30 : Power Line : Signal Line -EW) H Alignment and Adjustments 4-4 FOCUS Adjustment 1. Input a black and white signal. 2. Adjust the tuning control for the clearest picture. 3. Adjust the FOCUS control for well defined scanning lines in the center area of the screen. 4-5 SCREEN Adjustment 1. Input Toshiba Pattern 2. Enter “Service Mode”.(Refer to “4-8-1 Service Mode”) 3. Select “G2-Adjust”. 4. Set the values as below. Table 1. Screen Adjustment Table COLR G B No INCH / CRT REGION IBRM WDRV CDL (Smallest Value) 1 14” / SDI 205 35 100 100 Noraml 220 35 180 100 2 15PF / SDI 215 35 100 100 CIS 3 21” 1.7R / SDI 220 35 180 100 4 21” 1.7R / JCT 220 35 200 150 5 21PF / TSB 220 35 180 65 Noraml 6 21PF / LG 230 35 230 65 7 21PF / SDI 220 35 210 65 8 25PF / SDI 210 35 160 120 9 29” 1.3R / SDI 200 35 170 150 5. Turn the SCREEN VR until “MRCR G B” and “MRWDG” are green and those value are about 100. (The incorrect SCREEN Voltage may result that “MRCR G B” and “MRWDG” should be red) 4-2 Samsung Electronics Alignment and Adjustments 4-6 E2PROM (IC902) Replacement 1. -

ABBREVIATIONS EBU Technical Review

ABBREVIATIONS EBU Technical Review AbbreviationsLast updated: January 2012 720i 720 lines, interlaced scan ACATS Advisory Committee on Advanced Television 720p/50 High-definition progressively-scanned TV format Systems (USA) of 1280 x 720 pixels at 50 frames per second ACELP (MPEG-4) A Code-Excited Linear Prediction 1080i/25 High-definition interlaced TV format of ACK ACKnowledgement 1920 x 1080 pixels at 25 frames per second, i.e. ACLR Adjacent Channel Leakage Ratio 50 fields (half frames) every second ACM Adaptive Coding and Modulation 1080p/25 High-definition progressively-scanned TV format ACS Adjacent Channel Selectivity of 1920 x 1080 pixels at 25 frames per second ACT Association of Commercial Television in 1080p/50 High-definition progressively-scanned TV format Europe of 1920 x 1080 pixels at 50 frames per second http://www.acte.be 1080p/60 High-definition progressively-scanned TV format ACTS Advanced Communications Technologies and of 1920 x 1080 pixels at 60 frames per second Services AD Analogue-to-Digital AD Anno Domini (after the birth of Jesus of Nazareth) 21CN BT’s 21st Century Network AD Approved Document 2k COFDM transmission mode with around 2000 AD Audio Description carriers ADC Analogue-to-Digital Converter 3DTV 3-Dimension Television ADIP ADress In Pre-groove 3G 3rd Generation mobile communications ADM (ATM) Add/Drop Multiplexer 4G 4th Generation mobile communications ADPCM Adaptive Differential Pulse Code Modulation 3GPP 3rd Generation Partnership Project ADR Automatic Dialogue Replacement 3GPP2 3rd Generation Partnership -

Creating 4K/UHD Content Poster

Creating 4K/UHD Content Colorimetry Image Format / SMPTE Standards Figure A2. Using a Table B1: SMPTE Standards The television color specification is based on standards defined by the CIE (Commission 100% color bar signal Square Division separates the image into quad links for distribution. to show conversion Internationale de L’Éclairage) in 1931. The CIE specified an idealized set of primary XYZ SMPTE Standards of RGB levels from UHDTV 1: 3840x2160 (4x1920x1080) tristimulus values. This set is a group of all-positive values converted from R’G’B’ where 700 mv (100%) to ST 125 SDTV Component Video Signal Coding for 4:4:4 and 4:2:2 for 13.5 MHz and 18 MHz Systems 0mv (0%) for each ST 240 Television – 1125-Line High-Definition Production Systems – Signal Parameters Y is proportional to the luminance of the additive mix. This specification is used as the color component with a color bar split ST 259 Television – SDTV Digital Signal/Data – Serial Digital Interface basis for color within 4K/UHDTV1 that supports both ITU-R BT.709 and BT2020. 2020 field BT.2020 and ST 272 Television – Formatting AES/EBU Audio and Auxiliary Data into Digital Video Ancillary Data Space BT.709 test signal. ST 274 Television – 1920 x 1080 Image Sample Structure, Digital Representation and Digital Timing Reference Sequences for The WFM8300 was Table A1: Illuminant (Ill.) Value Multiple Picture Rates 709 configured for Source X / Y BT.709 colorimetry ST 296 1280 x 720 Progressive Image 4:2:2 and 4:4:4 Sample Structure – Analog & Digital Representation & Analog Interface as shown in the video ST 299-0/1/2 24-Bit Digital Audio Format for SMPTE Bit-Serial Interfaces at 1.5 Gb/s and 3 Gb/s – Document Suite Illuminant A: Tungsten Filament Lamp, 2854°K x = 0.4476 y = 0.4075 session display. -

PROFESSIONAL VIDEO 315 800-947-1175 | 212-444-6675 Blackmagic • Canon

PROFESSIONAL VIDEO 315 800-947-1175 | 212-444-6675 Blackmagic • Canon VIDEO TAPE Fuji Film PRO-T120 VHS Video Cassette (FUPROT120)............................3.29 XA10 Professional HD Camcorder DVC-60 Mini DV Cassette (FUDVC60) .......................................3.35 Pocket Cinema Camera Ultra-compact, the XA10 DVC-80 Mini DV Cassette (FUDVC80)........................................7.99 shares nearly all the Pocket Cinema Camera is a HDV Cassette, 63 Minute (FUHDVDVM63) .................................6.99 functionality of the XF100, true Super 16 digital film DV141HD63S HDV (FUDV14163S) ............................................7.95 but in an even smaller, camera that’s small enough run-and-gun form factor. to keep with you at all times. Maxell 64GB internal flash drive Remarkably compact (5 x 2.6 DV-60 Mini DV Cassette (MADVM60SE) .................................3.99 and two SDXC-compatible x 1.5”) and lightweight (12.5 M-DV63PRO Mini DV Cassette (MADVM63PRO)......................5.50 card slots allow non-stop oz) with a magnesium alloy chassis, it features 13 stops of T-120 VHS Cassette (MAGXT120) ..........................................2.39 recording. Able to capture dynamic range, Super 16 sensor size, and and records 1080HD STD-160 VHS Cassette (MAGXT160).....................................2.69 AVCHD video at bitrates up to lossless CinemaDNG RAW and Apple ProRes 422 (HQ) files to fast STD-180 VHS Cassette (MAGXT180)......................................3.09 24Mbps, the camcorder’s native 1920 x1080 CMOS sensor also SDXC cards, so you can immediately edit or color correct your HG-T120 VHS Cassette (MAHGT120) .....................................1.99 lets you choose 60i, 24p, PF30, and PF24 frame rates for media on your laptop. Active Micro Four Thirds lens mount can HG-T160 VHS Video Cassette (MAHGT160) ............................2.59 customizing the look of your footage. -

AXI Reference Guide

AXI Reference Guide [Guide Subtitle] [optional] UG761 (v13.4) January 18, 2012 [optional] Xilinx is providing this product documentation, hereinafter “Information,” to you “AS IS” with no warranty of any kind, express or implied. Xilinx makes no representation that the Information, or any particular implementation thereof, is free from any claims of infringement. You are responsible for obtaining any rights you may require for any implementation based on the Information. All specifications are subject to change without notice. XILINX EXPRESSLY DISCLAIMS ANY WARRANTY WHATSOEVER WITH RESPECT TO THE ADEQUACY OF THE INFORMATION OR ANY IMPLEMENTATION BASED THEREON, INCLUDING BUT NOT LIMITED TO ANY WARRANTIES OR REPRESENTATIONS THAT THIS IMPLEMENTATION IS FREE FROM CLAIMS OF INFRINGEMENT AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Except as stated herein, none of the Information may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. © Copyright 2012 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, Kintex, Artix, ISE, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners. ARM® and AMBA® are registered trademarks of ARM in the EU and other countries. All other trademarks are the property of their respective owners. Revision History The following table shows the revision history for this document: . Date Version Description of Revisions 03/01/2011 13.1 Second Xilinx release. -

HD-SDI, HDMI, and Tempus Fugit

TECHNICALL Y SPEAKING... By Steve Somers, Vice President of Engineering HD-SDI, HDMI, and Tempus Fugit D-SDI (high definition serial digital interface) and HDMI (high definition multimedia interface) Hversion 1.3 are receiving considerable attention these days. “These days” really moved ahead rapidly now that I recall writing in this column on HD-SDI just one year ago. And, exactly two years ago the topic was DVI and HDMI. To be predictably trite, it seems like just yesterday. As with all things digital, there is much change and much to talk about. HD-SDI Redux difference channels suffice with one-half 372M spreads out the image information The HD-SDI is the 1.5 Gbps backbone the sample rate at 37.125 MHz, the ‘2s’ between the two channels to distribute of uncompressed high definition video in 4:2:2. This format is sufficient for high the data payload. Odd-numbered lines conveyance within the professional HD definition television. But, its robustness map to link A and even-numbered lines production environment. It’s been around and simplicity is pressing it into the higher map to link B. Table 1 indicates the since about 1996 and is quite literally the bandwidth demands of digital cinema and organization of 4:2:2, 4:4:4, and 4:4:4:4 savior of high definition interfacing and other uses like 12-bit, 4096 level signal data with respect to the available frame delivery at modest cost over medium-haul formats, refresh rates above 30 frames per rates. distances using RG-6 style video coax. -

Glossary of Digital Video Terms

Glossary of Digital Video Terms 24P: 24 frame per second, progressive scan. This has been the frame rate of motion picture film since talkies arrived. It is also one of the rates allowed for transmission in the DVB and ATSC television standards – so they can handle film without needing any frame-rate change (3:2 pull-down for 60 fields-per-second systems or running film at 25fps for 50 Hz systems). It is now accepted as a part of television production formats – usually associated with high definition 1080 lines, progressive scan. A major attraction is a relatively easy path from this to all major television formats as well as offering direct electronic support for motion picture film and D-cinema. 24Psf: 24 frame per second, progressive segmented frame. A 24P system in which each frame is segmented – recorded as odd lines followed by even lines. Unlike normal television, the odd and even lines are from the same snapshot in time – exactly as film is shown today on 625/50 TV systems. This way the signal is more compatible (than normal progressive) for use with video systems, e.g. VTRs, SDTI or HD-SDI connections, mixers/switchers etc., which may also handle interlaced scans. It can also easily be viewed without the need to process the pictures to reduce 24-frame flicker. 3:2 pull-down: Method used to map the 24 fps of film onto the 30 fps (60 fields) of 525-line TV, so that one film frame occupies three TV fields, the next two, etc. It means the two fields of every other TV frame come from different film frames making operations such as rotoscoping impossible, and requiring care in editing. -

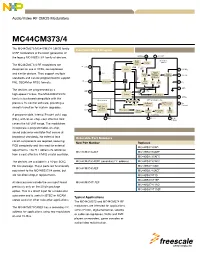

MC44CM373/4 Audio/Video RF CMOS Fact Sheet

Audio/Video RF CMOS Modulators MC44CM373/4 The MC44CM373/MC44CM374 CMOS family of RF modulators is the latest generation of the legacy MC44BS373/4 family of devices. The MC44CM373/4 RF modulators are designed for use in VCRs, set-top boxes and similar devices. They support multiple standards and can be programmed to support PAL, SECAM or NTSC formats. The devices are programmed by a high-speed I2C bus. The MC44CM373/374 family is backward compatible with the previous I2C control software, providing a smooth transition for system upgrades. A programmable, internal Phase-Lock Loop (PLL), with an on-chip, cost-effective tank covers the full UHF range. The modulators incorporate a programmable, on-chip, sound subcarrier oscillator that covers all broadcast standards. No external tank Orderable Part Numbers circuit components are required, reducing New Part Number Replaces PCB complexity and the need for external MC44BS373CAD adjustments. The PLL obtains its reference MC44CM373CAEF MC44BS373CAEF from a cost-effective 4 MHz crystal oscillator. MC44BS373CAFC The devices are available in a 16-pin SOIC, MC44CM373CASEF (secondary I2C address) MC44BS373CAFC Pb-free package. These parts are functionally MC44BS374CAD MC44CM374CAEF equivalent to the MC44BS373/4 series, but MC44BS374CAEF are not direct drop-in replacements. MC44BS374T1D MC44BS374T1EF All devices now include the aux input found MC44CM374T1AEF MC44BS374T1AD previously only on the 20-pin package MC44BS374T1AEF option. This is a direct input for a modulated subcarrier and is useful in BTSC or NICAM Typical Applications stereo sound or other subcarrier applications. The MC44CM373 and MC44CM374 RF modulators are intended for applications The MC44CM373CASEF has a secondary I2C within IP/DSL, digital terrestrial, satellite address for applications using two modulators or cable set-top boxes, VCRs and DVD on one I2C Bus. -

High Definition Analog Component Measurements

Application Note High Definition Analog Component Measurements Requirements for Measuring Analog Component HD Signals for Video Devices The transition to digital has enabled great strides in the of these devices. When an image is captured by a color processing of video signals, allowing a variety of camera and converted from light to an electrical signal, techniques to be applied to the video image. Despite the signal is comprised of three components - Red, these benefits, the final signal received by the customer Green and Blue (RGB). From the combination of these is still converted to an analog signal for display on a three signals, a representation of the original image can be picture monitor. With the proliferation of a wide variety conveyed to a color display. The various video processing of digital devices - set-top boxes, Digital Versatile Disk systems within the signal paths need to process the (DVD) players and PC cards - comes a wide range of three components identically, in order not to introduce video formats in addition to the standard composite any amplitude or channel timing errors. Each of the three output. It is therefore necessary to understand the components R’G’B’ (the ( ’ ) indicates that the signal requirements for measuring analog component High has been gamma corrected) has identical bandwidth, Definition (HD) signals in order to test the performance which increases complexity within the digital domain. High Definition Analog Component Measurements Application Note Y’, R’-Y’, B’-Y’, Commonly Used for Analog Component Analog Video Format 1125/60/2:1 750/60/1:1 525/59.94/1:1, 625/50/1:1 Y’ 0.2126 R’ + 0.7152 G’ + 0.0722 B’ 0.299 R’ + 0.587 G’ + 0.114 B’ R’-Y’ 0.7874 R’ - 0.7152 G’ - 0.0722 B’ 0.701 R’ - 0.587 G’ - 0.114 B’ B’-Y’ - 0.2126 R’ - 0.7152 G’ + 0.9278 B’ - 0.299 R’ - 0.587 G’ + 0.886 B’ Table 1. -

Understanding HD and 3G-SDI Video Poster

Understanding HD & 3G-SDI Video EYE DIGITAL SIGNAL TIMING EYE DIAGRAM The eye diagram is constructed by overlaying portions of the sampled data stream until enough data amplitude is important because of its relation to noise, and because the Y', R'-Y', B'-Y', COMMONLY USED FOR ANALOG COMPONENT ANALOG VIDEO transitions produce the familiar display. A unit interval (UI) is defined as the time between two adjacent signal receiver estimates the required high-frequency compensation (equalization) based on the Format 1125/60/2:1 750/60/1:1 525/59.94/2:1, 625/50/2:1, 1250/50/2:1 transitions, which is the reciprocal of clock frequency. UI is 3.7 ns for digital component 525 / 625 (SMPTE remaining half-clock-frequency energy as the signal arrives. Incorrect amplitude at the Y’ 0.2126 R' + 0.7152 G' + 0.0722 B' 0.299 R' + 0.587 G' + 0.114 B' 259M), 673.4 ps for digital high-definition (SMPTE 292) and 336.7ps for 3G-SDI serial digital (SMPTE 424M) sending end could result in an incorrect equalization applied at the receiving end, thus causing Digital video synchronization is provided by End of Active Video (EAV) and Start of Active Video (SAV) sequences which start with a R'-Y' 0.7874 R' - 0.7152 G' - 0.0722 B' 0.701 R' - 0.587 G' - 0.114 B' as shown in Table 1. A serial receiver determines if the signal is “high” or “low” in the center of each eye, and signal distortions. Overshoot of the rising and falling edge should not exceed 10% of the waveform HORIZONTAL LINE TIMING unique three word pattern: 3FFh (all bits in the word set to 1), 000h (all 0’s), 000h (all 0’s), followed by a fourth “XYZ” word whose B'-Y' -0.2126 R' - 0.7152 G' + 0.9278 B' -0.299 R' - 0.587 G' + 0.886 B' detects the serial data. -

VPC 3205C, VPC 3215C Video Processor Family

PRELIMINARY DATA SHEET MICRONAS VPC 3205C, VPC 3215C Video Processor Family Edition Oct. 19, 1998 6251-457-2PD MICRONAS VPC 3205C, VPC 3215C PRELIMINARY DATA SHEET Contents Page Section Title 4 1. Introduction 4 1.1. System Architecture 4 1.2. Video Processor Family 5 1.3. VPC Applications 6 2. Functional Description 6 2.1. Analog Front-End 6 2.1.1. Input Selector 6 2.1.2. Clamping 6 2.1.3. Automatic Gain Control 6 2.1.4. Analog-to-Digital Converters 6 2.1.5. Digitally Controlled Clock Oscillator 6 2.1.6. Analog Video Output 7 2.2. Adaptive Comb Filter 7 2.3. Color Decoder 8 2.3.1. IF-Compensation 8 2.3.2. Demodulator 8 2.3.3. Chrominance Filter 9 2.3.4. Frequency Demodulator 9 2.3.5. Burst Detection 9 2.3.6. Color Killer Operation 9 2.3.7. PAL Compensation/1-H Comb Filter 10 2.3.8. Luminance Notch Filter 10 2.3.9. Skew Filtering 11 2.4. Horizontal Scaler 11 2.5. Blackline Detector 11 2.6. Control and Data Output Signals 11 2.6.1. Line-Locked Clock Generation 12 2.6.2. Sync Signals 12 2.6.3. DIGIT3000 Output Format 12 2.6.4. Line-Locked 4:2:2 Output Format 12 2.6.5. Line-Locked 4:1:1 Output Format 12 2.6.6. Output Code Levels 12 2.6.7. Output Signal Levels 12 2.6.8. Test Pattern Generator 13 2.6.9. Priority Bus Codec 13 2.7. -

Multi-Rate Serial Digital Interface (SDI) Physical Layer IP Core Is an Ipexpress User-Configurable Core and Can Be Used to Generate Any Allowable Configuration

ispLever TM CORECORE Multi-Rate Serial Digital Interface Physical Layer IP Core User’s Guide January 2012 ipug70_01.2 Multi-Rate Serial Data Interface Physical Layer Lattice Semiconductor IP Core User’s Guide Introduction Serial Digital Interface (SDI) is the most popular raw video link standard used in television broadcast studios and video production facilities. Field Programmable Gate Arrays (FPGAs) with SDI interface capability can be used for acquisition, mixing, storage, editing, processing and format conversion applications. Simpler applications use FPGAs to acquire SDI data from one or more standard definition (SD) or high definition (HD) sources, perform sim- ple processing and retransmit the video data in SDI format. Such applications require an SDI physical layer (PHY) interface and some basic processing blocks such as a color space converter and frame buffer. In more complex applications, the acquired video receives additional processing, such as video format conversion, filtering, scaling, graphics mixing and picture-in-picture display. FPGA devices can also be used as a bridge between SDI video sources and backplane protocols such as PCI Express or Ethernet, with or without any additional video processing. In an FPGA-based SDI solution, the physical interface portion is often the most challenging part of the solution. This is because the PHY layer includes several device-dependent components such as high speed I/Os (inputs/outputs), serializer/deserializer (SERDES), clock/data recovery, word alignment and timing signal detection logic. Video processing, on the other hand, is algorithmic and is usually achieved using proprietary algorithms developed by in-house teams. The Lattice Multi-Rate SDI PHY Intellectual Property (IP) Core is a complete SDI PHY interface that connects to the high-speed SDI serial data on one side and the formatted parallel data on the other side.