Understanding HD and 3G-SDI Video Poster

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

881/882 Video Test Instrument User Guide

881/882 Video Test Instrument User Guide 881/882 Video Test Instrument, User Guide, Revision A.35 (9/23/10) Copyright 2010 Quantum Data. All rights reserved. The information in this document is provided for use by our customers and may not be incorporated into other products or publications without the expressed written consent of Quantum Data. Quantum Data reserves the right to make changes to its products to improve performance, reliability, producibility, and (or) marketability. Information furnished by Quantum Data is believed to be accurate and reliable. However, no responsibility is assumed by Quantum Data for its use. Updates to this manual are available at http://www.quantumdata.com/support/downloads/ . Table of Contents Chapter 1 Getting Started Introduction . 2 882D features . 2 Video interfaces . 4 Computer interfaces . 7 Front panel interface . 9 Status indicators . 9 Menu selection keys . 10 882 file system and media . 13 882 file system . 13 882 media . 13 882 operational modes . 14 Booting up the 882 . 14 Basic mode. 15 Browse mode . 15 Web interface . 20 Working with the Virtual Front Panel . 20 Working with the CMD (Command) Terminal. 22 Working with the 882 FTP Browser . 23 Copying files between 882s . 27 Command line interface . 30 Working with the serial interface. 30 Working with the network interface. 33 Sending commands interactively . 34 Sending command files (serial interface only) . 34 Working with user profiles . 36 Chapter 2 Testing Video Displays General video display testing procedures . 40 882 Video Test Instrument User Guide (Rev A.35) i Making physical connection . 40 Selecting interface type . 41 Selecting video format . -

VC-1 Compressed Video Bitstream Format and Decoding Process

_________________________________________________________________ SMPTE 421M-2006 SMPTE STANDARD VC-1 Compressed Video Bitstream Format and Decoding Process _________________________________________________________________ Intellectual property notice Copyright 2003-2006 THE SOCIETY OF MOTION PICTURE AND TELEVISION ENGINEERS 3 Barker Ave. White Plains, NY 10601 +1 914 761 1100 Fax +1 914 761-3115 E-mail [email protected] Web http://www.smpte.org The user’s attention is called to the possibility that compliance with this document may require use of inventions covered by patent rights. By publication of this document, no position is taken with respect to the validity of these claims or of any patent rights in connection therewith. The patent holders have, however, filed statements of willingness to grant a license under these rights on fair, reasonable and nondiscriminatory terms and conditions to applicants desiring to obtain such a license. Contact information may be obtained from the SMPTE. No representation or warranty is made or implied that these are the only licenses that may be required to avoid infringement in the use of this document. © SMPTE 2003-2006 – All rights reserved Approved 24-February-2006 i Foreword SMPTE (the Society of Motion Picture and Television Engineers) is an internationally-recognized standards developing organization. Headquartered and incorporated in the United States of America, SMPTE has members in over 80 countries on six continents. SMPTE’s Engineering Documents, including Standards, Recommended Practices and Engineering Guidelines, are prepared by SMPTE’s Technology Committees. Participation in these Committees is open to all with a bona fide interest in their work. SMPTE cooperates closely with other standards-developing organizations, including ISO, IEC and ITU. -

Iagrams TH EW)

iagrams TH EW) TP07 TP10 TP08 TP09 TP09 TP01 TP06 TP10 TP08 TP05 TP07 TP03 TP02 TP04 : Power Lin : Signal Lin TP12 TP13 TP15 TP11 TP14 TP22 TP23 TP23 TP22 TP24 TP16 TP18 TP17 TP25 TP21 TP19 TP24 TP20 TP25 TP32 TP33 TP35 TP26 TP33 TP34 TP34 TP27 TP32 TP35 TP31 TP28 TP29 TP30 : Power Line : Signal Line -EW) H Alignment and Adjustments 4-4 FOCUS Adjustment 1. Input a black and white signal. 2. Adjust the tuning control for the clearest picture. 3. Adjust the FOCUS control for well defined scanning lines in the center area of the screen. 4-5 SCREEN Adjustment 1. Input Toshiba Pattern 2. Enter “Service Mode”.(Refer to “4-8-1 Service Mode”) 3. Select “G2-Adjust”. 4. Set the values as below. Table 1. Screen Adjustment Table COLR G B No INCH / CRT REGION IBRM WDRV CDL (Smallest Value) 1 14” / SDI 205 35 100 100 Noraml 220 35 180 100 2 15PF / SDI 215 35 100 100 CIS 3 21” 1.7R / SDI 220 35 180 100 4 21” 1.7R / JCT 220 35 200 150 5 21PF / TSB 220 35 180 65 Noraml 6 21PF / LG 230 35 230 65 7 21PF / SDI 220 35 210 65 8 25PF / SDI 210 35 160 120 9 29” 1.3R / SDI 200 35 170 150 5. Turn the SCREEN VR until “MRCR G B” and “MRWDG” are green and those value are about 100. (The incorrect SCREEN Voltage may result that “MRCR G B” and “MRWDG” should be red) 4-2 Samsung Electronics Alignment and Adjustments 4-6 E2PROM (IC902) Replacement 1. -

Digital Video Quality Handbook (May 2013

Digital Video Quality Handbook May 2013 This page intentionally left blank. Executive Summary Under the direction of the Department of Homeland Security (DHS) Science and Technology Directorate (S&T), First Responders Group (FRG), Office for Interoperability and Compatibility (OIC), the Johns Hopkins University Applied Physics Laboratory (JHU/APL), worked with the Security Industry Association (including Steve Surfaro) and members of the Video Quality in Public Safety (VQiPS) Working Group to develop the May 2013 Video Quality Handbook. This document provides voluntary guidance for providing levels of video quality in public safety applications for network video surveillance. Several video surveillance use cases are presented to help illustrate how to relate video component and system performance to the intended application of video surveillance, while meeting the basic requirements of federal, state, tribal and local government authorities. Characteristics of video surveillance equipment are described in terms of how they may influence the design of video surveillance systems. In order for the video surveillance system to meet the needs of the user, the technology provider must consider the following factors that impact video quality: 1) Device categories; 2) Component and system performance level; 3) Verification of intended use; 4) Component and system performance specification; and 5) Best fit and link to use case(s). An appendix is also provided that presents content related to topics not covered in the original document (especially information related to video standards) and to update the material as needed to reflect innovation and changes in the video environment. The emphasis is on the implications of digital video data being exchanged across networks with large numbers of components or participants. -

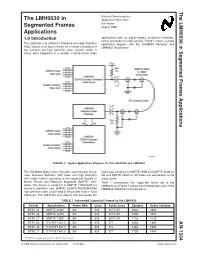

Application Note 1334 the LMH0030 in Segmented Frames Applications

The LMH0030 in Segmented Frames Applications AN-1334 National Semiconductor The LMH0030 in Application Note 1334 Kai Peters Segmented Frames August 2006 Applications 1.0 Introduction applications such as digital routers, production switchers, format converters or video servers. Figure 1 shows a typical The LMH0030 and LMH0031 Standard and High Definition application diagram with the LMH0030 Serializer and Video chipset is an ideal solution for a variety of products in LMH0031 Deserializer. the standard and high definition video systems realm. It allows easy integration in a number of professional video 20108501 FIGURE 1. Typical Application Diagram for the LMH0030 and LMH0031 The LMH0030 Digital Video Serializer automatically recog- video data compliant to SMPTE 259M and SMPTE 344M for nizes Standard Definition (SD) video and High Definition SD and SMPTE 292M for HD Video and serialization to the (HD) video formats according to the respective Society of output ports. Motion Picture and Television Engineers (SMPTE) stan- Table 1 summarizes the supported frame set of the dards. The device is compliant to SMPTE 125M/267M for LMH0030 and Figure 2 shows the simplified data path of the standard definition and SMPTE 260M/274M/295M/296M LMH0030 SD/HD Encoder/Serializer. high definition video as provided to the parallel 10bit or 20bit interfaces. The LMH0030 auto-detects and processes the TABLE 1. Automated Supported Frames by the LMH0030 Format Apecification Frame Rate Lines Active Lines Samples Active Samples SDTV, 54 SMPTE 344M 60I 525 507/1487 3432 2880 SDTV, 36 SMPTE 267M 60I 525 507/1487 2288 1920 SDTV, 27 SMPTE 125M 60I 525 507/1487 1716 1440 SDTV, 54 ITU-R BT 601.5 50I 625 577 3456 2880 SDTV, 36 ITU-R BT 601.5 50I 625 577 2304 1920 SDTV, 27 ITU-R BT 601.5 50I 625 577 1728 1440 PHYTER® is a registered trademark of National Semiconductor. -

Model 5280 Digital to Analog Composite Video Converter Data Pack

Model 5280 Digital to Analog Composite Video Converter Data Pack ENSEMBLE DESIGNS Revision 2.1 SW v2.0 This data pack provides detailed installation, configuration and operation information for the 5280 Digital to Analog Composite Video Converter and the 5210 Genlock option submodule as part of the Avenue Signal Integration System. The module information in this data pack is organized into the following sections: • Module Overview • Applications • Installation • Cabling • Module Configuration and Control ° Front Panel Controls and Indicators ° Avenue PC Remote Control ° Avenue Touch Screen Remote Control • Troubleshooting • Software Updating • Warranty and Factory Service • Specifications 5280-1 Model 5280 Video DAC MODULE OVERVIEW The 5280 module converts serial digital component video into composite analog video. Six separate composite or two Y/C (S-video) analog video outputs are available. The following analog formats are supported: • NTSC Composite with or without setup • PAL Composite A serial output BNC is provided for applications requiring the serial digital input signal to loop-through to another device. Output timing can be adjusted relative to a reference input signal by installing the 5210 Genlock Option, a submodule that plugs onto the 5280 circuit board. Incorporating a full- frame synchronizer, the 5210 also allows the 5280 to accept serial inputs that are asyn- chronous to the reference. As shown in the block diagram on the following page, the serial digital input signal first passes through serial receiver circuitry then on to EDH processing and deserializing. The serial output signal goes to a cable driver and is then AC coupled to a loop-through output BNC on the backplane. -

Bit-Serial Digital Interface for High-Definition Television Systems

ANSI/SMPTE 292M-1996 SMPTE STANDARD for Television ---- Bit-Serial Digital Interface for High-Definition Television Systems Page 1 of 9 pages 1 Scope ANSI/SMPTE 274M-1995, Television ---- 1920 × 1080 Scanning and Interface This standard defines a bit-serial digital coaxial and fiber-optic interface for HDTV component signals ANSI/SMPTE 291M-1996, Television ---- Ancillary operating at data rates in the range of 1.3 Gb/s to 1.5 Data Packet and Space Formatting Gb/s. Bit-parallel data derived from a specified source format are multiplexed and serialized to form the serial SMPTE RP 184-1995, Measurement of Jitter in Bit- data stream. A common data format and channel Serial Digital Interfaces coding are used based on modifications, if necessary, to the source format parallel data for a given high- IEC 169-8 (1978), Part 8: R.F. Coaxial Connectors with definition television system. Coaxial cable interfaces Inner Diameter of Outer Conductor 6.5 mm (0.256 in) are suitable for application where the signal loss does with Bayonet Lock ---- Characteristic Impedance 50 not exceed an amount specified by the receiver manu- Ohms (Type BNC), and Appendix A (1993) facturer. Typical loss amounts would be in the range of up to 20 dB at one-half the clock frequency. Fiber IEC 793-2 (1992), Optical Fibres, Part 2: Product optic interfaces are suitable for application at up to 2 Specifications km of distance using single-mode fiber. IEC 874-7 (1990), Part 7: Fibre Optic Connector Several source formats are referenced and others Type FC operating within the covered data rate range may be serialized based on the techniques defined by this 3 Definition of terms standard. -

Presentation Title Sub-Title / Date

Review of HDTV (production) standards Hans Hoffmann Senior Engineer Technical Department, EBU [email protected] Overview HDTV basics Interfaces Compression HD-Ready, HDTV-Ready, EBU Demos @ IBC2005 1080p/50 Summary Uncompromised quality of Sound and Video Details (for advertisements) “Bad” HDTV more annoying than “bad” SDTV High-Definition Television Design Viewing Distance: max. 3h on a 50inch display Preferred Viewing Distance: Line or pixel structure Picture width pw [m] ] c/pw [m ph Line density Ld [m] not visible gh h ] e hi D [m ur c/p nal ago s] ct Di che Pi [in 1' (1/ . 60° ) View in g Dista [m] n ce d α Definitions • SDTV: – 625-line TV = active 576 lines, “576i/25” – 525-line TV = active 480 lines, “480i/29.94” • HDTV: – 1080i/25 – 1080p/25 or 1080p/24 – 720p/50 – 1080p/50 •Interlaced or progressive scan HDTV – Options in the Signal Chain Creation Production Encoder Distribution Decoder Interfacing Display What did we learn from theSat. SDTV debate on interfaces and compression?DTT. IP etc. • The wholeSig. Process.signal chain determines STBthe final qualityDisplay at theCompression consumer Decoder Studio-InterfacesHDTV is muchSignal Processimoreng sensitiveContribution to technicalNew STBand Display HD-SDI (1.485Gb) P/I still MPEG-2 (VC-1, H264) HD-Ready HD-SDI (3Gb) artistical1080i/25 errors. 422P@HL HDTV Ready 720p/50-60 10 Gb? 1080p/25 Emission format (720p/50 1080i/25-30 HD-SDTI • We 1080p/24need to be moreH.264-AcarefulVC and have1080i/25)to provide 720p/50 prop. SMPTE VC1 Impact of sufficient1080p/50 quality 720p/50headroom in the studio. -

AXI Reference Guide

AXI Reference Guide [Guide Subtitle] [optional] UG761 (v13.4) January 18, 2012 [optional] Xilinx is providing this product documentation, hereinafter “Information,” to you “AS IS” with no warranty of any kind, express or implied. Xilinx makes no representation that the Information, or any particular implementation thereof, is free from any claims of infringement. You are responsible for obtaining any rights you may require for any implementation based on the Information. All specifications are subject to change without notice. XILINX EXPRESSLY DISCLAIMS ANY WARRANTY WHATSOEVER WITH RESPECT TO THE ADEQUACY OF THE INFORMATION OR ANY IMPLEMENTATION BASED THEREON, INCLUDING BUT NOT LIMITED TO ANY WARRANTIES OR REPRESENTATIONS THAT THIS IMPLEMENTATION IS FREE FROM CLAIMS OF INFRINGEMENT AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Except as stated herein, none of the Information may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. © Copyright 2012 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, Kintex, Artix, ISE, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners. ARM® and AMBA® are registered trademarks of ARM in the EU and other countries. All other trademarks are the property of their respective owners. Revision History The following table shows the revision history for this document: . Date Version Description of Revisions 03/01/2011 13.1 Second Xilinx release. -

Analog to Digital Converter User Guide

Analog to Digital Converter User Guide ENSEMBLE DESIGNS Revision 5 SW v1.0.7 This user guide provides detailed information for using the BrightEye™2 Analog to Digital Converter. The information in this user guide is organized into the following sections: • Product Overview • Functional Description • Applications • Rear Connections • Operation • Front Panel Controls and Indicators • Using The BrightEye Control Application • Warranty and Factory Service • Specifications • Glossary BrightEye-1 BrightEye 2 Analog to Digital Converter PRODUCT OVERVIEW The BrightEye 2 Converter is a self-contained unit that provides uncompromised analog to digital conversion of component and composite video. Analog inputs are digitized at 12 bits of resolution with 4x oversampling. Composite video is processed through an adaptive comb filter decoder. PAL and NTSC input detection is automatic. Signal I/O and power is supplied to the rear of the unit. It is powered by a modular style power supply. Supporting both Beta and SMPTE component, composite and Y/C formats, BrightEye 2 adapts to many conversion needs. Use BrightEye 2 to digitize analog VTR and camera outputs for example. Front panel controls permit the user to monitor input status, select input type, and adjust video gain. Control and monitoring can also be done using the BrightEye Control application from a personal computer with USB support. A glossary of commonly used video terms is provided at the end of this guide. FUNCTIONAL DESCRIPTION The BrightEye 2 converter can perform analog to digital conversion on a variety of television signal formats, in both the 525/60Hz (NTSC) and 625/50Hz (PAL) line standards. The converter supports the NTSC and PAL composite standards, Y/C, and color difference analog component formats. -

Types of Video Signals

WIKIPEDIA SOURCE TYPES OF VIDEO SIGNALS Component video is a video signal that has been split into two or more component channels. In popular use, it refers to a type of component analog video (CAV) information that is transmitted or stored as three separate signals. Component video can be contrasted with composite video (NTSC, PAL or SECAM) in which all the video information is combined into a single line-level signal that is used in analog television. Like composite, component-video cables do not carry audio and are often paired with audio cables. When used without any other qualifications the term component video generally refers to analog YPbPr component video with sync on luma. Analog component video Reproducing a video signal on a display device (for example, a Cathode ray tube) (CRT) is a straightforward process complicated by the multitude of signal sources. DVD, VHS, computers and video game consoles all store, process and transmit video signals using different methods, and often each will provide more than one signal option. One way of maintaining signal clarity is by separating the components of a video signal so that they do not interfere with each other. A signal separated in this way is called "component video". S-Video, RGB and YPbPr signals comprise two or more separate signals: hence, all are component-video signals. For most consumer-level applications, analog component video is used. Digital component video is slowly becoming popular in both computer and home-theatre applications. Component video is capable of carrying signals such as 480i, 480p, 576i, 576p, 720p, and 1080i. -

MC44CM373/4 Audio/Video RF CMOS Fact Sheet

Audio/Video RF CMOS Modulators MC44CM373/4 The MC44CM373/MC44CM374 CMOS family of RF modulators is the latest generation of the legacy MC44BS373/4 family of devices. The MC44CM373/4 RF modulators are designed for use in VCRs, set-top boxes and similar devices. They support multiple standards and can be programmed to support PAL, SECAM or NTSC formats. The devices are programmed by a high-speed I2C bus. The MC44CM373/374 family is backward compatible with the previous I2C control software, providing a smooth transition for system upgrades. A programmable, internal Phase-Lock Loop (PLL), with an on-chip, cost-effective tank covers the full UHF range. The modulators incorporate a programmable, on-chip, sound subcarrier oscillator that covers all broadcast standards. No external tank Orderable Part Numbers circuit components are required, reducing New Part Number Replaces PCB complexity and the need for external MC44BS373CAD adjustments. The PLL obtains its reference MC44CM373CAEF MC44BS373CAEF from a cost-effective 4 MHz crystal oscillator. MC44BS373CAFC The devices are available in a 16-pin SOIC, MC44CM373CASEF (secondary I2C address) MC44BS373CAFC Pb-free package. These parts are functionally MC44BS374CAD MC44CM374CAEF equivalent to the MC44BS373/4 series, but MC44BS374CAEF are not direct drop-in replacements. MC44BS374T1D MC44BS374T1EF All devices now include the aux input found MC44CM374T1AEF MC44BS374T1AD previously only on the 20-pin package MC44BS374T1AEF option. This is a direct input for a modulated subcarrier and is useful in BTSC or NICAM Typical Applications stereo sound or other subcarrier applications. The MC44CM373 and MC44CM374 RF modulators are intended for applications The MC44CM373CASEF has a secondary I2C within IP/DSL, digital terrestrial, satellite address for applications using two modulators or cable set-top boxes, VCRs and DVD on one I2C Bus.