Adv7177/Adv7178

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Iagrams TH EW)

iagrams TH EW) TP07 TP10 TP08 TP09 TP09 TP01 TP06 TP10 TP08 TP05 TP07 TP03 TP02 TP04 : Power Lin : Signal Lin TP12 TP13 TP15 TP11 TP14 TP22 TP23 TP23 TP22 TP24 TP16 TP18 TP17 TP25 TP21 TP19 TP24 TP20 TP25 TP32 TP33 TP35 TP26 TP33 TP34 TP34 TP27 TP32 TP35 TP31 TP28 TP29 TP30 : Power Line : Signal Line -EW) H Alignment and Adjustments 4-4 FOCUS Adjustment 1. Input a black and white signal. 2. Adjust the tuning control for the clearest picture. 3. Adjust the FOCUS control for well defined scanning lines in the center area of the screen. 4-5 SCREEN Adjustment 1. Input Toshiba Pattern 2. Enter “Service Mode”.(Refer to “4-8-1 Service Mode”) 3. Select “G2-Adjust”. 4. Set the values as below. Table 1. Screen Adjustment Table COLR G B No INCH / CRT REGION IBRM WDRV CDL (Smallest Value) 1 14” / SDI 205 35 100 100 Noraml 220 35 180 100 2 15PF / SDI 215 35 100 100 CIS 3 21” 1.7R / SDI 220 35 180 100 4 21” 1.7R / JCT 220 35 200 150 5 21PF / TSB 220 35 180 65 Noraml 6 21PF / LG 230 35 230 65 7 21PF / SDI 220 35 210 65 8 25PF / SDI 210 35 160 120 9 29” 1.3R / SDI 200 35 170 150 5. Turn the SCREEN VR until “MRCR G B” and “MRWDG” are green and those value are about 100. (The incorrect SCREEN Voltage may result that “MRCR G B” and “MRWDG” should be red) 4-2 Samsung Electronics Alignment and Adjustments 4-6 E2PROM (IC902) Replacement 1. -

AXI Reference Guide

AXI Reference Guide [Guide Subtitle] [optional] UG761 (v13.4) January 18, 2012 [optional] Xilinx is providing this product documentation, hereinafter “Information,” to you “AS IS” with no warranty of any kind, express or implied. Xilinx makes no representation that the Information, or any particular implementation thereof, is free from any claims of infringement. You are responsible for obtaining any rights you may require for any implementation based on the Information. All specifications are subject to change without notice. XILINX EXPRESSLY DISCLAIMS ANY WARRANTY WHATSOEVER WITH RESPECT TO THE ADEQUACY OF THE INFORMATION OR ANY IMPLEMENTATION BASED THEREON, INCLUDING BUT NOT LIMITED TO ANY WARRANTIES OR REPRESENTATIONS THAT THIS IMPLEMENTATION IS FREE FROM CLAIMS OF INFRINGEMENT AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Except as stated herein, none of the Information may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. © Copyright 2012 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, Kintex, Artix, ISE, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners. ARM® and AMBA® are registered trademarks of ARM in the EU and other countries. All other trademarks are the property of their respective owners. Revision History The following table shows the revision history for this document: . Date Version Description of Revisions 03/01/2011 13.1 Second Xilinx release. -

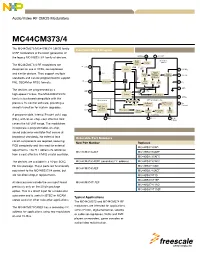

MC44CM373/4 Audio/Video RF CMOS Fact Sheet

Audio/Video RF CMOS Modulators MC44CM373/4 The MC44CM373/MC44CM374 CMOS family of RF modulators is the latest generation of the legacy MC44BS373/4 family of devices. The MC44CM373/4 RF modulators are designed for use in VCRs, set-top boxes and similar devices. They support multiple standards and can be programmed to support PAL, SECAM or NTSC formats. The devices are programmed by a high-speed I2C bus. The MC44CM373/374 family is backward compatible with the previous I2C control software, providing a smooth transition for system upgrades. A programmable, internal Phase-Lock Loop (PLL), with an on-chip, cost-effective tank covers the full UHF range. The modulators incorporate a programmable, on-chip, sound subcarrier oscillator that covers all broadcast standards. No external tank Orderable Part Numbers circuit components are required, reducing New Part Number Replaces PCB complexity and the need for external MC44BS373CAD adjustments. The PLL obtains its reference MC44CM373CAEF MC44BS373CAEF from a cost-effective 4 MHz crystal oscillator. MC44BS373CAFC The devices are available in a 16-pin SOIC, MC44CM373CASEF (secondary I2C address) MC44BS373CAFC Pb-free package. These parts are functionally MC44BS374CAD MC44CM374CAEF equivalent to the MC44BS373/4 series, but MC44BS374CAEF are not direct drop-in replacements. MC44BS374T1D MC44BS374T1EF All devices now include the aux input found MC44CM374T1AEF MC44BS374T1AD previously only on the 20-pin package MC44BS374T1AEF option. This is a direct input for a modulated subcarrier and is useful in BTSC or NICAM Typical Applications stereo sound or other subcarrier applications. The MC44CM373 and MC44CM374 RF modulators are intended for applications The MC44CM373CASEF has a secondary I2C within IP/DSL, digital terrestrial, satellite address for applications using two modulators or cable set-top boxes, VCRs and DVD on one I2C Bus. -

High Definition Analog Component Measurements

Application Note High Definition Analog Component Measurements Requirements for Measuring Analog Component HD Signals for Video Devices The transition to digital has enabled great strides in the of these devices. When an image is captured by a color processing of video signals, allowing a variety of camera and converted from light to an electrical signal, techniques to be applied to the video image. Despite the signal is comprised of three components - Red, these benefits, the final signal received by the customer Green and Blue (RGB). From the combination of these is still converted to an analog signal for display on a three signals, a representation of the original image can be picture monitor. With the proliferation of a wide variety conveyed to a color display. The various video processing of digital devices - set-top boxes, Digital Versatile Disk systems within the signal paths need to process the (DVD) players and PC cards - comes a wide range of three components identically, in order not to introduce video formats in addition to the standard composite any amplitude or channel timing errors. Each of the three output. It is therefore necessary to understand the components R’G’B’ (the ( ’ ) indicates that the signal requirements for measuring analog component High has been gamma corrected) has identical bandwidth, Definition (HD) signals in order to test the performance which increases complexity within the digital domain. High Definition Analog Component Measurements Application Note Y’, R’-Y’, B’-Y’, Commonly Used for Analog Component Analog Video Format 1125/60/2:1 750/60/1:1 525/59.94/1:1, 625/50/1:1 Y’ 0.2126 R’ + 0.7152 G’ + 0.0722 B’ 0.299 R’ + 0.587 G’ + 0.114 B’ R’-Y’ 0.7874 R’ - 0.7152 G’ - 0.0722 B’ 0.701 R’ - 0.587 G’ - 0.114 B’ B’-Y’ - 0.2126 R’ - 0.7152 G’ + 0.9278 B’ - 0.299 R’ - 0.587 G’ + 0.886 B’ Table 1. -

Basics of Video

Basics of Video Yao Wang Polytechnic University, Brooklyn, NY11201 [email protected] Video Basics 1 Outline • Color perception and specification (review on your own) • Video capture and disppy(lay (review on your own ) • Analog raster video • Analog TV systems • Digital video Yao Wang, 2013 Video Basics 2 Analog Video • Video raster • Progressive vs. interlaced raster • Analog TV systems Yao Wang, 2013 Video Basics 3 Raster Scan • Real-world scene is a continuous 3-DsignalD signal (temporal, horizontal, vertical) • Analog video is stored in the raster format – Sampling in time: consecutive sets of frames • To render motion properly, >=30 frame/s is needed – Sampling in vertical direction: a frame is represented by a set of scan lines • Number of lines depends on maximum vertical frequency and viewingg, distance, 525 lines in the NTSC s ystem – Video-raster = 1-D signal consisting of scan lines from successive frames Yao Wang, 2013 Video Basics 4 Progressive and Interlaced Scans Progressive Frame Interlaced Frame Horizontal retrace Field 1 Field 2 Vertical retrace Interlaced scan is developed to provide a trade-off between temporal and vertical resolution, for a given, fixed data rate (number of line/sec). Yao Wang, 2013 Video Basics 5 Waveform and Spectrum of an Interlaced Raster Horizontal retrace Vertical retrace Vertical retrace for first field from first to second field from second to third field Blanking level Black level Ӈ Ӈ Th White level Tl T T ⌬t 2 ⌬ t (a) Խ⌿( f )Խ f 0 fl 2fl 3fl fmax (b) Yao Wang, 2013 Video Basics 6 Color -

Understanding HD and 3G-SDI Video Poster

Understanding HD & 3G-SDI Video EYE DIGITAL SIGNAL TIMING EYE DIAGRAM The eye diagram is constructed by overlaying portions of the sampled data stream until enough data amplitude is important because of its relation to noise, and because the Y', R'-Y', B'-Y', COMMONLY USED FOR ANALOG COMPONENT ANALOG VIDEO transitions produce the familiar display. A unit interval (UI) is defined as the time between two adjacent signal receiver estimates the required high-frequency compensation (equalization) based on the Format 1125/60/2:1 750/60/1:1 525/59.94/2:1, 625/50/2:1, 1250/50/2:1 transitions, which is the reciprocal of clock frequency. UI is 3.7 ns for digital component 525 / 625 (SMPTE remaining half-clock-frequency energy as the signal arrives. Incorrect amplitude at the Y’ 0.2126 R' + 0.7152 G' + 0.0722 B' 0.299 R' + 0.587 G' + 0.114 B' 259M), 673.4 ps for digital high-definition (SMPTE 292) and 336.7ps for 3G-SDI serial digital (SMPTE 424M) sending end could result in an incorrect equalization applied at the receiving end, thus causing Digital video synchronization is provided by End of Active Video (EAV) and Start of Active Video (SAV) sequences which start with a R'-Y' 0.7874 R' - 0.7152 G' - 0.0722 B' 0.701 R' - 0.587 G' - 0.114 B' as shown in Table 1. A serial receiver determines if the signal is “high” or “low” in the center of each eye, and signal distortions. Overshoot of the rising and falling edge should not exceed 10% of the waveform HORIZONTAL LINE TIMING unique three word pattern: 3FFh (all bits in the word set to 1), 000h (all 0’s), 000h (all 0’s), followed by a fourth “XYZ” word whose B'-Y' -0.2126 R' - 0.7152 G' + 0.9278 B' -0.299 R' - 0.587 G' + 0.886 B' detects the serial data. -

VPC 3205C, VPC 3215C Video Processor Family

PRELIMINARY DATA SHEET MICRONAS VPC 3205C, VPC 3215C Video Processor Family Edition Oct. 19, 1998 6251-457-2PD MICRONAS VPC 3205C, VPC 3215C PRELIMINARY DATA SHEET Contents Page Section Title 4 1. Introduction 4 1.1. System Architecture 4 1.2. Video Processor Family 5 1.3. VPC Applications 6 2. Functional Description 6 2.1. Analog Front-End 6 2.1.1. Input Selector 6 2.1.2. Clamping 6 2.1.3. Automatic Gain Control 6 2.1.4. Analog-to-Digital Converters 6 2.1.5. Digitally Controlled Clock Oscillator 6 2.1.6. Analog Video Output 7 2.2. Adaptive Comb Filter 7 2.3. Color Decoder 8 2.3.1. IF-Compensation 8 2.3.2. Demodulator 8 2.3.3. Chrominance Filter 9 2.3.4. Frequency Demodulator 9 2.3.5. Burst Detection 9 2.3.6. Color Killer Operation 9 2.3.7. PAL Compensation/1-H Comb Filter 10 2.3.8. Luminance Notch Filter 10 2.3.9. Skew Filtering 11 2.4. Horizontal Scaler 11 2.5. Blackline Detector 11 2.6. Control and Data Output Signals 11 2.6.1. Line-Locked Clock Generation 12 2.6.2. Sync Signals 12 2.6.3. DIGIT3000 Output Format 12 2.6.4. Line-Locked 4:2:2 Output Format 12 2.6.5. Line-Locked 4:1:1 Output Format 12 2.6.6. Output Code Levels 12 2.6.7. Output Signal Levels 12 2.6.8. Test Pattern Generator 13 2.6.9. Priority Bus Codec 13 2.7. -

MICRONAS VDP 31Xxb Video Processor Family��������������

查询VDP31XXB供应商 捷多邦,专业PCB打样工厂,24小时加急出货 PRELIMINARY DATA SHEET MICRONAS VDP 31xxB Video Processor Family Edition Sept. 25, 1998 6251-437-2PD MICRONAS VDP 31xxB PRELIMINARY DATA SHEET Contents Page Section Title 5 1. Introduction 6 1.1. VDP Applications 7 2. Functional Description 7 2.1. Analog Front-End 7 2.1.1. Input Selector 7 2.1.2. Clamping 7 2.1.3. Automatic Gain Control 7 2.1.4. Analog-to-Digital Converters 7 2.1.5. ADC Range 7 2.1.6. Digitally Controlled Clock Oscillator 7 2.1.7. Analog Video Output 9 2.2. Adaptive Comb Filter 10 2.3. Color Decoder 10 2.3.1. IF-Compensation 11 2.3.2. Demodulator 11 2.3.3. Chrominance Filter 11 2.3.4. Frequency Demodulator 11 2.3.5. Burst Detection 11 2.3.6. Color Killer Operation 11 2.3.7. PAL Compensation/1-H Comb Filter 12 2.3.8. Luminance Notch Filter 12 2.3.9. Skew Filtering 13 2.4. Horizontal Scaler 13 2.5. Black-Line Detector 13 2.6. Test Pattern Generator 14 2.7. Video Sync Processing 15 2.8. Display Part 15 2.8.1. Luma Contrast Adjustment 15 2.8.2. Black Level Expander 16 2.8.3. Dynamic Peaking 17 2.8.4. Digital Brightness Adjustment 17 2.8.5. Soft Limiter 17 2.8.6. Chroma Input 17 2.8.7. Chroma Interpolation 18 2.8.8. Chroma Transient Improvement 18 2.8.9. Inverse Matrix 18 2.8.10. RGB Processing 18 2.8.11. -

NTSC Specifications

NTSC Modulation Standard ━━━━━━━━━━━━━━━━━━━━━━━━ The Impressionistic Era of TV. It©s Never The Same Color! The first analog Color TV system realized which is backward compatible with the existing B & W signal. To combine a Chroma signal with the existing Luma(Y)signal a quadrature sub-carrier Chroma signal is used. On the Cartesian grid the x & y axes are defined with B−Y & R−Y respectively. When transmitted along with the Luma(Y) G−Y signal can be recovered from the B−Y & R−Y signals. Matrixing ━━━━━━━━━ Let: R = Red \ G = Green Each range from 0 to 1. B = Blue / Y = Matrixed B & W Luma sub-channel. U = Matrixed Blue Chroma sub-channel. U #2900FC 249.76° −U #D3FC00 69.76° V = Matrixed Red Chroma sub-channel. V #FF0056 339.76° −V #00FFA9 159.76° W = Matrixed Green Chroma sub-channel. W #1BFA00 113.52° −W #DF00FA 293.52° HSV HSV Enhanced channels: Hue Hue I = Matrixed Skin Chroma sub-channel. I #FC6600 24.29° −I #0096FC 204.29° Q = Matrixed Purple Chroma sub-channel. Q #8900FE 272.36° −Q #75FE00 92.36° We have: Y = 0.299 × R + 0.587 × G + 0.114 × B B − Y = −0.299 × R − 0.587 × G + 0.886 × B R − Y = 0.701 × R − 0.587 × G − 0.114 × B G − Y = −0.299 × R + 0.413 × G − 0.114 × B = −0.194208 × (B − Y) −0.509370 × (R − Y) (−0.1942078377, −0.5093696834) Encode: If: U[x] = 0.492111 × ( B − Y ) × 0° ┐ Quadrature (0.4921110411) V[y] = 0.877283 × ( R − Y ) × 90° ┘ Sub-Carrier (0.8772832199) Then: W = 1.424415 × ( G − Y ) @ 235.796° Chroma Vector = √ U² + V² Chroma Hue θ = aTan2(V,U) [Radians] If θ < 0 then add 2π.[360°] Decode: SyncDet U: B − Y = -┼- @ 0.000° ÷ 0.492111 V: R − Y = -┼- @ 90.000° ÷ 0.877283 W: G − Y = -┼- @ 235.796° ÷ 1.424415 (1.4244145537, 235.79647610°) or G − Y = −0.394642 × (B − Y) − 0.580622 × (R − Y) (−0.3946423068, −0.5806217020) These scaling factors are for the quadrature Chroma signal before the 0.492111 & 0.877283 unscaling factors are applied to the B−Y & R−Y axes respectively. -

Secam Decoder

MITSUBISHI LINEAR INTEGRATED CIRCUIT M52325AP SECAM DECODER [GENERAL DESCRIPTION] pin configuration The M52325AP is designed for SECAM chrominance decoding.The IC should preferably be used in conjunction with PAL / NTSC signal processor M52340SP and the fref / IDENT 1 16 CVBS IN switched capacitor baseband delay line. It consists of a bell filter,a demodulator and an identification BELL OUT 2 15 SAND IN circuit. The IC needs no adjustment and few external Vcc 3 M52325AP 14 BLACK ADJ. R components are required. A signal with highly stable BAND GAP 4 13 PLL auto 1 reference frequency is required for the calibration, and a three - level sandcastle pulse for blanking and burst gating. SACAM KILLER OUT 5 12 PLL auto2 GND 6 11 BLACK ADJ. B BELL ref. 7 10 - (B - Y ) OUT [FEATURES] PLL ref. 8 9 - (R - Y ) OUT • Fully integrated filters 16 PIN DIL PLASTIC PACKAGE • No adjustment • Few external compornents • Used with a switched capacitor baseband delay line [STRUCRURE] [APPLICATION] Bipolar Silicon Monolithic IC SECAM Color Television 16 PIN DIL PLASTIC PACKAGE [QUICK REFERENCE DATA] SYMBOL PARAMETER MIN. TYP. MAX. UNIT positive power supply Vcc pin3 7.5 8.0 8.5 V Icc supply current pin3 18 24 30 mA input dynamic range VDR - 1.0 1.4 Vp-p pin16 -(R-Y) output voltage amplitude VR-Y 0.85 1.00 1.15 Vp-p (peak to peak value) ;pin9 -(B-Y) output voltage amplitude VB-Y (peak to peak value) ;pin10 1.10 1.24 1.43 Vp-p MITSUBISHI 1 - 13 MITSUBISHI LINEAR INTEGRATED CIRCUIT M52325AP SECAM DECODER Vcc=8.0V 0.1µ F + BELL PLL PLL OUT 22µF auto2 auto1 0.1µF 2 12 13 3 BAND GAP BANDGAP 4 CVBS IN BELL ACC AMP PLL 16 FILTER B-Y 10 -(B-Y) BELL OUTPUT OUT ref. -

AD8188/AD8189 350 Mhz Single-Supply (5 V)

350 MHz Single-Supply (5 V) Triple 2:1 Multiplexers AD8188/AD8189 FEATURES FUNCTIONAL BLOCK DIAGRAM Fully buffered inputs and outputs IN0A 1 24 VCC Fast channel-to-channel switching: 4 ns DGND 2 LOGIC 23 OE Single-supply operation (5 V) IN1A 3 22 SEL A/B V 4 SELECT 21 V High speed REF ENABLE CC 350 MHz bandwidth (−3 dB) @ 200 mV p-p IN2A 5 0 20 OUT0 300 MHz bandwidth (−3 dB) @ 2 V p-p VCC 6 19 VEE Slew rate: 1000 V/μs VEE 7 1 18 OUT1 Fast settling time: 7 ns to 0.1% IN2B 8 17 VCC V 9 2 16 OUT2 Low current: 19 mA/20 mA EE IN1B 10 15 VEE Excellent video specifications: load resistor (RL) = 150 Ω VEE 11 14 DVCC Differential gain error: 0.05% IN0B 12 AD8188/AD8189 13 VCC Differential phase error: 0.05° 06239-001 Low glitch Figure 1. All hostile crosstalk −84 dB @ 5 MHz −52 dB @ 100 MHz High off isolation: −95 dB @ 5 MHz Low cost Fast, high impedance disable feature for connecting multiple outputs Logic-shifted outputs APPLICATIONS Switching RGB in LCD and plasma displays RGB video switchers and routers GENERAL DESCRIPTION The AD8188 (G = 1) and AD8189 (G = 2) are high speed, 4.0 6.0 single-supply, triple 2-to-1 multiplexers. They offer −3 dB small 3.5 5.5 signal bandwidth of 350 MHz and −3 dB large signal bandwidth 3.0 5.0 of 300 MHz, along with a slew rate in excess of 1000 V/μs. -

SAA7114 PAL/NTSC/SECAM Video Decoder with Adaptive PAL/NTSC Comb filter, VBI Data Slicer and High Performance Scaler Rev

SAA7114 PAL/NTSC/SECAM video decoder with adaptive PAL/NTSC comb filter, VBI data slicer and high performance scaler Rev. 03 — 17 January 2006 Product data sheet 1. General description The SAA7114 is a video capture device for applications at the image port of Video Graphics Array (VGA) controllers. The SAA7114 is a combination of a two-channel analog preprocessing circuit including source selection, anti-aliasing filter and Analog-to-Digital Converter (ADC), an automatic clamp and gain control, a Clock Generation Circuit (CGC), a digital multistandard decoder containing two-dimensional chrominance/luminance separation by an adaptive comb filter and a high performance scaler, including variable horizontal and vertical up and downscaling and a brightness, contrast and saturation control circuit. It is a highly integrated circuit for desktop video and similar applications. The decoder is based on the principle of line-locked clock decoding and is able to decode the color of PAL, SECAM and NTSC signals into ITU 601 compatible color component values. The SAA7114 accepts CVBS or S-video (Y/C) as analog inputs from TV or VCR sources, including weak and distorted signals. An expansion port (X port) for digital video (bidirectional half duplex, D1 compatible) is also supported to connect to MPEG or a video phone codec. At the so called image port (I port) the SAA7114 supports 8-bit or 16-bit wide output data with auxiliary reference data for interfacing to VGA controllers. The target application for the SAA7114 is to capture and scale video images, to be provided as a digital video stream through the image port of a VGA controller, for display via the frame buffer of the VGA, or for capture to system memory.