Evolution of Microprocessor Lecture Notes

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

An Introduction to Microcontrollers and Embedded Systems

AN INTRODUCTION TO MICROCONTROLLERS AND EMBEDDED SYSTEMS Tyler Ross Lambert MECH 4240/4250 Supplementary Information Last Revision: 6/7/2017 5:30 PM Summary Embedded systems in robotics are the framework that allows electro-mechanical systems to be implemented into modern machines. The key aspects of this framework are C programming in embedded controllers, circuits for interfacing microcontrollers with sensors and actuators, and proper filtering and control of those hardware components. This document will cover the basics of C/C++ programming, including the basics of the C language in hardware interfacing, communication, and algorithms for state machines and controllers. In order to interface these controllers with the world around us, this document will also cover electrical circuits required to operate controllers, sensors, and actuators accurately and effectively. Finally, some of the more commonly used hardware that is interfaced with microcontrollers is gone over. Table of Contents 1. Introduction ....................................................................................................................................... 4 2. Numbering Systems .......................................................................................................................... 5 3. Variable Types and Memory............................................................................................................. 6 4. Basic C/C++ Notes and Code::Blocks ............................................................................................. -

Digital Preservation Guide: 3.5-Inch Floppy Disks Caralie Heinrichs And

DIGITAL PRESERVATION GUIDE: 3.5-Inch Floppy Disks Digital Preservation Guide: 3.5-Inch Floppy Disks Caralie Heinrichs and Emilie Vandal ISI 6354 University of Ottawa Jada Watson Friday, December 13, 2019 DIGITAL PRESERVATION GUIDE 2 Table of Contents Introduction ................................................................................................................................................. 3 History of the Floppy Disk ......................................................................................................................... 3 Where, when, and by whom was it developed? 3 Why was it developed? 4 How Does a 3.5-inch Floppy Disk Work? ................................................................................................. 5 Major parts of a floppy disk 5 Writing data on a floppy disk 7 Preservation and Digitization Challenges ................................................................................................. 8 Physical damage and degradation 8 Hardware and software obsolescence 9 Best Practices ............................................................................................................................................. 10 Storage conditions 10 Description and documentation 10 Creating a disk image 11 Ensuring authenticity: Write blockers 11 Ensuring reliability: Sustainability of the disk image file format 12 Metadata 12 Virus scanning 13 Ensuring integrity: checksums 13 Identifying personal or sensitive information 13 Best practices: Use of hardware and software 14 Hardware -

Introductory Microcontroller Programming

Introductory Microcontroller Programming by Peter Alley A Thesis Submitted to the Faculty of the WORCESTER POLYTECHNIC INSTITUTE in partial fulfillment of the requirements for the Degree of Master of Science in Robotics Engineering May 2011 Prof. William Michalson Advisor Prof. Taskin Padir Prof. Susan Jarvis Committee member Committee member Abstract This text is a treatise on microcontroller programming. It introduces the ma- jor peripherals found on most microcontrollers, including the usage of them, focusing on the ATmega644p in the AVR family produced by Atmel. Gen- eral information and background knowledge on several topics is also presented. These topics include information regarding the hardware of a microcontroller and assembly code as well as instructions regarding good program structure and coding practices. Examples with code and discussion are presented throughout. This is intended for hobbyists and students desiring knowledge on programming microcontrollers, and is written at a level that students entering the junior level core robotics classes would find useful. Contents Preface i 1 What is a Microcontroller? 1 1.1 Micro-processors, -computers, -controllers . .1 1.1.1 Microprocessor . .1 1.1.2 Microcomputer . .2 1.1.3 Microcontroller . .2 1.2 Memory Models . .3 1.2.1 Von Neumann . .3 1.2.2 Harvard Architecture . .4 1.2.3 Modified Harvard Architecture . .5 1.3 The Stack . .6 1.4 Conclusion . .7 2 Datasheets, SFRs and Libraries 9 2.1 Datasheets . .9 2.1.1 Part Name . 10 2.1.2 Description and Operation . 10 2.1.3 Absolute Maximum Ratings . 11 2.1.4 Electrical Characteristics . 12 2.1.5 Physical Characteristics . -

Hard Disk Drive Specifications Models: 2R015H1 & 2R010H1

Hard Disk Drive Specifications Models: 2R015H1 & 2R010H1 P/N:1525/rev. A This publication could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein – which will be incorporated in revised editions of the publication. Maxtor may make changes or improvements in the product(s) described in this publication at any time and without notice. Copyright © 2001 Maxtor Corporation. All rights reserved. Maxtor®, MaxFax® and No Quibble Service® are registered trademarks of Maxtor Corporation. Other brands or products are trademarks or registered trademarks of their respective holders. Corporate Headquarters 510 Cottonwood Drive Milpitas, California 95035 Tel: 408-432-1700 Fax: 408-432-4510 Research and Development Center 2190 Miller Drive Longmont, Colorado 80501 Tel: 303-651-6000 Fax: 303-678-2165 Before You Begin Thank you for your interest in Maxtor hard drives. This manual provides technical information for OEM engineers and systems integrators regarding the installation and use of Maxtor hard drives. Drive repair should be performed only at an authorized repair center. For repair information, contact the Maxtor Customer Service Center at 800- 2MAXTOR or 408-922-2085. Before unpacking the hard drive, please review Sections 1 through 4. CAUTION Maxtor hard drives are precision products. Failure to follow these precautions and guidelines outlined here may lead to product failure, damage and invalidation of all warranties. 1 BEFORE unpacking or handling a drive, take all proper electro-static discharge (ESD) precautions, including personnel and equipment grounding. Stand-alone drives are sensitive to ESD damage. 2 BEFORE removing drives from their packing material, allow them to reach room temperature. -

Flash Memory Guide

Flash Memory Guide Portable Flash memory for computers, digital cameras, mobile phones and other devices Flash Memory Guide Kingston®, the world’s leading independent manufacturer of memory products, offers a broad range of Flash cards, USB Flash drives and Solid-State Drives (SSD) (collectively called Flash storage devices) that employ Flash memory chips for storage. The purpose of this guide is to explain the various technologies and Flash memory offerings that are available. Note: Due to Flash technology changes, specifications listed in this document are subject to change without notice 1.0 Flash Memory: Empowering A New Generation of Flash Storage Devices Toshiba invented Flash memory in the 1980s as a new memory technology that allowed stored data to be saved even when the memory device was disconnected from its power source. Since then, Flash memory technology has evolved into the preferred storage media for a variety of consumer and industrial devices. In consumer devices, Flash memory is widely used in: • Notebook computers • Personal computers • Tablets • Digital cameras • Global Positioning Systems (GPS) • Mobile phones • Solid-state music players such as • Electronic musical instruments MP3 players • Television set-top boxes • Portable and Home Video game consoles Flash memory is also used in many industrial applications where reliability and data retention in power-off situations are key requirements, such as in: • Security systems/IP Cameras • Military systems • Embedded computers • Set-top boxes • Networking and communication products • Wireless communication devices • Retail management products • Point of Sale Devices (e.g., handheld scanners) Please Note: Most Kingston Flash memory is designed and tested for compatibility with consumer devices. -

Using MEMS-Based Storage Devices in Computer Systems

Using MEMS-based storage devices in computer systems STEVEN W. SCHLOSSER May 2004 cmu-pdl-04-104 Dept. of Electrical and Computer Engineering Carnegie Mellon University Pittsburgh, PA 15213 A dissertation submitted to the graduate school in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering. Thesis committee Gregory R. Ganger, Chair L. Richard Carley James C. Hoe Charles C. Morehouse, Hewlett-Packard Laboratories c 2004 Steven W. Schlosser i Keywords: MEMS-based storage, storage systems performance, database sys- tems, disk arrays To my family: my parents, Phil and Kathy; my sister, Jennifer; and my wife, Rachel. Abstract MEMS-based storage is an interesting new technology that promises to bring fast, non-volatile, mass data storage to computer systems. MEMS-based storage de- vices (MEMStores) themselves consist of several thousand read/write tips, anal- ogous to the read/write heads of a disk drive, which read and write data in a recording medium. This medium is coated on a moving rectangular surface that is positioned by a set of MEMS actuators. Access times are expected to be less than a millisecond with energy consumption 10{100× less than a low-power disk drive, while streaming bandwidth and volumetric density are expected to be around that of disk drives. This dissertation explores the use of MEMStores in computer systems, with a focus on whether systems can use existing abstractions and interfaces to incor- porate MEMStores effectively, or if they will have to change the way they access storage to benefit from MEMStores. If systems can use MEMStores in the same way that they use disk drives, it will be more likely that MEMStores will be adopted when they do become available. -

A Robust Low Power Static Random Access Memory Cell Design

Wright State University CORE Scholar Browse all Theses and Dissertations Theses and Dissertations 2018 A Robust Low Power Static Random Access Memory Cell Design A. V. Rama Raju Pusapati Wright State University Follow this and additional works at: https://corescholar.libraries.wright.edu/etd_all Part of the Electrical and Computer Engineering Commons Repository Citation Pusapati, A. V. Rama Raju, "A Robust Low Power Static Random Access Memory Cell Design" (2018). Browse all Theses and Dissertations. 2005. https://corescholar.libraries.wright.edu/etd_all/2005 This Thesis is brought to you for free and open access by the Theses and Dissertations at CORE Scholar. It has been accepted for inclusion in Browse all Theses and Dissertations by an authorized administrator of CORE Scholar. For more information, please contact [email protected]. A ROBUST LOW POWER STATIC RANDOM ACCESS MEMORY CELL DESIGN A Thesis in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering by A.V. RAMA RAJU PUSAPATI B.TECH., JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY, KAKINADA, 2016 2018 Wright State University WRIGHT STATE UNIVERSITY GRADUATE SCHOOL JULY 25, 2018 I HEREBY RECOMMEND THAT THE THESIS PREPARED UNDER MY SUPERVISION BY A.V. Rama Raju Pusapati ENTITLED A Robust Low Power Static Random Access Memory Cell Design BE ACCEPTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF Master of Science in Electrical Engineering. __________________________ Saiyu Ren, Ph.D. Thesis Director __________________________ Brian D. Rigling Ph.D. Chair, Department of Electrical Engineering Committee on Final Examination: ________________________________ Saiyu Ren, Ph.D. ________________________________ Ray Siferd, Ph.D. -

Review on Performance of Static Random Access Memory (SRAM)

ISSN (Online) 2278-1021 ISSN (Print) 2319-5940 International Journal of Advanced Research in Computer and Communication Engineering Vol. 4, Issue 2, February 2015 Review on Performance of Static Random Access Memory (SRAM) Santhiya.V1, Mathan.N2 M.Tech, VLSI Design, Department of ECE, Sathyabama University, Chennai, India1 Assistant professor, Department of ECE, Sathyabama University, Chennai, India2 Abstract: The power consumption is a major concern these days for long operational life. Although various types of techniques to reduce the power dissipation has been developed. One of the most adopted method is to lower the supply voltage. Techniques based on replica circuits which minimize the effect of operating conditions variability on the speed and power. In this paper different static random access memory are designed in order to satisfy low power, high performance circuit and the extensive survey on features of various static random access memory(SRAM) designs were reported. Keywords: SRAM, Delay, speed and area, stability, Power Consumption. I. INTRODUCTION Random-access memory is a form of computer data computers. Dynamic RAM are considered volatile, as it storage. A random-access memory (RAM) device allows lost the information or data when power is removed from data items to be read and written in roughly the same the system. amount of time regardless of the order in which data items II.SRAM OPERATION are accessed[3]. In contrast, with some of the other direct The SRAM cell has three different states such as standby, access data storage media such as hard disks, DVD-RWs reading and writing. To operate in read mode and write and CD-RWs, the time required to read and write data mode SRAM should have “readability and “write items varies significantly depending on their physical stability” respectively. -

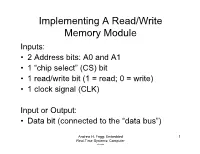

Implementing a Read/Write Memory Module Inputs: • 2 Address Bits: A0 and A1 • 1 “Chip Select” (CS) Bit • 1 Read/Write Bit (1 = Read; 0 = Write) • 1 Clock Signal (CLK)

Implementing A Read/Write Memory Module Inputs: • 2 Address bits: A0 and A1 • 1 “chip select” (CS) bit • 1 read/write bit (1 = read; 0 = write) • 1 clock signal (CLK) Input or Output: • Data bit (connected to the “data bus”) Andrew H. Fagg: Embedded 1 Real-Time Systems: Computer Arch Implementing A Read/Write Memory Module With 2 address bits, how many memory elements can we address? How could we implement each memory element? Andrew H. Fagg: Embedded 2 Real-Time Systems: Computer Arch Implementing A Read/Write Memory Module With 2 address bits, how many memory elements can we address? • 4 1-bit elements How could we implement each memory element? • With a D flip-flop Andrew H. Fagg: Embedded 3 Real-Time Systems: Computer Arch Memory Module Specification When chip select is low: • No memory elements change state • The memory does not drive the data bus Andrew H. Fagg: Embedded 4 Real-Time Systems: Computer Arch Memory Module Specification When chip select is high: • If R/W is high: – Drive the data bus with the value that is stored in the element specified by A1, A0 • If R/W is low: – Store the value that is on the data bus in the element specified by A1, A0 Andrew H. Fagg: Embedded 5 Real-Time Systems: Computer Arch Memory Timing Diagram Q2 A1 A0 R/W CS CLK D Andrew H. Fagg: Embedded 6 Real-Time Systems: Computer Arch Memory Timing Diagram Q2 A1 A0 R/W CS CLK Data bus not driven D Andrew H. Fagg: Embedded 7 Real-Time Systems: Computer Arch Memory Timing Diagram Q2 A1 A0 Memory element 2 is initially in a high state R/W CS CLK D Andrew H. -

Static Random-Access Memory Designs Based on Different Finfets

STATIC RANDOM-ACCESS MEMORY DESIGNS BASED ON DIFFERENT FINFETS AT LOWER TECHNOLOGY NODE (7NM) A THESIS IN Electrical Engineering Presented to the Faculty of the University of Missouri – Kansas City in partial fulfillment of the Requirements for the degree MASTER OF SCIENCE By Athiya Nizam Bachelor of Engineering (B.E.) in Electrical and Electronics Engineering, Osmania University Kansas City, Missouri 2019 ©2019 Athiya Nizam ALL RIGHTS RESERVED STATIC RANDOM-ACCESS MEMORY DESIGNS BASED ON DIFFERENT FINFETS AT LOWER TECHNOLOGY NODE (7NM) Athiya Nizam, Candidate for the Master of Science Degree University of Missouri - Kansas City, 2019 ABSTRACT The Static Random-Access Memory (SRAM) has a significant performance impact on current nanoelectronics systems. To improve SRAM efficiency, it is important to utilize emerging technologies to overcome short-channel effects (SCE) of conventional CMOS. FinFET devices are promising emerging devices that can be utilized to improve the performance of SRAM designs at lower technology nodes. In this thesis, I present detail analysis of SRAM cells using different types of FinFET devices at 7nm technology. From the analysis, it can be concluded that the performance of both 6T and 8T SRAM designs are improved. 6T SRAM achieves a 44.97% improvement in the read energy compared to 8T SRAM. However, 6T SRAM write energy degraded by 3.16% compared to 8T SRAM. Read stability and write ability of SRAM cells are determined using Static Noise Margin and N- curve methods. Moreover, Monte Carlo simulations are performed on the SRAM cells to evaluate process variations. Simulations were done in HSPICE using 7nm Asymmetrical Underlap FinFET technology. -

Lecture Notes on 8085 Microprocessor

LECTURE NOTES ON 8085 MICROPROCESSOR Mr. ASHOK S PATIL CHAPTER: 1 History of microprocessor:- The invention of the transistor in 1947 was a significant development in the world of technology. It could perform the function of a large component used in a computer in the early years. Shockley, Brattain and Bardeen are credited with this invention and were awarded the Nobel prize for the same. Soon it was found that the function this large component was easily performed by a group of transistors arranged on a single platform. This platform, known as the integrated chip (IC), turned out to be a very crucial achievement and brought along a revolution in the use of computers. A person named Jack Kilby of Texas Instruments was honored with the Nobel Prize for the invention of IC, which laid the foundation on which microprocessors were developed. At the same time, Robert Noyce of Fairchild made a parallel development in IC technology for which he was awarded the patent. ICs proved beyond doubt that complex functions could be integrated on a single chip with a highly developed speed and storage capacity. Both Fairchild and Texas Instruments began the manufacture of commercial ICs in 1961. Later, complex developments in the IC led to the addition of more complex functions on a single chip. The stage was set for a single controlling circuit for all the computer functions. Finally, Intel corporation's Ted Hoff and Frederico Fagin were credited with the design of the first microprocessor. The work on this project began with an order from a Japanese calculator company Busicom to Intel, for building some chips for it. -

Microcontroller.Pdf

Basic Microcontroller Use for Measurement and Control Yeyin Shi University of Nebraska- Lincoln, USA Guangjun Qiu South China Agricultural University, China Ning Wang Oklahoma State University, USA https:// doi .org/ 10 .21061/ IntroBiosystemsEngineering/ Microcontroller How to cite this chapter: Shi, Y., Qiu, G., & Wang, N. (2020). Basic Microcontroller Use for Measurement and Control. In Holden, N. M., Wolfe, M. L., Ogejo, J. A., & Cummins, E. J. (Ed.), Introduction to Biosystems Engineering. https:// doi .org/ 10 .21061/ IntroBiosystemsEngineering/ Microcontroller This chapter is part of Introduction to Biosystems Engineering International Standard Book Number (ISBN) (PDF): 978- 1- 949373- 97- 4 International Standard Book Number (ISBN) (Print): 978- 1- 949373- 93- 6 https:// doi .org/ 10 .21061/ IntroBiosystemsEngineering Copyright / license: © The author(s) This work is licensed under a Creative Commons Attribution (CC BY) 4.0 license. https:// creativecommons .org/ licenses/ by/ 4 .0 The work is published jointly by the American Society of Agricultural and Biological Engineers (ASABE) www .asabe .org and Virginia Tech Publishing publishing.vt.edu. Basic Microcontroller Use for Measurement and Control Yeyin Shi Ning Wang Department of Biological Systems Engineering, University of Department of Biosystems and Agricultural Engineering, Nebraska- Lincoln, Lincoln, Nebraska, USA Oklahoma State University, Stillwater, Oklahoma, USA Guangjun Qiu College of Engineering, South China Agricultural University, Guangzhou, Guangdong, China KEY TERMS Architecture and hardware Operating principles Greenhouse control Programming Introduction Measurement and control systems are widely used in biosystems engineering. They are ubiquitous and indispensable in the digital age, being used to collect data (measure) and to automate actions (control). For example, weather stations measure temperature, precipitation, wind, and other environmental parameters.