Transistor-Level Layout of Integrated Circuits

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Transistor Circuit Guidebook Byron Wels TAB BOOKSBLUE RIDGE SUMMIT, PA

TAB BOOKS No. 470 34.95 By Byron Wels TransistorCircuit GuidebookByronWels TABBLUE RIDGE BOOKS SUMMIT,PA. 17214 Preface beforemeIa supposepioneer (along the my withintransistor firstthe many field.experiencewith wasother Weknown. World were using WarUnlike solid-stateIIsolid-state GIs) today's asdevices somewhat experimen- receivers marks of FIRST EDITION devicester,ownFirst, withsemiconductors! youwith a choice swipedwhichor tank. ofto a sealed,Here'sexperiment, pairThen ofhow encapsulated, you earphones we carefullywe did had it: from totookand construct the veryonenearest exoticof our the THIRDSECONDFIRST PRINTING-SEPTEMBER PRINTING-AUGUST PRINTING-JANUARY 1972 1970 1968 plane,wasyouAnphonesantenna. emptywound strung jeep,apart After toiletfull outand ofclippingas paper wire,unwoundhigh closelyrollandthe servedascatchthe far spaced.wire offas as itfrom a thewouldsafetyThe thecoil remaining-pin,magnetreach-for form, you inside.which stuckwire the Copyright © 1968by TAB BOOKS coatedNext,it into youneeded,a hunkribbons of -ofwooda razor -steel, soblade.the but point Oh,aItblued was noneprojected placedblade of the -quenchat so fancy right the pointplastic-bluedangles.of -, Reproduction or publicationPrinted inof the ofAmerica the United content States in any manner, with- themindfoundphoneground pin you,the was couldserved right not wired contact lacquerspotas toa onground blade, it. theblued.blade'sAconnector, pin,bayonet bluing,and stuck antennaand you hilt thecould coil.-deep other actuallyIfin ear- youthe isoutherein. assumed express -

Chapter 7: AC Transistor Amplifiers

Chapter 7: Transistors, part 2 Chapter 7: AC Transistor Amplifiers The transistor amplifiers that we studied in the last chapter have some serious problems for use in AC signals. Their most serious shortcoming is that there is a “dead region” where small signals do not turn on the transistor. So, if your signal is smaller than 0.6 V, or if it is negative, the transistor does not conduct and the amplifier does not work. Design goals for an AC amplifier Before moving on to making a better AC amplifier, let’s define some useful terms. We define the output range to be the range of possible output voltages. We refer to the maximum and minimum output voltages as the rail voltages and the output swing is the difference between the rail voltages. The input range is the range of input voltages that produce outputs which are not at either rail voltage. Our goal in designing an AC amplifier is to get an input range and output range which is symmetric around zero and ensure that there is not a dead region. To do this we need make sure that the transistor is in conduction for all of our input range. How does this work? We do it by adding an offset voltage to the input to make sure the voltage presented to the transistor’s base with no input signal, the resting or quiescent voltage , is well above ground. In lab 6, the function generator provided the offset, in this chapter we will show how to design an amplifier which provides its own offset. -

Electronic Circuit Design and Component Selecjon

Electronic circuit design and component selec2on Nan-Wei Gong MIT Media Lab MAS.S63: Design for DIY Manufacturing Goal for today’s lecture • How to pick up components for your project • Rule of thumb for PCB design • SuggesMons for PCB layout and manufacturing • Soldering and de-soldering basics • Small - medium quanMty electronics project producMon • Homework : Design a PCB for your project with a BOM (bill of materials) and esMmate the cost for making 10 | 50 |100 (PCB manufacturing + assembly + components) Design Process Component Test Circuit Selec2on PCB Design Component PCB Placement Manufacturing Design Process Module Test Circuit Selec2on PCB Design Component PCB Placement Manufacturing Design Process • Test circuit – bread boarding/ buy development tools (breakout boards) / simulaon • Component Selecon– spec / size / availability (inventory! Need 10% more parts for pick and place machine) • PCB Design– power/ground, signal traces, trace width, test points / extra via, pads / mount holes, big before small • PCB Manufacturing – price-Mme trade-off/ • Place Components – first step (check power/ground) -- work flow Test Circuit Construc2on Breadboard + through hole components + Breakout boards Breakout boards, surcoards + hookup wires Surcoard : surface-mount to through hole Dual in-line (DIP) packaging hap://www.beldynsys.com/cc521.htm Source : hap://en.wikipedia.org/wiki/File:Breadboard_counter.jpg Development Boards – good reference for circuit design and component selec2on SomeMmes, it can be cheaper to pair your design with a development -

Integrated Circuits

CHAPTER67 Learning Objectives ➣ What is an Integrated Circuit ? ➣ Advantages of ICs INTEGRATED ➣ Drawbacks of ICs ➣ Scale of Integration CIRCUITS ➣ Classification of ICs by Structure ➣ Comparison between Different ICs ➣ Classification of ICs by Function ➣ Linear Integrated Circuits (LICs) ➣ Manufacturer’s Designation of LICs ➣ Digital Integrated Circuits ➣ IC Terminology ➣ Semiconductors Used in Fabrication of ICs and Devices ➣ How ICs are Made? ➣ Material Preparation ➣ Crystal Growing and Wafer Preparation ➣ Wafer Fabrication ➣ Oxidation ➣ Etching ➣ Diffusion ➣ Ion Implantation ➣ Photomask Generation ➣ Photolithography ➣ Epitaxy Jack Kilby would justly be considered one of ➣ Metallization and Intercon- the greatest electrical engineers of all time nections for one invention; the monolithic integrated ➣ Testing, Bonding and circuit, or microchip. He went on to develop Packaging the first industrial, commercial and military ➣ Semiconductor Devices and applications for this integrated circuits- Integrated Circuit Formation including the first pocket calculator ➣ Popular Applications of ICs (pocketronic) and computer that used them 2472 Electrical Technology 67.1. Introduction Electronic circuitry has undergone tremendous changes since the invention of a triode by Lee De Forest in 1907. In those days, the active components (like triode) and passive components (like resistors, inductors and capacitors etc.) of the circuits were separate and distinct units connected by soldered leads. With the invention of the transistor in 1948 by W.H. Brattain and I. Bardeen, the electronic circuits became considerably reduced in size. It was due to the fact that a transistor was not only cheaper, more reliable and less power consuming but was also much smaller in size than an electron tube. To take advantage of small transistor size, the passive components too were greatly reduced in size thereby making the entire circuit very small. -

35402 Electronic Circuit R TG

Electricity and Electronics Electronic Circuit Repair Introduction The purpose of this video is to help you quickly learn the most common methods used to trou- bleshoot electronic circuits. Electronic troubleshooting skills are needed to diagnose and repair several types of devices. These devices include stereos, cameras, VCRs, and much more. As mentioned, the program will explain how to diagnose and repair different types of electronic com- ponents and circuits. Viewers will also learn how to use the specialized tools and instruments needed to test these particular types of circuits and components. If students plan to enter any type of electronics field, viewing this program will prove to be beneficial. The program is organized into major sections or topics. Each section covers one major segment of the subject. Graphic breaks are given between each section so that you can stop the video for class discussion, demonstrations, to answer questions, or to ask questions. This allows you to watch only a portion of the program each day, or to present it in its entirety. This program is part of the ten-part series Electricity and Electronics, which includes the following titles: • Electrical Principles • Electrical Circuits: Ohm's Law • Electrical Components Part I: Resistors/Batteries/Switches • Electrical Components Part II: Capacitors/Fuses/Flashers/Coils • Electrical Components Part III: Transformers/Relays/Motors • Electronic Components Part I: Semiconductors/Transistors/Diodes • Electronic Components Part II: Operation—Transistors/Diodes • Electronic Components Part III: Thyristors/Piezo Crystals/Solar Cells/Fiber Optics • Electrical Troubleshooting • Electronic Circuit Repair To order additional titles please see Additional Resources at www.filmsmediagroup.com at the end of this guide. -

Capacitors and Inductors

DC Principles Study Unit Capacitors and Inductors By Robert Cecci In this text, you’ll learn about how capacitors and inductors operate in DC circuits. As an industrial electrician or elec- tronics technician, you’ll be likely to encounter capacitors and inductors in your everyday work. Capacitors and induc- tors are used in many types of industrial power supplies, Preview Preview motor drive systems, and on most industrial electronics printed circuit boards. When you complete this study unit, you’ll be able to • Explain how a capacitor holds a charge • Describe common types of capacitors • Identify capacitor ratings • Calculate the total capacitance of a circuit containing capacitors connected in series or in parallel • Calculate the time constant of a resistance-capacitance (RC) circuit • Explain how inductors are constructed and describe their rating system • Describe how an inductor can regulate the flow of cur- rent in a DC circuit • Calculate the total inductance of a circuit containing inductors connected in series or parallel • Calculate the time constant of a resistance-inductance (RL) circuit Electronics Workbench is a registered trademark, property of Interactive Image Technologies Ltd. and used with permission. You’ll see the symbol shown above at several locations throughout this study unit. This symbol is the logo of Electronics Workbench, a computer-simulated electronics laboratory. The appearance of this symbol in the text mar- gin signals that there’s an Electronics Workbench lab experiment associated with that section of the text. If your program includes Elec tronics Workbench as a part of your iii learning experience, you’ll receive an experiment lab book that describes your Electronics Workbench assignments. -

Basic DC Motor Circuits

Basic DC Motor Circuits Living with the Lab Gerald Recktenwald Portland State University [email protected] DC Motor Learning Objectives • Explain the role of a snubber diode • Describe how PWM controls DC motor speed • Implement a transistor circuit and Arduino program for PWM control of the DC motor • Use a potentiometer as input to a program that controls fan speed LWTL: DC Motor 2 What is a snubber diode and why should I care? Simplest DC Motor Circuit Connect the motor to a DC power supply Switch open Switch closed +5V +5V I LWTL: DC Motor 4 Current continues after switch is opened Opening the switch does not immediately stop current in the motor windings. +5V – Inductive behavior of the I motor causes current to + continue to flow when the switch is opened suddenly. Charge builds up on what was the negative terminal of the motor. LWTL: DC Motor 5 Reverse current Charge build-up can cause damage +5V Reverse current surge – through the voltage supply I + Arc across the switch and discharge to ground LWTL: DC Motor 6 Motor Model Simple model of a DC motor: ❖ Windings have inductance and resistance ❖ Inductor stores electrical energy in the windings ❖ We need to provide a way to safely dissipate electrical energy when the switch is opened +5V +5V I LWTL: DC Motor 7 Flyback diode or snubber diode Adding a diode in parallel with the motor provides a path for dissipation of stored energy when the switch is opened +5V – The flyback diode allows charge to dissipate + without arcing across the switch, or without flowing back to ground through the +5V voltage supply. -

United States Patent (19) 11

United States Patent (19) 11. Patent Number: 4,503,479 Otsuka et al. 45 Date of Patent: Mar. 5, 1985 54 ELECTRONIC CIRCUIT FOR VEHICLES, 4,244,050 1/1981 Weber et al. .............. 364/431.11 X HAVING A FAIL SAFE FUNCTION FOR 4,245,150 1/1981 Driscoll et al. ................... 361/92 X ABNORMALITY IN SUPPLY VOLTAGE 4,306,270 12/1981 Miller et al. ...... ... 361/90 X 4,327,397 4/1982 McCleery ............................. 361/90 75) Inventors: Kazuo Otsuka, Higashikurume; Shin 4,348,727 9/1982 Kobayashi et al.............. 123/480 X Narasaka, Yono; Shumpei Hasegawa, Niiza, all of Japan OTHER PUBLICATIONS 73 Assignee: Honda Motor Co., Ltd., Tokyo, #18414, Res. Disclosure, Great Britain, No. 184, Aug. Japan 1979. Electronic Design; "Simple Circuit Checks Power-S- 21 Appl. No.: 528,236 upply Faults'; Lindberg, pp. 57-63, Aug. 2, 1980. (22 Filed: Aug. 31, 1983 Primary Examiner-Reinhard J. Eisenzopf Attorney, Agent, or Firm-Arthur L. Lessler Related U.S. Application Data (57) ABSTRACT 63 Continuation of Ser. No. 297,998, Aug. 31, 1981, aban doned. An electronic circuit for use in a vehicle equipped with an internal combustion engine. The electronic circuit (30) Foreign Application Priority Data comprises a constant-voltage regulated power-supply Sep. 4, 1980 (JP) Japan ................................ 55.122594 circuit, a control circuit having a central processing unit 51) Int. Cl. ......................... H02H 3/20; HO2H 3/24 for controlling electrical apparatus installed in the vehi 52 U.S. Cl. ...................................... 361/90; 123/480; cle, and a detecting circuit for detecting variations in 340/661; 364/431.11 supply voltage supplied from the power-supply circuit. -

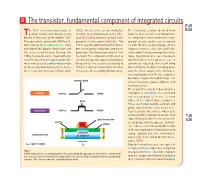

The Transistor, Fundamental Component of Integrated Circuits

D The transistor, fundamental component of integrated circuits he first transistor was made in (SiO2), which serves as an insulator. The transistor, a name derived from Tgermanium by John Bardeen and In 1958, Jack Kilby invented the inte- transfer and resistor, is a fundamen- Walter H. Brattain, in December 1947. grated circuit by manufacturing 5 com- tal component of microelectronic inte- The year after, along with William B. ponents on the same substrate. The grated circuits, and is set to remain Shockley at Bell Laboratories, they 1970s saw the advent of the first micro- so with the necessary changes at the developed the bipolar transistor and processor, produced by Intel and incor- nanoelectronics scale: also well-sui- the associated theory. During the porating 2,250 transistors, and the first ted to amplification, among other func- 1950s, transistors were made with sili- memory. The complexity of integrated tions, it performs one essential basic con (Si), which to this day remains the circuits has grown exponentially (dou- function which is to open or close a most widely-used semiconductor due bling every 2 to 3 years according to current as required, like a switching to the exceptional quality of the inter- “Moore's law”) as transistors continue device (Figure). Its basic working prin- face created by silicon and silicon oxide to become increasingly miniaturized. ciple therefore applies directly to pro- cessing binary code (0, the current is blocked, 1 it goes through) in logic cir- control gate cuits (inverters, gates, adders, and memory cells). The transistor, which is based on the switch source drain transport of electrons in a solid and not in a vacuum, as in the electron gate tubes of the old triodes, comprises three electrodes (anode, cathode and gate), two of which serve as an elec- transistor source drain tron reservoir: the source, which acts as the emitter filament of an electron gate insulator tube, the drain, which acts as the col- source lector plate, with the gate as “control- gate drain ler”. -

Fundamentals of MOSFET and IGBT Gate Driver Circuits

Application Report SLUA618A–March 2017–Revised October 2018 Fundamentals of MOSFET and IGBT Gate Driver Circuits Laszlo Balogh ABSTRACT The main purpose of this application report is to demonstrate a systematic approach to design high performance gate drive circuits for high speed switching applications. It is an informative collection of topics offering a “one-stop-shopping” to solve the most common design challenges. Therefore, it should be of interest to power electronics engineers at all levels of experience. The most popular circuit solutions and their performance are analyzed, including the effect of parasitic components, transient and extreme operating conditions. The discussion builds from simple to more complex problems starting with an overview of MOSFET technology and switching operation. Design procedure for ground referenced and high side gate drive circuits, AC coupled and transformer isolated solutions are described in great details. A special section deals with the gate drive requirements of the MOSFETs in synchronous rectifier applications. For more information, see the Overview for MOSFET and IGBT Gate Drivers product page. Several, step-by-step numerical design examples complement the application report. This document is also available in Chinese: MOSFET 和 IGBT 栅极驱动器电路的基本原理 Contents 1 Introduction ................................................................................................................... 2 2 MOSFET Technology ...................................................................................................... -

Power MOSFET Basics by Vrej Barkhordarian, International Rectifier, El Segundo, Ca

Power MOSFET Basics By Vrej Barkhordarian, International Rectifier, El Segundo, Ca. Breakdown Voltage......................................... 5 On-resistance.................................................. 6 Transconductance............................................ 6 Threshold Voltage........................................... 7 Diode Forward Voltage.................................. 7 Power Dissipation........................................... 7 Dynamic Characteristics................................ 8 Gate Charge.................................................... 10 dV/dt Capability............................................... 11 www.irf.com Power MOSFET Basics Vrej Barkhordarian, International Rectifier, El Segundo, Ca. Discrete power MOSFETs Source Field Gate Gate Drain employ semiconductor Contact Oxide Oxide Metallization Contact processing techniques that are similar to those of today's VLSI circuits, although the device geometry, voltage and current n* Drain levels are significantly different n* Source t from the design used in VLSI ox devices. The metal oxide semiconductor field effect p-Substrate transistor (MOSFET) is based on the original field-effect Channel l transistor introduced in the 70s. Figure 1 shows the device schematic, transfer (a) characteristics and device symbol for a MOSFET. The ID invention of the power MOSFET was partly driven by the limitations of bipolar power junction transistors (BJTs) which, until recently, was the device of choice in power electronics applications. 0 0 V V Although it is not possible to T GS define absolutely the operating (b) boundaries of a power device, we will loosely refer to the I power device as any device D that can switch at least 1A. D The bipolar power transistor is a current controlled device. A SB (Channel or Substrate) large base drive current as G high as one-fifth of the collector current is required to S keep the device in the ON (c) state. Figure 1. Power MOSFET (a) Schematic, (b) Transfer Characteristics, (c) Also, higher reverse base drive Device Symbol. -

Chapter 4: the MOS Transistor

Chapter 4: the MOS transistor 1. Introduction First products in Complementary Metal Oxide Silicon (CMOS) technology appeared in the market in seventies. At the beginning, CMOS devices were reserved for logic, as they offer the highest density (in gates/mm2), and the lowest static power consumption. Most high‐frequency circuitry was carried out in bipolar technology. As a result, a lot of analog functions were realized in bipolar technology. The technology development, which is driven by digital circuits (in particular by flash memories), lead to smaller and faster CMOS devices. At the beginning of the seventies, 1µm transistors length was considered short. Currently, CMOS technology with 22nm channel length is available. In the last twenty years a lot of analog circuits started to be developed in CMOS technology. In fact, the technology scaling enabled CMOS devices at higher frequencies of working, also for the analog counterpart. Today, CMOS and bipolar technologies are in competition over a wide frequency region up to 100GHz. The challenge indeed, to choice the technology that fulfills best the system and circuit requirements at a reasonable cost. Bipolar is more expensive than standard CMOS technology. Moreover, most systems and circuits are mixed signal, i.e. they include digital and analog parts. In the past, separated integrated circuits were dedicated to the analog (bipolar) and digital (CMOS) circuits. As analog circuits were also available in CMOS technology, this technology started to offer the opportunity to integrate cheap, high density and low power digital circuits, as well as analog circuits, in the same chip. This brings enormous advantages in terms of reduced costs and smaller form factors of electronic devices.