Pin Information for the Intel® Agilex™ AGFB022 Device

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

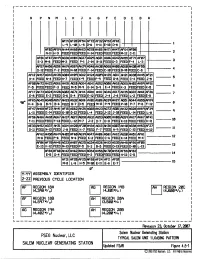

Salem Generating Station, Units 1 & 2, Revision 29 to Updated Final Safety Analysis Report, Chapter 4, Figures 4.5-1 to 4.5

r------------------------------------------- 1 I p M J B I R N L K H G F E D c A I I I I I Af'Jq AF20 AF54 AF72 32 AF52 AF18 I L-q L-10 L-15 D-6 -11 E-10 D-8 l I AF03 Af't;qAH44 AH60 AH63 AG70 AH65 AH7l AH47 AFS4 AF08 I N-ll H-3 FEED FEED FEED H-14 FEED FEED FEED M-12 C-11 2 I AF67 AH4q AH04 AG27 AG2<i' AG21 AG16 AG42 AF71 AF07 AF01 AG36 AH!5!5 3 I E-3 M-6 FEED M-3 FEED P-1 J-14 B-11 FEED D-3 FEED F-4 L-3 I AF67 AH5S AG56 Atflq AGsq AH2<1' AG48 AH30 AG68 AH08 AG60 AH30 AF55 I D-12 FEED F-2 FEED N-11 FEED F-14 FEED C-11 FEED B-11 FEED C-8 4 I AF12 AH57 AG43 AH38 AHtiJq AG12 AH24 AGfR AH25 AGil AG31 AH45 AF21 AGlM AH21 5 I H~4 FEED N-4 FEED H-7 FEED K~q FEED F-q FEED G-8 FEED C-4 FEED J-15 I AF50 AH72 AH22 AGS6 AH15 AGll.lAG64 AG41 AG52 AG88 AH18 AG65 AHIJ2 AH5q AF51 I F-5 FEED FEED F-3 FEED M-5 r+q G-14 o-q E-4 FEED K-3 FEED FEED K-5 6 I f:Fl7 AH73 AG24 AH28 AG82 AG71 AH14 AG18 AHil AG46 AG17 AH35 AG22 AH61 AF26 7 I E-8 FEED E-2 FEED G-6 G-4 FEED E-12 FEED J-4 J-6 FEED L-2 FEED E-5 I Af&q I qeo AF65 AG45 AtM0 AG57 AH33 AG32 AG16 AH01 AGI6 AG3<1' AH27 AG51 AG44 AG55 K-4 B-8 e-q B-6 FEED B-7 P-5 FEEC M-11 P-q FEED P-11 P-7 P-8 F-12 8 I AF47 AH68 AF23 AH41 AF1!5 AG62 AH26 AG03 AH23 AH32 AG28 AHsq AF3<1' q I L-U FEED E-14 FEED G-10 G-12 FEED L-4 FEED FEED L-14 FEED L-8 I ~~ AF66 AH66 AH10 AG67 AH37 AGJq AG68 AG3l AG63 AG05 AH08 AG5q AH17 AH67 AF41 I F-11 FEED FEED F-13 FEED L-12 M-7 J-2 D-7 D-11 FEED K-13 FEED FEED K-11 10 I AE33 AH!52 AG37 AH31 AG14 AH20 AF20 AH34 AG13 AH36 AG07 AH40 AG38 AH!53 AF27 I G-ll FEED N-12 FEED J-8 FEED K-7 FEED -

Dating of Remains of Neanderthals and Homo Sapiens from Anatolian Region by ESR-US Combined Methods: Preliminary Results

INTERNATIONAL JOURNAL OF SCIENTIFIC & TECHNOLOGY RESEARCH VOLUME 5, ISSUE 05, MAY 2016 ISSN 2277-8616 Dating Of Remains Of Neanderthals And Homo Sapiens From Anatolian Region By ESR-US Combined Methods: Preliminary Results Samer Farkh, Abdallah Zaiour, Ahmad Chamseddine, Zeinab Matar, Samir Farkh, Jamal Charara, Ghayas Lakis, Bilal Houshaymi, Alaa Hamze, Sabine Azoury Abstract: We tried in the present study to apply the electron spin resonance method (ESR) combined with uranium-series method (US), for dating fossilized human teeth and found valuable archaeological sites such as Karain Cave in Anatolia. Karain Cave is a crucial site in a region that has yielded remains of Neanderthals and Homo sapiens, our direct ancestors. The dating of these remains allowed us to trace the history, since the presence of man on earth. Indeed, Anatolia in Turkey is an important region of the world because it represents a passage between Africa, the Middle East and Europe. Our study was conducted on faunal teeth found near human remains. The combination of ESR and US data on the teeth provides an understanding of their complex geochemical evolution and get better estimated results. Our samples were taken from the central cutting where geological layers are divided into archaeological horizons each 10 cm. The AH4 horizon of I.3 layer, which represents the boundary between the Middle Paleolithic and Upper Paleolithic, is dated to 29 ± 4 ka by the ESR-US model. Below, two horizons AH6 and AH8 in the same layer I.4 are dated respectively 40 ± 6 and 45 ± 7 ka using the ESR-US model. -

1St IRF Asia Regional Congress & Exhibition

1st IRF Asia Regional Congress & Exhibition Bali, Indonesia November 17–19 , 2014 For Professionals. By Professionals. "Building the Trans-Asia Highway" Bali’s Mandara toll road Executive Summary International Road Federation Better Roads. Better World. 1 International Road Federation | Washington, D.C. ogether with the Ministry of Public Works Indonesia, we chose the theme “Building the Trans-Asia Highway” to bring new emphasis to a visionary project Tthat traces its roots back to 1959. This Congress brought the region’s stakeholders together to identify new and innovative resources to bridge the current financing gap, while also sharing case studies, best practices and new technologies that can all contribute to making the Trans-Asia Highway a reality. This Congress was a direct result of the IRF’s strategic vision to become the world’s leading industry knowledge platform to help countries everywhere progress towards safer, cleaner, more resilient and better connected transportation systems. The Congress was also a reflection of Indonesia’s rising global stature. Already the largest economy in Southeast Asia, Indonesia aims to be one of world’s leading economies, an achievement that will require the continued development of not just its own transportation network, but also that of its neighbors. Thank you for joining us in Bali for this landmark regional event. H.E. Eng. Abdullah A. Al-Mogbel IRF Chairman Minister of Transport, Kingdom of Saudi Arabia Indonesia Hosts the Region’s Premier Transportation Meeting Indonesia was the proud host to the 1st IRF Asia Regional Congress & Exhibition, a regional gathering of more than 700 transportation professionals from 52 countries — including Ministers, senior national and local government officials, academics, civil society organizations and industry leaders. -

Asian Highway Handbook United Nations

ECONOMIC AND SOCIAL COMMISSION FOR ASIA AND THE PACIFIC ASIAN HIGHWAY HANDBOOK UNITED NATIONS New York, 2003 ST/ESCAP/2303 The Asian Highway Handbook was prepared under the direction of the Transport and Tourism Division of the United Nations Economic and Social Commission for Asia and the Pacific. The team of staff members of the Transport and Tourism Division who prepared the Handbook comprised: Fuyo Jenny Yamamoto, Tetsuo Miyairi, Madan B. Regmi, John R. Moon and Barry Cable. Inputs for the tourism- related parts were provided by an external consultant: Imtiaz Muqbil. The designations employed and the presentation of the material in this publication do not imply the expression of any opinion whatsoever on the part of the Secretariat of the United Nations concerning the legal status of any country, territory, city or area or of its authorities, or concerning the delimitation of its frontiers or boundaries. This publication has been issued without formal editing. CONTENTS I. INTRODUCTION TO THE ASIAN HIGHWAY………………. 1 1. Concept of the Asian Highway Network……………………………… 1 2. Identifying the Network………………………………………………. 2 3. Current status of the Asian Highway………………………………….. 3 4. Formalization of the Asian Highway Network……………………….. 7 5. Promotion of the Asian Highway……………………………………... 9 6. A Vision of the Future………………………………………………… 10 II. ASIAN HIGHWAY ROUTES IN MEMBER COUNTRIES…... 16 1. Afghanistan……………………………………………………………. 16 2. Armenia……………………………………………………………….. 19 3. Azerbaijan……………………………………………………………... 21 4. Bangladesh……………………………………………………………. 23 5. Bhutan…………………………………………………………………. 27 6. Cambodia……………………………………………………………… 29 7. China…………………………………………………………………... 32 8. Democratic People’s Republic of Korea……………………………… 36 9. Georgia………………………………………………………………... 38 10. India…………………………………………………………………… 41 11. Indonesia………………………………………………………………. 45 12. Islamic Republic of Iran………………………………………………. 49 13 Japan………………………………………………………………….. -

International Society for Soil Mechanics and Geotechnical Engineering

INTERNATIONAL SOCIETY FOR SOIL MECHANICS AND GEOTECHNICAL ENGINEERING This paper was downloaded from the Online Library of the International Society for Soil Mechanics and Geotechnical Engineering (ISSMGE). The library is available here: https://www.issmge.org/publications/online-library This is an open-access database that archives thousands of papers published under the Auspices of the ISSMGE and maintained by the Innovation and Development Committee of ISSMGE. Dynamic centrifuge model test for performance-based design of grid-form deep mixing walls supporting a tall building Junji Hamada & Tsuyoshi Honda Takenaka Research & Development Institute, Takenaka Corporation, Inzai, Chiba, Japan ABSTRACT Dynamic centrifuge model tests in the 50 g field were conducted to investigate a failure behavior of DMWs in liquefiable sand during large earthquakes. A miniature model of DMWs was made of soil-cement with an unconfined compressive strength of about 4,000 kPa in order to investigate the behavior/toughness of the DMWs after yield and failure on seismic performance. The DMWs model that support the superstructure’s weight of 206 kPa, the natural period of 0.6 second were set in a laminar shear box, and repeatedly tested by increasing the acceleration level of the input motion recorded at TAFT earthquakes. The relationship between shear stress and shear strain of the DMWs, namely the nonlinearity of the DMWs was investigated. No significant settlement of the structure was observed even if the normal and shear stresses in the DMWs were assumed to have locally reached the tensile or shear criteria of soil-cement. 1 INTRODUCTION potential for liquefaction mitigation. However, the local failures of the DMWs are not acceptable in the existing Grid-form DMWs (Deep cement Mixing Walls) which is method of allowable stress design. -

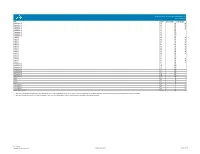

Covers Cable Tray Straight Cover Number Selection

Aluminum Covers Cable Tray Straight Cover Number Selection Tray Covers — Tray covers are available for all classes of tray. They should be installed where falling objects may damage cables or where vertical tray run is accessible by pedestrian or vehicular traffic. Cover mounting hardware must be ordered separately. Solid Covers — These covers provide maximum mechanical protection for cables with limited heat build up. Solid covers are available with or without flange. Flanged covers have 1/2” flange. Cover mounting hardware must be ordered separately. Ventilated Flanged Covers — This design offers excellent mechanical protection while allowing heat produced by cables to dissipate. Cover mounting hardware must be ordered separately. Peaked Flanged Covers — Peaked covers offer mechanical protection reduce pooling of liquids on the cover and accumulation of snow or ice. Peaked covers have 15° rise. Covers greater than 12" wide available in 72" and 3m lengths only. Cover mounting hardware must be ordered separately. T&B aluminum cable tray is composed of two distinct systems H-Style and U-Style. These systems are interchangeable. 100 Aluminum Covers Straight Cover Number Selection Cable Tray Straight Cover Number Selection (ABW-1-12)-SNC-72 Material Cover Series Width Cover Type Length ABW • Aluminum 1 • For tray series: AH04, AH14 06 • (6") SNC • Solid Non-Flanged Cover 72 • (72”) Accessory 2 • For tray series: AH06, AH24, AH34, AH44, 09 • (9") AH54, AH25, AH35, AH45, AH16, AH26 12 • (12") SFC • Solid Flanged Cover 144 • (12ft) 3 • For tray series: AH36, AH46, AH56, AH66 18 • (18") VFC • Ventilated Flanged Cover 3 • (3 m) AH27, AH2C7, AH37 24 • (24") 30 • (30") *PFC • Peaked Flanged Cover 36 • (36") * Peaked covers greater than 12” wide available in 72” and 3m lengths only. -

Congressional Record United States Th of America PROCEEDINGS and DEBATES of the 105 CONGRESS, FIRST SESSION

E PL UR UM IB N U U S Congressional Record United States th of America PROCEEDINGS AND DEBATES OF THE 105 CONGRESS, FIRST SESSION Vol. 143 WASHINGTON, TUESDAY, JANUARY 7, 1997 No. 1 House of Representatives This being the day fixed by the 20th The CLERK. Representatives-elect, Hunter Miller Sanchez Kim Packard Sherman amendment of the Constitution of the this is the day fixed by the 20th amend- Lantos Pelosi Stark United States, and Public Law 104±296 ment to the Constitution and Public Lewis Pombo Tauscher for the meeting of the Congress of the Law 104±296 for the meeting of the 105th Lofgren Radanovich Thomas United States, the Members-elect of Congress and, as the law directs, the Martinez Riggs Torres Matsui Rogan Waters the 105th Congress met in their Hall, Clerk of the House has prepared the of- McKeon Rohrabacher Waxman and at 12 noon were called to order by ficial roll of the Representatives-elect. Millender- Roybal-Allard Woolsey the Clerk of the House of Representa- Certificates of election covering 435 McDonald Royce tives, Hon. Robin H. Carle. seats in the 105th Congress have been COLORADO The Chaplain, Rev. James David received by the Clerk of the House, and Ford, D.D., offered the following pray- DeGette McInnis Schaffer the names of those persons whose cre- Hefley Schaefer Skaggs er: dentials show that they were regularly Oh, gracious God, from whom we CONNECTICUT elected as Representatives in accord- have come and to whom we belong, we ance with the laws of their respective DeLauro Johnson Maloney offer this prayer of thanksgiving and Gejdenson Kennelly Shays States or of the United States will be gratitude for all the blessings You have called. -

Auction 14A Final Draft.Vp

OUR STAFF Stephen Album Paul Montz Director of Islamic & Early Indian Numismatics Director of World Coins Steve has been serving the Paul joined the staff in January numismatic community since 2011. He attended UC Davis 1960. In 1976 he began dealing from 1975-80, earning bachelor's nearly exclusively in Islamic and and master's degrees in Indian coins. He has authored Agricultural Science & several books including the Management and Agronomy, Catalogue of California Trade respectively. He began working Tokens, Volumes I & II in 1972 in the numismatic field in the and 1974 respectively. 1977 saw 1970's. In 1981, he founded the release of his complete rewrite of Marsden's Olde World Numismatics in Chico, CA, a business he Numismata Orientalia Illustrata, a guide to Islamic ran for 30 years, focusing on A-Z world coins, before and Oriental coins with values. In 1993 he published merging with Stephen Album Rare Coins. He has put A Checklist of Islamic Coins, which now in its second out price lists for many years and has been a fixture edition is the standard for collectors of Islamic coins. at major shows since the 1980's. Paul is a life Mr. Album is currently a senior fellow at the member of the American Numismatic Association Worcester College, Oxford, England, and in this and is a member of other organizations. He has been position has authored three of the ten volumes of the a contributing editor for the Standard Catalog of Sylloge of Islamic Coins in the Ashmolean (Museum) World Coins since 1998. Paul brings experience in beginning in 1999. -

Growing Together Articulates a Number of Proposals That Can Help the Region Exploit Its Huge Untapped Potential for Regional Economic Integration

i Photo by Warren Field ii FOREWORD For the global economy, these are difficult times. The world is emerging from a crisis whose aftershocks continue to resonate – trapping some of the richest economies in recession and shaking the foundations of one of the world’s major currencies. Here at ESCAP, there are historical echoes. What is now the Economic and Social Commission for Asia and the Pacific was founded more than 60 years ago – also in the aftermath of a global crisis. The countries of Asia and the Pacific established their new Commission partly to assist them in rebuilding their economies as they came out of the yoke of colonialism and the Second World War. The newly established ECAFE, as ESCAP was called then, held a ministerial conference on regional economic cooperation in 1963 that resolved to set up the Asian Development Bank with the aim of assisting the countries in the region in rebuilding their economies. Fifty years later, the Asia-Pacific region is again at a crossroads, on this occasion seeking ways and means to sustain its dynamism in a dramatically changed global context in the aftermath of a global financial and economic crisis. An important change is the fact that, burdened by huge debts and global imbalances, the advanced economies of the West are no longer able to play the role of engines of growth for the Asia-Pacific region that they played in the past. Hence, the Asia-Pacific region has to look for new engines of growth. The secretariat of ESCAP has argued over the past few years that regional developmental challenges, such as poverty and wide disparities in social and physical infrastructure, can be turned into opportunities for sustaining growth in the future. -

1 EAPRS SCORING CODEBOOK Full P1

1 EAPRS SCORING CODEBOOK Full p1, Abbreviated p45, Mini p57 Full scoring Section A1-6 – Paved trails Item Description Scoring Aa13 Trail condition 1=poor 2=fair 3=excellent Aa15 Trail cleanliness 1=not at all 2=somewhat 3=mostly to extremely Saa11 Trail presence 0=no 1=yes Saa62 Trail length, trichotomized and weighted 1= 0-0.5 miles 3=0.6-1 mile 5=1.1-highest Aa14 Trail width 1=<2ft 2=2-5ft 3=>5ft Aa16 Trail flatness 1=significant incline/decline 2=some incline/decline 3=completely flat Aa17 Trail continuity 0=no 1=yes Aa18 Trail clear from obstruction 1=not at all 2=somewhat 3=mostly to extremely Aa19 Trail coverage/shade 1=poor 2=fair 3=excellent Aa110 Trail dividing-line stripe 0=no 1=yes Scorea1, paved Max score 44. Condition and cleanliness multiplied by length, then summed with trail existence width, flatness, continuity, clear, coverage, dividing line. and surface scoresa1=sum(((aa13+aa15)*(saa11*saa62),aa14,aa16,aa17,aa18,aa19,aa110) Aa22 Signage visibility 1=not at all 2=somewhat 2 3=mostly to extremely Aa23 Signage condition 1=poor 2=fair 3=excellent Aa24 Signage content - uses 0=no 1=yes Aa25 Signage content – warnings 0=no 1=yes Aa26 Signage content – distances 0=no 1=yes Aa27 Signage content – trail name 0=no 1=yes Aa28 Signage colorful 0=no 1=yes Aa29 Signage trail map 0=no 1=yes Aa210 Signage distance markings 0=no 1=yes Aa211 Signage convergence 0=no 1=yes Scorea2, paved Sum of above items. -

South Asia Subregional Economic Cooperation Tourism Development Plan

ASIAN DEVELOPMENT BANK AND SOUTH ASIA SUBREGIONAL ECONOMIC COOPERATION TOURISM WORKING GROUP TOURISM RESOURCE CONSULTANTS LTD, NEW ZEALAND IN ASSOCIATION WITH METCON CONSULTANTS PTE LTD, NEPAL December 2004 SOUTH ASIA SUBREGIONAL ECONOMIC COOPERATION Photo Credits: Les Clark Lisa Choegyal Department of Tourism, Bhutan Department of Tourism, India Nepal Tourism Board © 2005 Asian Development Bank All rights reserved. This book was prepared by staff and consultants of the Asian Development Bank (ADB). The analyses and assessments contained herein do not necessarily reflect the views of the Asian Dvelopment Bank, or its Board of Directors, or the governments its members represent. ADB does not guarantee the accuracy of the data included in this publication and accepts no responsibility for any consequences of their use. The term “country,” as used in the context of ADB, refers to a member of ADB and does not imply any view on the part of ADB as to the member’s sovereignty or independent status. Asian Development Bank 6 ADB Avenue, Mandaluyong City 1550 Metro Manila, Philippines Tel (63-2) 632-4444 Fax (63-2) 636-2444 www.adb.org Asian Development Bank. 2004. South Asia Subregional Economic Cooperation Tourism Development Plan Publication Stock No. 111304 ii ABBREVIATIONS ABBREVIATIONS ABTO — Association of Bhutan Tour Operators ACAP — Annapurna Conservation Area Project ADF — Asian Development Fund ACT — Association for Conservation and Tourism ADB — Asian Development Bank ASEAN — Association of South East Asian Nations APETIT — Asia Pacific -

Pin Information for the Intel® Stratix®10 1SM16B Device Version: 2020-12-22

Pin Information for the Intel® Stratix®10 1SM16B Device Version: 2020-12-22 TYPE BANK UF53 Package UF55 Package Transceiver I/O 1C 28 28 Transceiver I/O 1D 28 28 Transceiver I/O 1E 28 28 Transceiver I/O 1F 28 28 Transceiver I/O 1K 28 - Transceiver I/O 1L 28 - Transceiver I/O 1M 28 - Transceiver I/O 1N 28 - LVDS I/O 2A 48 48 LVDS I/O 2B 48 48 LVDS I/O 2C 48 48 LVDS I/O 2F 24 24 LVDS I/O 2K 24 24 LVDS I/O 2L 48 48 LVDS I/O 2M 48 48 LVDS I/O 2N 48 48 LVDS I/O 3A 48 48 LVDS I/O 3B 48 48 LVDS I/O 3C 24 - LVDS I/O 3I 24 - LVDS I/O 3J 48 48 LVDS I/O 3K 48 48 LVDS I/O 3L 48 48 Transceiver I/O 4C 28 - Transceiver I/O 4D 28 - Transceiver I/O 4E 28 - Transceiver I/O 4F 28 - Transceiver I/O 4K 28 - Transceiver I/O 4L 28 - Transceiver I/O 4M 28 - Transceiver I/O 4N 28 - 3V I/O 6A 8 8 3V I/O 6C 8 - 3V I/O 7A 8 - 3V I/O 7C 8 - Transceiver I/O 8C - 114 Transceiver I/O 9A - 114 Transceiver I/O 9C - 114 SDM shared LVDS I/O SDM 29 29 i. Total LVDS channels per bank supporting SERDES Non-DPA and DPA mode is equivalent to (LVDS I/O per bank)/2, inclusive of clock pair.