Review Article Advanced MOSFET Technologies for Next Generation

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

A Review Paper on Enhancement of Radio Frequency Microelectro Mechanical Systems

International Journal of Engineering Research & Technology (IJERT) ISSN: 2278-0181 Vol. 3 Issue 10, October- 2014 A Review Paper on Enhancement of Radio Frequency MicroElectro Mechanical Systems Shilpa G. Kulkarni Electronics And Telecommunication Engineering V.I.T.Wadala Mumbai - India Abstract—Radio Frequency Micro Electro Mechanical Systems (RF MEMS) refers to the design and fabrication of committed II. NEED FOR RF MEMS MEMS for RF circuits. RF MEMS is a multi-disciplinary area MEMS switches combine the advantageous properties of in which the components operate Micromechanical And / Or mechanical and semiconductor switches.RF MEMS have components are fabricated using micromachining and these advantages such as, Low insertion loss, High isolation, Lower components are used in RF systems. The regular microwave switches currently employed in the microwave industry are power consumption, Excellent signal linearity, Better mechanical switches and semiconductor switches. Mechanical impedance match, Less dispersion , Miniaturization, Simple coaxial and waveguide switches offer benefits such as, low control circuits, High volume production possible, Very large insertion loss, large off-state isolation and high power handling bandwidth , Resistant to external environment. Table Iand Fig capabilities. Yet, they are bulky, heavy and slow. Semiconductor 1provide a comparison of RF MEMS Switches with the switches provide switching at a much faster speed and are conventional switches. smaller in size and weight, but are inferior in insertion loss, DC power consumption, isolation and power handling capabilities TABLE I. COMPARISON OF VARIOUS PARAMETERS[2] than their mechanical counterparts. MEMS switches promise to RF combine the advantageous properties of mechanical and Parameter PIN FET semiconductor switches. There are nevertheless few issues in RF MEMS MEMS Switch like, Actuation Speed, Power handling capacity, Voltage(V) 20-80 ±3-5 3-5 Stiction and Actuation voltage etc. -

"Bob" Schreiner

Oral History of Robert “Bob” Schreiner Interviewed by: Stephen Diamond Recorded: June 10, 2013 Mountain View, California CHM Reference number: X6873.2014 © 2013 Computer History Museum Oral History of Robert “Bob” Schreiner Stephen Diamond: We're here at the Computer History Museum with Bob Schreiner. It's June 10th, 2013, and we're going to talk about the oral history of Synertek and the 6502. Welcome, Bob. Thanks for being here. Can you introduce yourself to us? Robert “Bob” Schreiner: Okay. My name is Bob Schreiner. I'm an ex-Fairchilder, one of the Fairchildren in the valley, and then involved in running a couple of other small semiconductor companies, and I started a semiconductor company. Diamond: So that would be Synertek. Schreiner: Synertek. Diamond: Tell us about that. Schreiner: Okay. As you know from an earlier session I left Fairchild Semiconductor around 1971. And at the time I left I was running the LSI program at Fairchild, and I was a big believer that the future marketplace for MOS technology would be in the custom area. And since Fairchild let that whole thing fall apart, I decided there's got to be room for a company to start up to do that very thing, work with big producers of hardware and develop custom chips for them so they would have a propriety product that would be difficult to copy. So I wrote a business plan, and I went around to a number of manufacturers. I had a computer guy [General Automation], and I had Bulova Watch Company, and I had a company that made electronic telephones [American Telephones], and who was the fourth guy? Escapes my memory right now, but the pitch basically was, "Your business, which now you manufacture things with discrete components, it's going to change. -

Three-Dimensional Integrated Circuit Design: EDA, Design And

Integrated Circuits and Systems Series Editor Anantha Chandrakasan, Massachusetts Institute of Technology Cambridge, Massachusetts For other titles published in this series, go to http://www.springer.com/series/7236 Yuan Xie · Jason Cong · Sachin Sapatnekar Editors Three-Dimensional Integrated Circuit Design EDA, Design and Microarchitectures 123 Editors Yuan Xie Jason Cong Department of Computer Science and Department of Computer Science Engineering University of California, Los Angeles Pennsylvania State University [email protected] [email protected] Sachin Sapatnekar Department of Electrical and Computer Engineering University of Minnesota [email protected] ISBN 978-1-4419-0783-7 e-ISBN 978-1-4419-0784-4 DOI 10.1007/978-1-4419-0784-4 Springer New York Dordrecht Heidelberg London Library of Congress Control Number: 2009939282 © Springer Science+Business Media, LLC 2010 All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden. The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights. Printed on acid-free paper Springer is part of Springer Science+Business Media (www.springer.com) Foreword We live in a time of great change. -

ECE 255, MOSFET Basic Configurations

ECE 255, MOSFET Basic Configurations 8 March 2018 In this lecture, we will go back to Section 7.3, and the basic configurations of MOSFET amplifiers will be studied similar to that of BJT. Previously, it has been shown that with the transistor DC biased at the appropriate point (Q point or operating point), linear relations can be derived between the small voltage signal and current signal. We will continue this analysis with MOSFETs, starting with the common-source amplifier. 1 Common-Source (CS) Amplifier The common-source (CS) amplifier for MOSFET is the analogue of the common- emitter amplifier for BJT. Its popularity arises from its high gain, and that by cascading a number of them, larger amplification of the signal can be achieved. 1.1 Chararacteristic Parameters of the CS Amplifier Figure 1(a) shows the small-signal model for the common-source amplifier. Here, RD is considered part of the amplifier and is the resistance that one measures between the drain and the ground. The small-signal model can be replaced by its hybrid-π model as shown in Figure 1(b). Then the current induced in the output port is i = −gmvgs as indicated by the current source. Thus vo = −gmvgsRD (1.1) By inspection, one sees that Rin = 1; vi = vsig; vgs = vi (1.2) Thus the open-circuit voltage gain is vo Avo = = −gmRD (1.3) vi Printed on March 14, 2018 at 10 : 48: W.C. Chew and S.K. Gupta. 1 One can replace a linear circuit driven by a source by its Th´evenin equivalence. -

Understanding Performance Numbers in Integrated Circuit Design Oprecomp Summer School 2019, Perugia Italy 5 September 2019

Understanding performance numbers in Integrated Circuit Design Oprecomp summer school 2019, Perugia Italy 5 September 2019 Frank K. G¨urkaynak [email protected] Integrated Systems Laboratory Introduction Cost Design Flow Area Speed Area/Speed Trade-offs Power Conclusions 2/74 Who Am I? Born in Istanbul, Turkey Studied and worked at: Istanbul Technical University, Istanbul, Turkey EPFL, Lausanne, Switzerland Worcester Polytechnic Institute, Worcester MA, USA Since 2008: Integrated Systems Laboratory, ETH Zurich Director, Microelectronics Design Center Senior Scientist, group of Prof. Luca Benini Interests: Digital Integrated Circuits Cryptographic Hardware Design Design Flows for Digital Design Processor Design Open Source Hardware Integrated Systems Laboratory Introduction Cost Design Flow Area Speed Area/Speed Trade-offs Power Conclusions 3/74 What Will We Discuss Today? Introduction Cost Structure of Integrated Circuits (ICs) Measuring performance of ICs Why is it difficult? EDA tools should give us a number Area How do people report area? Is that fair? Speed How fast does my circuit actually work? Power These days much more important, but also much harder to get right Integrated Systems Laboratory The performance establishes the solution space Finally the cost sets a limit to what is possible Introduction Cost Design Flow Area Speed Area/Speed Trade-offs Power Conclusions 4/74 System Design Requirements System Requirements Functionality Functionality determines what the system will do Integrated Systems Laboratory Finally the cost sets a limit -

DEVICE and CIRCUIT DESIGN for VLSI by Amr Mohsen

31 DEVICE AND CIRCUIT DESIGN FOR VLSI by Amr Mohsen* Intel Corporation 3065 Bowers Avenue Santa Clara, California 95051 ABSTRACT A review of the device and circuit design complexity and limitations for VLSI is presented. VLSI device performance will be limited by second order device effects, interconnection line de lay and current density and chip power dissipation. The complexity of VLSI circuit design will require hierarchial structured design methodology with special consideration of testability dnd more emphasis on redundancy. New organizations of logic function architectures and smart memories will evolve to take advantage of the topological properties of the VLSI silicon technology. * The author is also on the faculty of California Institute of Technology CALTECH CONFERENCE ON VLSI, January 1979 32 Amr Mohsen I. INTRODUCTION: As semiconductor technology has evolved from discrete to small-scale to medium-scale and through large-scale integration levels a rapid decrease in the cost per function provided by the technology have opened up new applications and industries. Today there is a large interest in the next phase of integration: very large scale integration (VLSI). The semi conductor technology will be able to fabricate chips with more than lOOK devices (l) in the 1980's. The continuous scaling of the semi- conductor devices and increase in components counts on a single chip is resulting in more complex technology developments, device and circuit designs and product definition. In this review paper, projections of how device technology will evolve in the future and the problems and limitations of device and circuit design for VLSI are presented. VLSI TECHNOLOGIES: In Fig. -

Mos Technology, 1963-1974: a Dozen Crucial Years

One of IBM’s most important MOS Technology, 1963-1974: A Dozen Crucial Years contributions to MOS research came from the Components Division, which was responsible for developing by Ross Knox Bassett and manufacturing bipolar transistors for its large computer systems and had very little interest in MOS transistors line can be drawn from the as such. As part of its work on Frosch’s and Derick’s work on bipolar transistors, Donald Kerr and silicon dioxide to the MOS (metal- a group of engineers had discovered A that depositing small amounts of oxide-semiconductor) transistor’s domi- nance of semiconductor technology, phosphorous on the silicon-dioxide but it is neither short nor straight. That surface and forming a layer of line has several discernable segments, phosphosilicate glass (PSG) could first from Frosch and Derick’s work, limit the amount of leakage in bipolar until 1963. In this interval, by and transistors and play an important role large, no one thought seriously about a in enhancing the stability of MOS metal-oxide-semiconductor as a viable transistors. Jerome Eldridge and Pieter technology in its own right. The second Balk from IBM Research implemented segment runs from 1963, when the this work by using thin layers of combination of integrated circuits and PSG to make stable MOS devices. the planar manufacturing process had Other important work on the physics FIG. 2. Drawing of Atalla and Kahng’s “silicon-silicon dioxide surface device,” now known as and chemistry of MOS devices done led people to see MOS transistors as a the MOS transistor, from a 1961 Bell Labs technical memorandum by Kahng. -

Design of a Microelectronic Manufacturing Laboratory

2006-1635: DESIGN OF A MICROELECTRONIC MANUFACTURING LABORATORY Stilson Applin, Montana State University Todd Kaiser, Montana State University Page 11.407.1 Page © American Society for Engineering Education, 2006 Design of a Microelectronic Manufacturing Laboratory Abstract The design of an undergraduate microelectronic manufacturing laboratory for teaching will be described in the following paper. This laboratory emphasizes learning the processes of semiconductor manufacturing and clean room protocol. The laboratory is housed in a 500 square foot, class 10,000 facility. In the laboratory the students, with a junior standing and a science based background, will use a pre-made six mask set to create P and N type transistors as well as inverters and diodes. The students will be conducting oxidization, RCA clean, photolithography, etching, diffusion, metallization and other processes. A brief description of these processes and the methods used to teach them will also be described. In addition to these processes students will also learn about clean room protocol, chemical safety, and testing devices. All of these skills will be marketable to future employers and graduate schools. These same skills and processes will be covered in a seminar course for educators, with the main purpose of inspiring the high school teachers to teach about semiconductor manufacturing. The cost effective design is what makes the laboratory unique. The expenditure control is important due to the size of the Electrical Engineering department. The department has only 250 undergraduates and 40 graduate students, thus internal funding is difficult to obtain. A user fee paid by the students will cover the funding. This fee will be small and manageable for any college student. -

First-Order Circuits

CHAPTER SIX FIRST-ORDER CIRCUITS Chapters 2 to 5 have been devoted exclusively to circuits made of resistors and independent sources. The resistors may contain two or more terminals and may be linear or nonlinear, time-varying or time-invariant. We have shown that these resistive circuits are always governed by algebraic equations. In this chapter, we introduce two new circuit elements, namely, two- terminal capacitors and inductors. We will see that these elements differ from resistors in a fundamental way: They are lossless, and therefore energy is not dissipated but merely stored in these elements. A circuit is said to be dynamic if it includes some capacitor(s) or some inductor(s) or both. In general, dynamic circuits are governed by differential equations. In this initial chapter on dynamic circuits, we consider the simplest subclass described by only one first-order differential equation-hence the name first-order circuits. They include all circuits containing one 2-terminal capacitor (or inductor), plus resistors and independent sources. The important concepts of initial state, equilibrium state, and time constant allow us to find the solution of any first-order linear time-invariant circuit driven by dc sources by inspection (Sec. 3.1). Students should master this material before plunging into the following sections where the inspection method is extended to include linear switching circuits in Sec. 4 and piecewise- linear circuits in Sec. 5. Here,-the important concept of a dynamic route plays a crucial role in the analysis of piecewise-linear circuits by inspection. l TWO-TERMINAL CAPACITORS AND INDUCTORS Many devices cannot be modeled accurately using only resistors. -

Basic Electrical Engineering

BASIC ELECTRICAL ENGINEERING V.HimaBindu V.V.S Madhuri Chandrashekar.D GOKARAJU RANGARAJU INSTITUTE OF ENGINEERING AND TECHNOLOGY (Autonomous) Index: 1. Syllabus……………………………………………….……….. .1 2. Ohm’s Law………………………………………….…………..3 3. KVL,KCL…………………………………………….……….. .4 4. Nodes,Branches& Loops…………………….……….………. 5 5. Series elements & Voltage Division………..………….……….6 6. Parallel elements & Current Division……………….………...7 7. Star-Delta transformation…………………………….………..8 8. Independent Sources …………………………………..……….9 9. Dependent sources……………………………………………12 10. Source Transformation:…………………………………….…13 11. Review of Complex Number…………………………………..16 12. Phasor Representation:………………….…………………….19 13. Phasor Relationship with a pure resistance……………..……23 14. Phasor Relationship with a pure inductance………………....24 15. Phasor Relationship with a pure capacitance………..……….25 16. Series and Parallel combinations of Inductors………….……30 17. Series and parallel connection of capacitors……………...…..32 18. Mesh Analysis…………………………………………………..34 19. Nodal Analysis……………………………………………….…37 20. Average, RMS values……………….……………………….....43 21. R-L Series Circuit……………………………………………...47 22. R-C Series circuit……………………………………………....50 23. R-L-C Series circuit…………………………………………....53 24. Real, reactive & Apparent Power…………………………….56 25. Power triangle……………………………………………….....61 26. Series Resonance……………………………………………….66 27. Parallel Resonance……………………………………………..69 28. Thevenin’s Theorem…………………………………………...72 29. Norton’s Theorem……………………………………………...75 30. Superposition Theorem………………………………………..79 31. -

Chap01: Computer Abstractions and Technology

CHAPTER 1 Computer Abstractions and Technology 1.1 Introduction 3 1.2 Eight Great Ideas in Computer Architecture 11 1.3 Below Your Program 13 1.4 Under the Covers 16 1.5 Technologies for Building Processors and Memory 24 1.6 Performance 28 1.7 The Power Wall 40 1.8 The Sea Change: The Switch from Uniprocessors to Multiprocessors 43 1.9 Real Stuff: Benchmarking the Intel Core i7 46 1.10 Fallacies and Pitfalls 49 1.11 Concluding Remarks 52 1.12 Historical Perspective and Further Reading 54 1.13 Exercises 54 CMPS290 Class Notes (Chap01) Page 1 / 24 by Kuo-pao Yang 1.1 Introduction 3 Modern computer technology requires professionals of every computing specialty to understand both hardware and software. Classes of Computing Applications and Their Characteristics Personal computers o A computer designed for use by an individual, usually incorporating a graphics display, a keyboard, and a mouse. o Personal computers emphasize delivery of good performance to single users at low cost and usually execute third-party software. o This class of computing drove the evolution of many computing technologies, which is only about 35 years old! Server computers o A computer used for running larger programs for multiple users, often simultaneously, and typically accessed only via a network. o Servers are built from the same basic technology as desktop computers, but provide for greater computing, storage, and input/output capacity. Supercomputers o A class of computers with the highest performance and cost o Supercomputers consist of tens of thousands of processors and many terabytes of memory, and cost tens to hundreds of millions of dollars. -

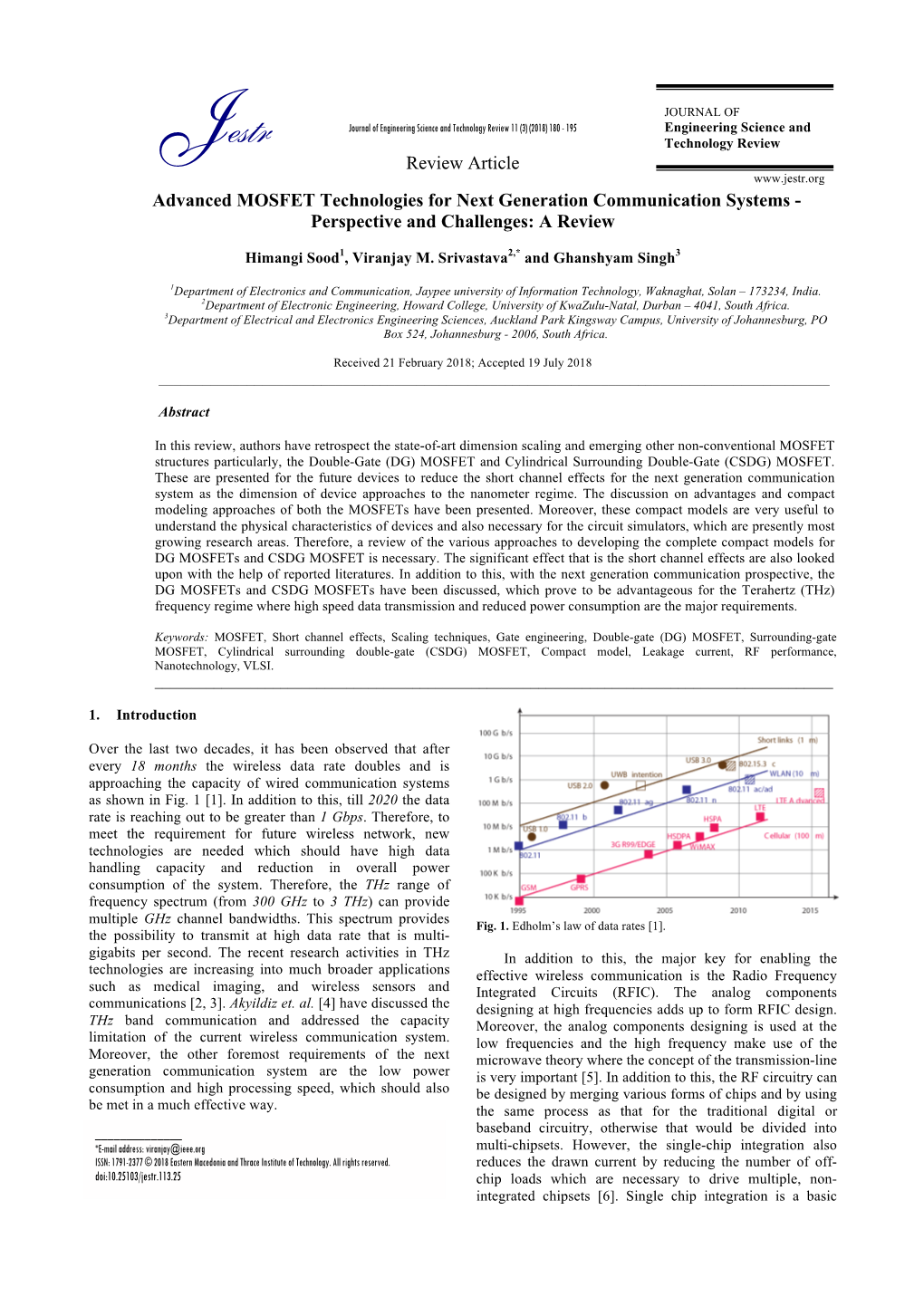

MOSFET Operation Lecture Outline

97.398*, Physical Electronics, Lecture 21 MOSFET Operation Lecture Outline • Last lecture examined the MOSFET structure and required processing steps • Now move on to basic MOSFET operation, some of which may be familiar • First consider drift, the movement of carriers due to an electric field – this is the basic conduction mechanism in the MOSFET • Then review basic regions of operation and charge mechanisms in MOSFET operation 97.398*, Physical Electronics: David J. Walkey Page 2 MOSFET Operation (21) Drift • The movement of charged particles under the influence of an electric field is termed drift • The current density due to conduction by drift can be written in terms of the electron and hole velocities vn and vp (cm/sec) as =+ J qnvnp qpv • This relationship is general in that it merely accounts for particles passing a certain point with a given velocity 97.398*, Physical Electronics: David J. Walkey Page 3 MOSFET Operation (21) Mobility and Velocity Saturation • At low values of electric field E, the carrier velocity is proportional to E -the proportionality constant is the mobility µ • At low fields, the current density can therefore be written Jqn= µ qpµ !nE+!p E v n v p • At high E, scattering limits the velocity to a maximum value and the relationship above no longer holds - this is termed velocity saturation 97.398*, Physical Electronics: David J. Walkey Page 4 MOSFET Operation (21) Factors Influencing Mobility • The value of mobility (velocity per unit electric field) is influenced by several factors – The mechanisms of conduction through the valence and conduction bands are different, and so the mobilities associated with electrons and holes are different.