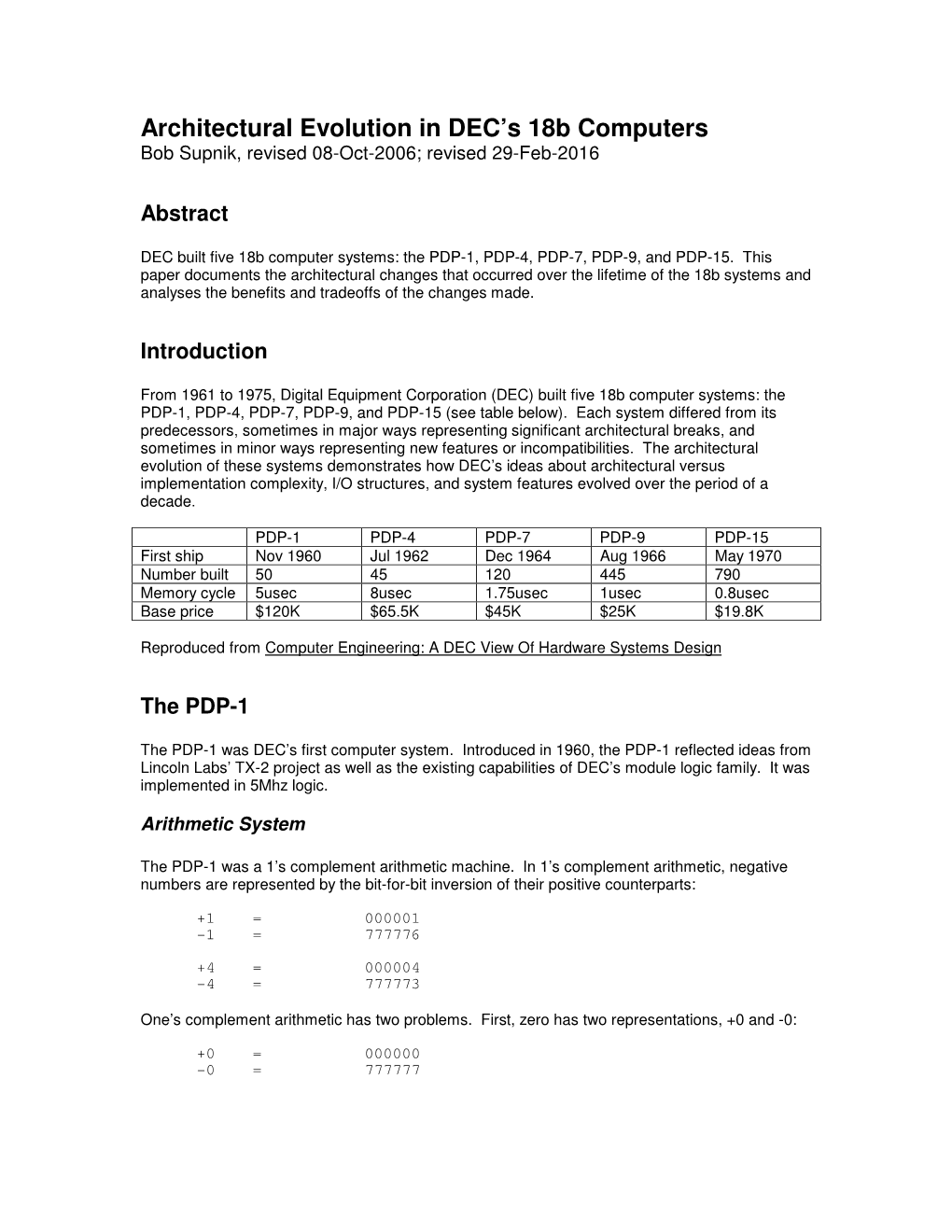

Architectural Evolution in DEC's 18B Computers

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Mobile Digital Computer Program. Mobidic D

UNCLASSIFIED AD 4 7_070 DEFENSE DOCUMEI'TATION CENTER FOR SCIENTIFIC AND TECHNIA!. INFO'UMATION CAMERON STATION, ALEXANDRW , VIFGINI, UNCLASSIFIED NOTICE: When government or other drawings, speci- fications or other data are used for any purpose other than in connection with a definitely related government procurement operation, the U. S. Government thereby incurs no responsibility, nor any obligation whatsoever; and the fact that the Govern- ment may have formulated, furnished, or in any way supplied the said drawings, specifications, or other data is not to be regarded by implication or other- wise as in any manner licensing the holder or any other person or corporation, or conveying any rights or permission to manufacture, use or sell any patented invention that may in any way be related thereto. FINAL REPORT 1 FEBRUARY 1963 J a I MOBILE DIGITAL COMPUTER PROGRAM MOBIDIC D FINAL REPORT 1 July 1958 to 1 February 1963 I Signal Corps Technical Requirements I SCL 1959 SCL 4328 Contract No. DA 3 6 -039-sc-781 6 4 I DA Project No. 3-28-02-201 I Submitted by: _, _ _ _ E. W. Jer'7is, Manage'r MOBIDIC Projects February 1963 S SYLVANIA ELECTRONIC SYSTEMS-EAST SYLVANIA ELECTRONIC SYSTEMS A Division of Sylvania Electric Products Inc. 189 B Street-Needham Heights 94, Massachusetts ~• I 3 TABLE OF CONTENTS I Section Page LIST OF ILLUSTRATIONS v ILIST OF TABLES vii I PURPOSE 1-1 1U1.1 MOBIDIC D General Purpose High-Speed Computer 1-1 1.2 MOBIDIC D Program 1-1 11.2. 1 Phase I -Preliminary Design 1-1 1.2.2 Phase II-Design 1-1 1.2.3 Phase III-Construction and Test 1-2 1.2.4 Phase IV-Update MOBIDIC D to MOBIDIC 7A 1-2 I 1.2.5 Phase V-Van Installation and Test 1,-2 II ABSTRACT 2-1 III PUBLICATIONS, LECTURES, CONFERENCES & TERMINOLOGY 3-1 3.1 Publications 3-1 T3.2 Lectures 3-1 3.3 Conferences 3-2 3.4 Terminology and Abbreviations 3-10 S3.4.1 Logical and Mechanization Designations: 3-13 Central Machine and Converter S3.4.2 Logical and Mechanization Designations: - 3-45 Card Reader and Punch Buffer 3.4. -

Procurement and Retrieval - Meeting the Challenge"

UNCLASSIFIED AD NUMBER AD493137 NEW LIMITATION CHANGE TO Approved for public release, distribution unlimited FROM Distribution authorized to U.S. Gov't. agencies and their contractors; Administrative/Operational Use; 10 JUN 1964. Other requests shall be referred to Bureau of Naval Weapons, Washington, DC. AUTHORITY USNOL ltr, 26 Nov 1969 THIS PAGE IS UNCLASSIFIED NOLTR 64-98 PkOCEEDINGS OF THE 7th MILITARY LIBRARIANS' WORKSHOP "Procurement and Retrieval - Meeting the Challenge" - 0 40 :- =7 - r cOm 1963 No2,3,4 UNITED STATES ,,:,,NAVAL ORDNANCE LABORATORY, WHITE OAK, MARYLAND co I- 0 NOLTR 64-98- PROCEEDINGS OF THE SEVENTH MILITARY LIBRARIANS' WORKSHOP "Procurement and Retrieval - Meeting the Challenge" ABSTRACT: Papers presented at the Workshop on library operation make up the Proceedings. A panel on the Army STINFO program and one on procurement were important contributions to the Work- shop. Two sessions were devoted to library operation - one using computer, the other using automated equipment. Questions and answers at the end of the talks are included. U. S. NAVAL ORDNANCE LABORATORY WHITE OAK, MARYLAND V77 7. NOLTR\64-98 NOLTR 64-98 10 June 1964 PROCEEDINGS OF THE SEVENTH MILITARY LIBRARIANS' WORKSHOP "Procurement and Retrieval - Meeting the Challenge" The Naval Ordnance Laboratory was host to the Seventh Military Librarians' Workshop on 2 - 4 October 1963. These Proceedings are the record of the meeting, including papers presented, and recordings of discussion which followed the talks. The business meeting of the Group, which was held on 4 October, is included in the Proceedings. R. E. 0DENING LAN BECK By directio ii A# NOLTR 64-98 I CONTENTS Page INTRODUCTION ................. -

Published In: Encyclopedia of Library and Information Science, Vol. 49 (New York: Dekker, 1992), Pp

Published in: Encyclopedia of Library and Information Science, vol. 49 (New York: Dekker, 1992), pp. 268-78 Author’s address: [email protected] WORD PROCESSING (HISTORY OF). Definition. The term and concept of “word processing” are by now so widely used that most readers will be already familiar with them. The term, created on the model of “data processing,” is more vague than commonly believed. A human editor, for example, obviously pro- cesses words, but is not what is meant by a “word proces- sor.” A number of software programs process words in one way or another--a concordance or indexing program, for example--but are not understood to be word processing programs.’ The term “word processor” means a facility that records keystrokes from a typewriter-like keyboard, and prints the output onto paper in a separate operation. In the meantime the data is stored, usually in memory or mag- netic media. A word processor also can make improve- ments in the stream of words before they are printed. At their most basic these include the ability to arrange words into lines. An “editor,” such as the infamous EDLINE distributed with the Microsoft Disk Operating System (MS-DOS), lacks the ability to structure lines. Commonly a word processor is understood to be a software program, and in the 1980s and 1990s it usually meant a program written for a microcomputer. However, preceding this period and continuing through it there have been hardware word processors. These are pieces of equip- ment sold for the sole purpose of word processing, con- taining in one package a keyboard, printer, recording and playback device, and in all recent examples a video or liquid crystal display screen. -

The Computer History Simulation Project

The Computer History Simulation Project The Computer History Simulation Project The Computer History Simulation Project is a loose Internet-based collective of people interested in restoring historically significant computer hardware and software systems by simulation. The goal of the project is to create highly portable system simulators and to publish them as freeware on the Internet, with freely available copies of significant or representative software. Simulators SIMH is a highly portable, multi-system simulator. ● Download the latest sources for SIMH (V3.5-1 updated 15-Oct-2005 - see change log). ● Download a zip file containing Windows executables for all the SIMH simulators. The VAX and PDP-11 are compiled without Ethernet support. Versions with Ethernet support are available here. If you download the executables, you should download the source archive as well, as it contains the documentation and other supporting files. ● If your host system is Alpha/VMS, and you want Ethernet support, you need to download the VMS Pcap library and execlet here. SIMH implements simulators for: ● Data General Nova, Eclipse ● Digital Equipment Corporation PDP-1, PDP-4, PDP-7, PDP-8, PDP-9, PDP-10, PDP-11, PDP- 15, VAX ● GRI Corporation GRI-909 ● IBM 1401, 1620, 1130, System 3 ● Interdata (Perkin-Elmer) 16b and 32b systems ● Hewlett-Packard 2116, 2100, 21MX ● Honeywell H316/H516 ● MITS Altair 8800, with both 8080 and Z80 ● Royal-Mcbee LGP-30, LGP-21 ● Scientific Data Systems SDS 940 Also available is a collection of tools for manipulating simulator file formats and for cross- assembling code for the PDP-1, PDP-7, PDP-8, and PDP-11. -

Oral History Interview with George M. Ryan

An Interview with GEORGE M. RYAN OH 253 Conducted by Arthur L. Norberg on 10-11 June 1993 Los Angeles, CA Charles Babbage Institute Center for the History of Information Processing University of Minnesota, Minneapolis Copyright, Charles Babbage Institute 1 George M. Ryan Interview 10-11 June 1993 Abstract After briefly describing his background and education, Ryan, former chairman and CEO of CADO Systems Corporation, discusses his work in the development and distribution of data processing equipment from the early 1950s through the early 1990s. He recalls work with Benson-Lehner in the early 1950s and he describes the firm's development of the computyper, a billing machine. Ryan discusses his role in the sale of the computyper to Friden and his employment by Friden. He recalls his frustration with Friden's attempts at further development of the product, his involvement in the acquisition of the Flexowriter for Friden, and his management of a branch for Friden in Los Angeles. Ryan recalls his return to Benson-Lehner from Friden in the late 1950s and the events leading to his formation of Intercontinental Systems Incorporated with Pete Taylor in the late 1960s. Ryan describes ISI's distribution and development of data processing equipment and his philosophy for the management of engineering and sales at ISI. Ryan recalls his idea to develop a computer for small businesses and describes his role in the partnership that became CADO Systems Corporation in 1976. He discusses the development of the computer by Jim Ferguson and Bob Thorne, his strategy of marketing the computer to small businesses and government offices, CADO's rapid growth, and the creation of additional product lines. -

Research and Development in the Computer and Information Sciences

DOCUMENT RESUME ED 039 891 LI 001 944 AUTHOR Stevens, Mary Elizabeth TITLE Research and Development in the Computer and Information Sciences. Volume 1 r Information Acquisition, Sensing, and Input: A Selective Literature Review. INSTITUTION National Bureau of Standards (DOC), Washington, D.C. Center for Computer Sciences and Technology. REPORT NO NBS-Monogr-113-Vol-1 PUB DATE Mar 70 NOTE 169p. AVAILABLE FROM Superintendent of Documents, U.S. Government Printing Office, Washington, D.C. 20402 (C 13.44:113/Vol.1, $1.50) EDRS PRICE EDRS Price MF-$0.75 HC Not Available from EDRS. DESCRIPTORS Automation, *Computer Science, Information Networks, *Information Processing, *Information Science, *Literature Reviews, Research, *Telecommunication ABSTRACT The series, of which this is the initial report, is intended to give a selective overview of research and development efforts and requirements in the computer and informationsciences. The operations of information acquisition, sensing, andinput to information processing systems ate considered in generalized terms. Specific topics include but are not limited to:(1) source data automation and remote sensing techniques,(2) communication systems and data transmission links, (3) audio and graphic inputs, (4) preprocessing operations upon input items,(5) character recognition, (6) speech recognition and (7) various other aspects of automatic pattern recognition. Supplemental notes and abibliography of over 640 cited references are included. (Author/NH) UNITED STATES DEPARTMENT OF COMMERCE Maurice H. Stans, Secretary NATIONAL BUREAU OF STANDARDS Lewis M. Branscomb, Director CO tr1 cD Research and Development in the um' Computer and Information Sciences 1. Information Acquisition, Sensing, and Input: A Selective Literature Review Mary Elizabeth Stevens Center for Computer Sciences and Technology National Bureau of Standards Washington, D.C. -

Compatible Time-Sharing System (1961-1973) Fiftieth Anniversary

Compatible Time-Sharing System (1961-1973) Fiftieth Anniversary Commemorative Overview The Compatible Time Sharing System (1961–1973) Fiftieth Anniversary Commemorative Overview The design of the cover, half-title page (reverse side of this page), and main title page mimics the design of the 1963 book The Compatible Time-Sharing System: A Programmer’s Guide from the MIT Press. The Compatible Time Sharing System (1961–1973) Fiftieth Anniversary Commemorative Overview Edited by David Walden and Tom Van Vleck With contributions by Fernando Corbató Marjorie Daggett Robert Daley Peter Denning David Alan Grier Richard Mills Roger Roach Allan Scherr Copyright © 2011 David Walden and Tom Van Vleck All rights reserved. Single copies may be printed for personal use. Write to us at [email protected] for a PDF suitable for two-sided printing of multiple copies for non-profit academic or scholarly use. IEEE Computer Society 2001 L Street N.W., Suite 700 Washington, DC 20036-4928 USA First print edition June 2011 (web revision 03) The web edition at http://www.computer.org/portal/web/volunteercenter/history is being updated from the print edition to correct mistakes and add new information. The change history is on page 50. To Fernando Corbató and his MIT collaborators in creating CTSS Contents Preface . ix Acknowledgments . ix MIT nomenclature and abbreviations . x 1 Early history of CTSS . 1 2 The IBM 7094 and CTSS at MIT . 5 3 Uses . 17 4 Memories and views of CTSS . 21 Fernando Corbató . 21 Marjorie Daggett . 22 Robert Daley . 24 Richard Mills . 26 Tom Van Vleck . 31 Roger Roach . -

Digital Equipment Corporation PDP-1

PDP-1 Simulator Usage 13-Jul-2016 COPYRIGHT NOTICE The following copyright notice applies to the SIMH source, binary, and documentation: Original code published in 1993-2016, written by Robert M Supnik Copyright (c) 1993-2016, Robert M Supnik Permission is hereby granted, free of charge, to any person obtaining a copy of this software and associated documentation files (the "Software"), to deal in the Software without restriction, including without limitation the rights to use, copy, modify, merge, publish, distribute, sublicense, and/or sell copies of the Software, and to permit persons to whom the Software is furnished to do so, subject to the following conditions: The above copyright notice and this permission notice shall be included in all copies or substantial portions of the Software. THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL ROBERT M SUPNIK BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE SOFTWARE. Except as contained in this notice, the name of Robert M Supnik shall not be used in advertising or otherwise to promote the sale, use or other dealings in this Software without prior written authorization from Robert M Supnik. 1 Simulator Files ............................................................................................................. 3 2 PDP-1 Features ........................................................................................................... 3 2.1 CPU ...................................................................................................................... 4 2.2 Programmed I/O Devices ..................................................................................... 5 2.2.1 Paper Tape Reader (PTR) ............................................................................ -

An Informal Look Into the History of Digital Typography

An informal look into the history of digital typography David Walden walden-family.com/texland (Comments to me as [email protected]) October 25, 2016 Introduction The ditto machine at the elementary school at which my mother taught was what first sparked my interest in printing (and it had a swell smell). I became seriously interested in the craft of printing during four summers of college when I worked in or near the printing department of a large Fibreboard company plant that made cardboard packaging for food and drink companies (for example, cereal boxes and milk cartons). The plant had a four-color Miehle offset lithography machine that printed an array of boxes on each approximately 4.5-foot-by-6.5-foot sheet of cardboard; the plant also had big two-color lithograph machines and a couple of smaller letterpress machines. I have retained this interest in printing throughout my life. I didn’t begin to explicitly think about typography itself1,2 until about 20 years ago when I adopted LATEX for drafting and formatting books and papers I write. Then in 2012, I began to think about the history of printing and typography as I prepared a presentation for TUG2012 in Boston.3,4 Since then I have been reading (books, papers, Internet websites) and watching YouTube videos about the history of printing and typography that in time led into the digital era. This companion paper to my TUG2016 presentation sketches some of what I (think I) have learned in the hope that my study and thinking will be useful to someone else who is just starting to dig into this history. -

Vectrex Punched Paper Tape up from the Depths

VECTREX THE ULTIMATE RETROGAMING MACHINE PUNCHED PAPER TAPE DATA STORAGE FOR REAL MEN UP FROM THE DEPTHS A TALE BY SHAUN M. WHEELER BOOTSTRAPPING OLD MACS A CRASH COURSE ON THE LININTOSH SERVER SOLDERING FOR BEGINNERS TONY FINK’S GUIDE TO NOT BURNING YOURSELF GROWING UP WITH A DRAGON 32 NO SUBSTITUTE FOR CHARM AND POISE #"6% HOW TO MAKE FRIENDS AND INFLUENCE PEOPLE IN THE 1980s by Dale Goodfellow Watty was impressed. ladies (well that would have came later, you ISSUE #1 - January 2010 understand - I was still a boy) and in general we have, I would state, a moral right to duplicate Ever since he realised, when we were about offer me many of the societal rewards that and distribute these historical works. I would also 10 years old, that I was in fact not ‘hard’ an eleven year old desires. FINDERS KEEPERS extend this to cover books and magazines, the but just fat, and had ‘battered’ me, I had an I know its theft, I just don’t care! recognised ephemera of all ages. apprehensive relationship with him. I always All of these things were easily within my felt that it could turn violent at any time. grasp... We may as well tackle this one straight off the bat. The people and the skills needed to start from To state the case; to make the point; to clarify the scratch on a Z80 and a 6502 are disappearing as sentiment; to justify our indifference to Intellectual each year passes. Individuals who, while having a Watty was impressed and this was good, as Only one thing stood in my way – I had a property rights.. -

Research and Development in the Computer and Information Sciences

A11 100989830 NBS-PUB-C 1 ST5°5l"v'^113;1-3;197 C.1 Standaras national Bureau of Bldg. Ubrary, E-01 Admin. NBS MONOGRAPH 113, VOLUME 1 Standards Nationsi Bureau of JUL 2 8 1972 : /120S OS. I to Research and Development in the Computer and Information Sciences Volume 1. Information Acquisition, Sensing, and Input— U.S. A Selective Literature Review (ITMENT OF l/IMERCE National Bureau of tandards NATIONAL BUREAU OF STANDARDS The National Bureau of Standards ' was established by an act of Congress March 3, 1901. Today, in addition to serving as the Nation's central measurement laboratory, the Bureau is a principal focal point in the Federal Government for assuring maximum application of the physical and engineering sciences to the advancement of technology in industry and commerce. To this end the Bureau conducts research and provides central national services in four broad program areas. These are: (1) basic measurements and standards, (2) materials measurements and standards, (3) technological measurements and standards, and (4) transfer of technology. The Bureau comprises the Institute for Basic Standards, the Institute for Materials Research, the Institute for Applied Technology, the Center for Radiation Research, the Center for Computer Sciences and Technology, and the Office for Information Programs. THE INSTITUTE FOR BASIC STANDARDS provides the centra! basis within the United States of a complete and consistent system of physical measurement; coordinates that system with measurement systems of other nations; and furnishes essential -

Office Machines. By

REPOR TRESUMES ED 011 560 VT 002 929 OFFICE MACHINES. BY.. HILL, MARCELLA P. NEW JERSEY STATE DEPT. OF EDUCATION, TRENTON RUTGERS, THE STATE UNIV., NEW BRUNSWICK, N.J. PUB DATE JAN 67 EDRS PRICE MF -$1.50 HC-$14.16 352P. DESCRIPTORS-. *OFFICE OCCUPATIONS EDUCATION, *OFFICE MACHINES, *STUDY GUIDES, GRADE 11, *DEAF EDUCATION, *SPECIAL EDUCATION, RETARDED CHILDREN, CLERICAL OCCUPATIONS, DESIGNED FOR STUDENTS' READING IN THE JUNIOR YEAR OF HIGH SCHOOL, THIS MANUAL PRESENTS AN INTRODUCTION TO THE VARIETY OF POSITIONS HELD BY CLERICAL WORKERS AND AN IDEA OF THE MACHINE SKILLS, KNOWLEDGE, AND ATTITUDE THAT WILL BE EXPECTED IN BUSINESS. IT WAS DEVELOPED BY THE AUTHOR AND SCHOOL FACULTY FOLLOWING THE COURSE OF STUDY APPROVED BY THE BOARD OF EDUCATION AND WAS TESTED IN VARIOUS CLASSROOMS. THE MATERIAL WAS DESIGNED FOR ONE YEAR OF SHOP WORK AT A LOW LEVEL IN A SCHOOL FOR DEAF OR RETARDED STUDENTS. THE INSTRUCTOR SHOULD BE CERTIFIED. UNITS ARE (1) THE MEANING OF OFFICE PRACTICE CLASS,(2) TYPEWRITERS,(3) MIMEOGRAPHS, (4) FLUID DUPLICATORS, (5) FLEXOWRITER, (6) PHOTOCOPYING MACHINES,(7) ADDING MACHINES,(8) CALCULATING MACHINES, (9) BOOKKEEPING MACHINES, (10) VARITYPER, AND (11) JOB TITLES. AN ACHIEVEMENT TEST, PROJECTS, AND A VOCABULARY FOLLOW EACH UNIT. EACH LESSON GIVES OBJECTIVES, TOPIC INFORMATION, ASSIGNMENTS, ILLUSTRATIONS, AND A VOCABULARY. THIS DOCUMENT IS ALSO AVAILABLE FOR $2.00 FROM VOCATIONAL - TECHNICAL LABORATORY, RUTGERS UNIVERSITY, 10 SEMINARY PLACE, NEW BRUNSWICK, NEW JERSEY 08903. (PS) STATE OF NEW JERSEY DEPARTMENT OF EDUCATION DIVISION OF VOCATIONAL EDUCATION OFFICE MACHINES MARCELLA P. HILL, INSTRUCTOR MARIE KATZENBACH SCHOOL FOR THE DEAF WEST TRENTON, NEW JERSEY MEMORANDUM TO: The ERIC Clearinghonse on Vocationaland Technical Education The Ohio State University 980 Kinnear Road Columbus, Ohio43212 Vocational Div.-Curriculum Laboratory FROM: amin New Brunswick,N J 08903 (Address) School of Education-Rutgers;10 Seminary Place, DATE: July 10, 1967 P.