Testing Bicmos and Dynamic CMOS Logic

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

A New Paradigm in High-Speed and High-Efficiency Silicon Photodiodes

382 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 65, NO. 2, FEBRUARY 2018 A New Paradigm in High-Speed and High-Efficiency Silicon Photodiodes for Communication—Part II: Device and VLSI Integration Challenges for Low-Dimensional Structures Hilal Cansizoglu , Member, IEEE, Aly F. Elrefaie, Fellow, IEEE, Cesar Bartolo-Perez, Toshishige Yamada, Senior Member, IEEE, Yang Gao, Ahmed S. Mayet, Mehmet F. Cansizoglu, Ekaterina Ponizovskaya Devine, Shih-Yuan Wang, Life Fellow, IEEE,and M. Saif Islam, Senior Member, IEEE (Invited Review Paper) Abstract— The ability to monolithically integrate high- Index Terms— CMOS integration, extended-reach links, speed photodetectors (PDs) with silicon (Si) can contribute high speed, high-efficiency photodetectors (PDs), high- to drastic reduction in cost. Such PDs are envisioned to performance computing, light detection and ranging, micro- be integral parts of high-speed optical interconnects in /nanostructures, single-photon detection, surface states, the future intrachip, chip-to-chip, board-to-board, rack-to- very-large-scale integration (VLSI) and ultralarge-scale inte- rack, and intra-/interdata center links. Si-based PDs are of gration (ULSI). special interest since they present the potential for mono- lithic integration with CMOS and BiCMOS very-large-scale integration and ultralarge-scale integration electronics. I. INTRODUCTION In the second part of this review, we present the efforts HE rise of distributed computing, cloud storage, social pursued by the researchers in engineering and integrating Si, SiGe alloys, and Ge PDs to CMOS and BiCMOS electron- Tmedia, and affordable hand-held devices currently allow ics and compare the performance of recently demonstrated extreme ease of transferring a plethora of data including CMOS-compatible ultrafast surface-illuminated Si PD with videos, pictures, and texts, all over the world. -

Reduced Swing Domino Techniques for Low Power and High Performance Arithmetic Circuits

Reduced Swing Domino Techniques for Low Power and High Performance Arithmetic Circuits by Shahrzad Naraghi A thesis presented to the University of Waterloo in ful¯llment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering Waterloo, Ontario, Canada 2004 °c Shahrzad Naraghi, 2004 I hereby declare that I am the sole author of this thesis. I authorize the University of Waterloo to lend this thesis to other institutions or individuals for the purpose of scholarly research. Shahrzad Naraghi I authorize the University of Waterloo to reproduce this thesis by photocopying or other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research. Shahrzad Naraghi ii The University of Waterloo requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date. iii Acknowledgements First, I would like to thank my supervisor Professor Manoj Sachdev for his great guidance, support and patience. His advice and support were always greatly appreciated. I also want to thank Dr. Opal and Dr. Anis, my thesis readers. I'd like to thank Bhaskar Chatterjee for his great help on my research; Phil Regier for his great help on computer problems; and my good friends for bringing me joy and laughter during these years that I was away from my family. Most importantly, I'd like to thank my family for their supporting and encouraging com- ments, their love and faith in me. iv Abstract The increasing frequency of operation and the larger number of transistors on the chip, along with slower decrease in supply voltage have led to more power dissipation and high chip power density which cause problems in chip thermal management and heat removal process. -

Vlsi Design Lecture Notes B.Tech (Iv Year – I Sem) (2018-19)

VLSI DESIGN LECTURE NOTES B.TECH (IV YEAR – I SEM) (2018-19) Prepared by Dr. V.M. Senthilkumar, Professor/ECE & Ms.M.Anusha, AP/ECE Department of Electronics and Communication Engineering MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY (Autonomous Institution – UGC, Govt. of India) Recognized under 2(f) and 12 (B) of UGC ACT 1956 (Affiliated to JNTUH, Hyderabad, Approved by AICTE - Accredited by NBA & NAAC – ‘A’ Grade - ISO 9001:2015 Certified) Maisammaguda, Dhulapally (Post Via. Kompally), Secunderabad – 500100, Telangana State, India Unit -1 IC Technologies, MOS & Bi CMOS Circuits Unit -1 IC Technologies, MOS & Bi CMOS Circuits UNIT-I IC Technologies Introduction Basic Electrical Properties of MOS and BiCMOS Circuits MOS I - V relationships DS DS PMOS MOS transistor Threshold Voltage - VT figure of NMOS merit-ω0 Transconductance-g , g ; CMOS m ds Pass transistor & NMOS Inverter, Various BiCMOS pull ups, CMOS Inverter Technologies analysis and design Bi-CMOS Inverters Unit -1 IC Technologies, MOS & Bi CMOS Circuits INTRODUCTION TO IC TECHNOLOGY The development of electronics endless with invention of vaccum tubes and associated electronic circuits. This activity termed as vaccum tube electronics, afterward the evolution of solid state devices and consequent development of integrated circuits are responsible for the present status of communication, computing and instrumentation. • The first vaccum tube diode was invented by john ambrase Fleming in 1904. • The vaccum triode was invented by lee de forest in 1906. Early developments of the Integrated Circuit (IC) go back to 1949. German engineer Werner Jacobi filed a patent for an IC like semiconductor amplifying device showing five transistors on a common substrate in a 2-stage amplifier arrangement. -

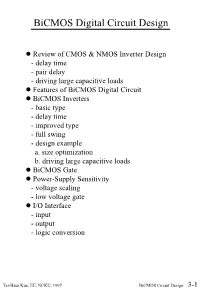

Bicmos Digital Circuit Design

BiCMOS Digital Circuit Design Review of CMOS & NMOS Inverter Design - delay time - pair delay - driving large capacitive loads Features of BiCMOS Digital Circuit BiCMOS Inverters -basic type - delay time - improved type - full swing - design example a. size optimization b. driving large capacitive loads BiCMOS Gate Power-Supply Sensitivity - voltage scaling - low voltage gate I/O Interface - input - output - logic conversion Tai-Haur Kuo, EE, NCKU, 1997 BiCMOS Circuit Design 3-1 NMOS DIGITAL CIRCUITS Static inverters Load Vout ==> V in driver A B C IDS VGS=V(1) C B A VDS (driver) VDD Vth VDD D: in in Vout VGS=V(1) VGS=V(0) V(0) V(0) V(1) V(0) V(1) Vin ― Static power dissipation during Vout=V(0) Tai-Haur Kuo, EE, NCKU, 1997 BiCMOS Circuit Design 3-2 Switching Characteristics of CMOS Inverter CMOS inverter VDD VDD T 2 V (t) o t Vin(t) T1 CL +VDD Vin(t) 0 t +VDD 0.9VDD 0.1VDD t td tf tr Trajectory of n-transistor operating point during switching in CMOS inverter Input transition : X1 X2 Output transition: X2 X3 Vds=Vgs-Vt UNSATURATED SATURATED STATE STATE X2 Vgs=VDD Ids OPERATING POINT AFTER COMPLETION OF SWITCHING INITIAL OPERATING POINT X3 X1 0 VDD Vo(t) Tai-Haur Kuo, EE, NCKU, 1997 BiCMOS Circuit Design 3-3 Rise Time and Fall Time of CMOS Inverter > Equivalent Circuit V DD VDD > Fall p-DEVICE p-DEVICE t=0 t=0 I Vin ↑ c Ic Idsn R V c C o Vo n-DEVICE L n-DEVICE CL Vo ↓ SATURATION: VVoD≥ D− Vtn 0 < VV≤ − V (a) SATURATION: 0 DD tn > Rise VDD VDD p-DEVICE p-DEVICE Idsp Rc Vin ↓ I Ic Vo ↑ t=0 c Vo Vo n-DEVICE CL n-DEVICE -

Chapter 6 PROBLEMS

1 Chapter 6 Problem Set Chapter 6 PROBLEMS 1. [E, None, 4.2] Implement the equation X = ((A + B) (C + D + E) + F) G using complemen- tary CMOS. Size the devices so that the output resistance is the same as that of an inverter with an NMOS W/L = 2 and PMOS W/L = 6. Which input pattern(s) would give the worst and best equivalent pull-up or pull-down resistance? Solution Rewriting the output expression in the form X = ((A + B) (C + D + E) + F) G = ((AB + CDE)F) + G allows us to build the pulldown network by inspection (parallel devices imple- ment an OR, and series devices implement an AND). The pullup network is the dual of the pulldown network. A B 24 24 F 12 C 24 D 24 E 24 G 12 X A 8 C 12 G 2 B 8 D 12 E 12 F 4 The plot shows sizes that meet the requirement - in the worst case, the output resistance of the circuit matches the output resistance of an inverter with NMOS W/L=2 and PMOS W/L=6. The worst case pull-up resistance occurs whenever a single path exists from the output node to Vdd. Examples of vectors for the worst case are ABCDEFG=1111100 and 0101110. The best case pull-up resistance occurs when ABCDEFG=0000000. The worst case pull-down resistance occurs whenever a single path exists from the out- put node to GND. Examples of vectors for the worst case are ABCDEFG=0000001 and 0011110. The best case pull-down resistance occurs when ABCDEFG=1111111. -

High-Performance Flexible Bicmos Electronics Based on Single-Crystal

www.nature.com/npjflexelectron ARTICLE OPEN High-performance flexible BiCMOS electronics based on single-crystal Si nanomembrane Jung-Hun Seo 1,3, Kan Zhang1, Munho Kim1, Weidong Zhou2 and Zhenqiang Ma1 In this work, we have demonstrated for the first time integrated flexible bipolar-complementary metal-oxide-semiconductor (BiCMOS) thin-film transistors (TFTs) based on a transferable single crystalline Si nanomembrane (Si NM) on a single piece of bendable plastic substrate. The n-channel, p-channel metal-oxide semiconductor field-effect transistors (N-MOSFETs & P-MOSFETs), and NPN bipolar junction transistors (BJTs) were realized together on a 340-nm thick Si NM layer with minimized processing complexity at low cost for advanced flexible electronic applications. The fabrication process was simplified by thoughtfully arranging the sequence of necessary ion implantation steps with carefully selected energies, doses and anneal conditions, and by wisely combining some costly processing steps that are otherwise separately needed for all three types of transistors. All types of TFTs demonstrated excellent DC and radio-frequency (RF) characteristics and exhibited stable transconductance and current gain under bending conditions. Overall, Si NM-based flexible BiCMOS TFTs offer great promises for high-performance and multi- functional future flexible electronics applications and is expected to provide a much larger and more versatile platform to address a broader range of applications. Moreover, the flexible BiCMOS process proposed and demonstrated here -

Designing Combinational Logic Gates in Cmos

CHAPTER 6 DESIGNING COMBINATIONAL LOGIC GATES IN CMOS In-depth discussion of logic families in CMOS—static and dynamic, pass-transistor, nonra- tioed and ratioed logic n Optimizing a logic gate for area, speed, energy, or robustness n Low-power and high-performance circuit-design techniques 6.1 Introduction 6.3.2 Speed and Power Dissipation of Dynamic Logic 6.2 Static CMOS Design 6.3.3 Issues in Dynamic Design 6.2.1 Complementary CMOS 6.3.4 Cascading Dynamic Gates 6.5 Leakage in Low Voltage Systems 6.2.2 Ratioed Logic 6.4 Perspective: How to Choose a Logic Style 6.2.3 Pass-Transistor Logic 6.6 Summary 6.3 Dynamic CMOS Design 6.7 To Probe Further 6.3.1 Dynamic Logic: Basic Principles 6.8 Exercises and Design Problems 197 198 DESIGNING COMBINATIONAL LOGIC GATES IN CMOS Chapter 6 6.1Introduction The design considerations for a simple inverter circuit were presented in the previous chapter. In this chapter, the design of the inverter will be extended to address the synthesis of arbitrary digital gates such as NOR, NAND and XOR. The focus will be on combina- tional logic (or non-regenerative) circuits that have the property that at any point in time, the output of the circuit is related to its current input signals by some Boolean expression (assuming that the transients through the logic gates have settled). No intentional connec- tion between outputs and inputs is present. In another class of circuits, known as sequential or regenerative circuits —to be dis- cussed in a later chapter—, the output is not only a function of the current input data, but also of previous values of the input signals (Figure 6.1). -

Comparision on Different Domino Logic Design for High- Performance and Leakage-Tolerant Wide OR Gate

Ajay Kumar Dadoria et al Int. Journal of Engineering Research and Applications www.ijera.com ISSN : 2248-9622, Vol. 3, Issue 6, Nov-Dec 2013, pp.2048-2052 RESEARCH ARTICLE OPEN ACCESS Comparision on Different Domino Logic Design for High- Performance and Leakage-Tolerant Wide OR Gate Uday Panwar*, Ajay Kumar Dadoria** (Department of Electronics and Communication Engineering MANIT Bhopal, M.P., India ABSTRACT - Dynamic logic circuits are used for high performance and high speed applications. Wide OR gates are used in Dynamic RAMs, Static RAMs, high speed processors and other high speed circuits. In spite of their high performance, dynamic logic circuit has high noise and extensive leakage which has caused problems for the circuits. To overcome these problems Domino logic circuits are used which reduce sub-threshold leakage current in standby mode and improve noise immunity for wide OR gates. In this paper we analyze and compare different domino logic design topologies for lowering the sub-threshold leakage current in standby mode, increasing the speed and increasing the noise immunity. We compare power, delay, and unit noise gain (UNG) of different topologies. The simulation results revealed that High Speed Clock Delay Domino (HSCD) circuit gives the better results in terms of reduction in delay and power consumption as compare to other circuits. Keywords - Wide domino circuit, sub-threshold leakage current, delay, noise immunity. I. INTRODUCTION VDD VDD In comparison to static CMOS circuits, dynamic PRECHARGE TRANSISTOR KEEPER TRANSISTOR CMOS circuits have a large number of advantages CLK MP MP2 such as lower number of transistors, low-power, 1 higher speed, short-circuit power free and glitch-free VDD operation. -

IEDM 2003 Conference Paper on Diode Triggered

Conference paper Diode-Triggered SCR (DTSCR) for RF-ESD Protection of BiCMOS SiGe HBTs and CMOS Ultra-Thin Gate Oxides International Electron Devices Meeting 2003 A novel Diode‐Triggered SCR (DTSCR) ESD protection element is introduced for low‐voltage application (signal, supply voltage ≤1.8V) and extremely narrow ESD design margins. Trigger voltage engineering in conjunction with fast and efficient SCR voltage clamping is applied for the protection of ultra‐sensitive circuit nodes, such as SiGe HBT bases (e.g. fTmax=45GHz in BiCMOS‐0.35u LNA input) and thin gate‐oxides (e.g. tox=1.7nm in CMOS‐ 0.09u input). SCR integration is possible based on CMOS devices or can alternatively be formed by high‐speed SiGe HBT’s. Diode-Triggered SCR (DTSCR) for RF-ESD Protection of BiCMOS SiGe HBTs and CMOS Ultra-Thin Gate Oxides Markus P.J. Mergens, Christian C. Russ**, Koen G. Verhaege, John Armer*, Phillip C. Jozwiak*, Russ Mohn*, Bart Keppens, Con Son Trinh* Sarnoff Europe, Brugse Baan 188A, B-8470 Gistel, Belgium, Europe Phone: ++49-751-3525633 - Fax: ++49-751-3525962, e-mail: [email protected] *) Sarnoff Corporation, 201 Washington Road, Princeton, NJ-08543, USA **) formerly with Sarnoff Corp., now with Infineon Technologies, Munich, Germany, Europe Abstract – A novel Diode-Triggered SCR (DTSCR) ESD protection element is introduced for low-voltage application (signal, supply voltage ≤ 1.8V) and extremely narrow ESD design margins. Trigger voltage engineering in conjunction with fast and efficient SCR voltage clamping is applied for the protection of ultra-sensitive circuit nodes, such as SiGe HBT bases (e.g. -

Why Dynamic Logic

Lecture 13 Why dynamic Logic • It occupies less area…………………compare to static CMOS • It has higher speed …………………compare to static CMOS • It has less power ………………….compare to static CMOS Why not • Requires a clock • Can not operate at low speed • It is affected by charge sharing • Circuits are more sensitive to timing errors and noise • Design is more difficult Page 1 of 32 An introduction to dynamic logic 1. Dynamic logic In static logic families the pull up and pull down networks operate concurrently. Dynamic logic on the other hand uses a sequence of precharge and conditional evaluation phases governed by the clock to realize complex logic functions. Figure 1 Dynamic logic A dynamic logic block is shown in Fig. 1. Both forms of Fig.1 can be used. In our analysis we will concentrate on Fig.1 n-logic network. The operation of the pull- down network (PDN) can be divided into two major phases. The precharge and the evaluation phase. In what mode the circuit is operating is determined by the signal φ, the “clock” signal. Let us take an example of either network: Page 2 of 32 Mp precharge transistor OUTPUT A C B CLK ф Me Evaluation transistor CLK OUTPUT Precharge Evaluation Precharge Fig. 2 Example of nmos block For OUTPUT= (A.B + C)’ Precharge When φ =0, the output node “OUT” is precharged to VDD by the PMOS transistor. During that time, the nmos evaluation transistor is off, so the nmos logic network is isolated from ground by a series of nmos transistors and hence no dc current flows regardless of the values of the input signal. -

Logic Families

Logic Families PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Mon, 11 Aug 2014 22:42:35 UTC Contents Articles Logic family 1 Resistor–transistor logic 7 Diode–transistor logic 10 Emitter-coupled logic 11 Gunning transceiver logic 16 Transistor–transistor logic 16 PMOS logic 23 NMOS logic 24 CMOS 25 BiCMOS 33 Integrated injection logic 34 7400 series 35 List of 7400 series integrated circuits 41 4000 series 62 List of 4000 series integrated circuits 69 References Article Sources and Contributors 75 Image Sources, Licenses and Contributors 76 Article Licenses License 77 Logic family 1 Logic family In computer engineering, a logic family may refer to one of two related concepts. A logic family of monolithic digital integrated circuit devices is a group of electronic logic gates constructed using one of several different designs, usually with compatible logic levels and power supply characteristics within a family. Many logic families were produced as individual components, each containing one or a few related basic logical functions, which could be used as "building-blocks" to create systems or as so-called "glue" to interconnect more complex integrated circuits. A "logic family" may also refer to a set of techniques used to implement logic within VLSI integrated circuits such as central processors, memories, or other complex functions. Some such logic families use static techniques to minimize design complexity. Other such logic families, such as domino logic, use clocked dynamic techniques to minimize size, power consumption, and delay. Before the widespread use of integrated circuits, various solid-state and vacuum-tube logic systems were used but these were never as standardized and interoperable as the integrated-circuit devices. -

Dynamic Logic

6/8/2018 ECE4740: Digital VLSI Design Lecture 15: Dynamic logic 542 Recap Pseudo NMOS and pass -transistor logic 543 1 6/8/2018 Ratio’ed logic VDD VDD VDD Resistive Depletion V PMOS Load RL Load T < 0 Load VSS F F F In 1 In 1 In 1 In 2 PDN In 2 PDN In 2 PDN In 3 In 3 In 3 VSS VSS VSS (a) resistive load (b) depletion load NMOS (c) pseudo-NMOS • Goal: Reduce # of transistors over CMOS • Ratio’ed = functionality depends on ratios! • Static power When exactly? 544 Image taken from: CMOS VLSI Design: A Circuits and Systems Perspective by Weste, Harris Improving loads is critical VDD VDD M1 M2 Out Out !A A B PDN1 PDN2 !B VSS VSS • Differential cascode voltage switch logic (DCVSL) • No static power consumption but more routing • Gates keep state why could this be useful? 545 Image taken from: CMOS VLSI Design: A Circuits and Systems Perspective by Weste, Harris 2 6/8/2018 Pass transistor logic: AND gate B A B F=A* B A B 0 0 0 F=A*B 0 1 0 0 1 0 0 1 1 1 • Requires 4 logic gates (needs an inverter) • CMOS logic would require 6 logic gates • The gate has no rail-to-rail swing • Non-inverting logic 546 Key issue: static power In = V DD M2 Vx = V DD -VTn A = V DD M1 • Pass transistor suffers from body effect • M2 may be weakly conducting forming a path from V DD to GND • Can fix with level-restorer transistor 547 3 6/8/2018 We can go faster Dynamic logic 548 Do not confuse with sequential logic combinational sequential In sequential or Out Combinationalsequential Combinational In Out static CMOS logicLogic circuit Logic Circuit logicCircuit circuit