Bicmos TECHNOLOGY and APPLICATIONS the KLUWER INTERNATIONAL SERIES in ENGINEERING and COMPUTER SCIENCE

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

A New Paradigm in High-Speed and High-Efficiency Silicon Photodiodes

382 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 65, NO. 2, FEBRUARY 2018 A New Paradigm in High-Speed and High-Efficiency Silicon Photodiodes for Communication—Part II: Device and VLSI Integration Challenges for Low-Dimensional Structures Hilal Cansizoglu , Member, IEEE, Aly F. Elrefaie, Fellow, IEEE, Cesar Bartolo-Perez, Toshishige Yamada, Senior Member, IEEE, Yang Gao, Ahmed S. Mayet, Mehmet F. Cansizoglu, Ekaterina Ponizovskaya Devine, Shih-Yuan Wang, Life Fellow, IEEE,and M. Saif Islam, Senior Member, IEEE (Invited Review Paper) Abstract— The ability to monolithically integrate high- Index Terms— CMOS integration, extended-reach links, speed photodetectors (PDs) with silicon (Si) can contribute high speed, high-efficiency photodetectors (PDs), high- to drastic reduction in cost. Such PDs are envisioned to performance computing, light detection and ranging, micro- be integral parts of high-speed optical interconnects in /nanostructures, single-photon detection, surface states, the future intrachip, chip-to-chip, board-to-board, rack-to- very-large-scale integration (VLSI) and ultralarge-scale inte- rack, and intra-/interdata center links. Si-based PDs are of gration (ULSI). special interest since they present the potential for mono- lithic integration with CMOS and BiCMOS very-large-scale integration and ultralarge-scale integration electronics. I. INTRODUCTION In the second part of this review, we present the efforts HE rise of distributed computing, cloud storage, social pursued by the researchers in engineering and integrating Si, SiGe alloys, and Ge PDs to CMOS and BiCMOS electron- Tmedia, and affordable hand-held devices currently allow ics and compare the performance of recently demonstrated extreme ease of transferring a plethora of data including CMOS-compatible ultrafast surface-illuminated Si PD with videos, pictures, and texts, all over the world. -

Vlsi Design Lecture Notes B.Tech (Iv Year – I Sem) (2018-19)

VLSI DESIGN LECTURE NOTES B.TECH (IV YEAR – I SEM) (2018-19) Prepared by Dr. V.M. Senthilkumar, Professor/ECE & Ms.M.Anusha, AP/ECE Department of Electronics and Communication Engineering MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY (Autonomous Institution – UGC, Govt. of India) Recognized under 2(f) and 12 (B) of UGC ACT 1956 (Affiliated to JNTUH, Hyderabad, Approved by AICTE - Accredited by NBA & NAAC – ‘A’ Grade - ISO 9001:2015 Certified) Maisammaguda, Dhulapally (Post Via. Kompally), Secunderabad – 500100, Telangana State, India Unit -1 IC Technologies, MOS & Bi CMOS Circuits Unit -1 IC Technologies, MOS & Bi CMOS Circuits UNIT-I IC Technologies Introduction Basic Electrical Properties of MOS and BiCMOS Circuits MOS I - V relationships DS DS PMOS MOS transistor Threshold Voltage - VT figure of NMOS merit-ω0 Transconductance-g , g ; CMOS m ds Pass transistor & NMOS Inverter, Various BiCMOS pull ups, CMOS Inverter Technologies analysis and design Bi-CMOS Inverters Unit -1 IC Technologies, MOS & Bi CMOS Circuits INTRODUCTION TO IC TECHNOLOGY The development of electronics endless with invention of vaccum tubes and associated electronic circuits. This activity termed as vaccum tube electronics, afterward the evolution of solid state devices and consequent development of integrated circuits are responsible for the present status of communication, computing and instrumentation. • The first vaccum tube diode was invented by john ambrase Fleming in 1904. • The vaccum triode was invented by lee de forest in 1906. Early developments of the Integrated Circuit (IC) go back to 1949. German engineer Werner Jacobi filed a patent for an IC like semiconductor amplifying device showing five transistors on a common substrate in a 2-stage amplifier arrangement. -

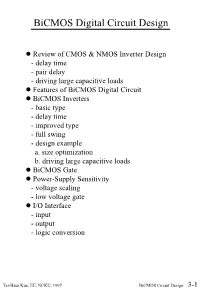

Bicmos Digital Circuit Design

BiCMOS Digital Circuit Design Review of CMOS & NMOS Inverter Design - delay time - pair delay - driving large capacitive loads Features of BiCMOS Digital Circuit BiCMOS Inverters -basic type - delay time - improved type - full swing - design example a. size optimization b. driving large capacitive loads BiCMOS Gate Power-Supply Sensitivity - voltage scaling - low voltage gate I/O Interface - input - output - logic conversion Tai-Haur Kuo, EE, NCKU, 1997 BiCMOS Circuit Design 3-1 NMOS DIGITAL CIRCUITS Static inverters Load Vout ==> V in driver A B C IDS VGS=V(1) C B A VDS (driver) VDD Vth VDD D: in in Vout VGS=V(1) VGS=V(0) V(0) V(0) V(1) V(0) V(1) Vin ― Static power dissipation during Vout=V(0) Tai-Haur Kuo, EE, NCKU, 1997 BiCMOS Circuit Design 3-2 Switching Characteristics of CMOS Inverter CMOS inverter VDD VDD T 2 V (t) o t Vin(t) T1 CL +VDD Vin(t) 0 t +VDD 0.9VDD 0.1VDD t td tf tr Trajectory of n-transistor operating point during switching in CMOS inverter Input transition : X1 X2 Output transition: X2 X3 Vds=Vgs-Vt UNSATURATED SATURATED STATE STATE X2 Vgs=VDD Ids OPERATING POINT AFTER COMPLETION OF SWITCHING INITIAL OPERATING POINT X3 X1 0 VDD Vo(t) Tai-Haur Kuo, EE, NCKU, 1997 BiCMOS Circuit Design 3-3 Rise Time and Fall Time of CMOS Inverter > Equivalent Circuit V DD VDD > Fall p-DEVICE p-DEVICE t=0 t=0 I Vin ↑ c Ic Idsn R V c C o Vo n-DEVICE L n-DEVICE CL Vo ↓ SATURATION: VVoD≥ D− Vtn 0 < VV≤ − V (a) SATURATION: 0 DD tn > Rise VDD VDD p-DEVICE p-DEVICE Idsp Rc Vin ↓ I Ic Vo ↑ t=0 c Vo Vo n-DEVICE CL n-DEVICE -

High-Performance Flexible Bicmos Electronics Based on Single-Crystal

www.nature.com/npjflexelectron ARTICLE OPEN High-performance flexible BiCMOS electronics based on single-crystal Si nanomembrane Jung-Hun Seo 1,3, Kan Zhang1, Munho Kim1, Weidong Zhou2 and Zhenqiang Ma1 In this work, we have demonstrated for the first time integrated flexible bipolar-complementary metal-oxide-semiconductor (BiCMOS) thin-film transistors (TFTs) based on a transferable single crystalline Si nanomembrane (Si NM) on a single piece of bendable plastic substrate. The n-channel, p-channel metal-oxide semiconductor field-effect transistors (N-MOSFETs & P-MOSFETs), and NPN bipolar junction transistors (BJTs) were realized together on a 340-nm thick Si NM layer with minimized processing complexity at low cost for advanced flexible electronic applications. The fabrication process was simplified by thoughtfully arranging the sequence of necessary ion implantation steps with carefully selected energies, doses and anneal conditions, and by wisely combining some costly processing steps that are otherwise separately needed for all three types of transistors. All types of TFTs demonstrated excellent DC and radio-frequency (RF) characteristics and exhibited stable transconductance and current gain under bending conditions. Overall, Si NM-based flexible BiCMOS TFTs offer great promises for high-performance and multi- functional future flexible electronics applications and is expected to provide a much larger and more versatile platform to address a broader range of applications. Moreover, the flexible BiCMOS process proposed and demonstrated here -

IEDM 2003 Conference Paper on Diode Triggered

Conference paper Diode-Triggered SCR (DTSCR) for RF-ESD Protection of BiCMOS SiGe HBTs and CMOS Ultra-Thin Gate Oxides International Electron Devices Meeting 2003 A novel Diode‐Triggered SCR (DTSCR) ESD protection element is introduced for low‐voltage application (signal, supply voltage ≤1.8V) and extremely narrow ESD design margins. Trigger voltage engineering in conjunction with fast and efficient SCR voltage clamping is applied for the protection of ultra‐sensitive circuit nodes, such as SiGe HBT bases (e.g. fTmax=45GHz in BiCMOS‐0.35u LNA input) and thin gate‐oxides (e.g. tox=1.7nm in CMOS‐ 0.09u input). SCR integration is possible based on CMOS devices or can alternatively be formed by high‐speed SiGe HBT’s. Diode-Triggered SCR (DTSCR) for RF-ESD Protection of BiCMOS SiGe HBTs and CMOS Ultra-Thin Gate Oxides Markus P.J. Mergens, Christian C. Russ**, Koen G. Verhaege, John Armer*, Phillip C. Jozwiak*, Russ Mohn*, Bart Keppens, Con Son Trinh* Sarnoff Europe, Brugse Baan 188A, B-8470 Gistel, Belgium, Europe Phone: ++49-751-3525633 - Fax: ++49-751-3525962, e-mail: [email protected] *) Sarnoff Corporation, 201 Washington Road, Princeton, NJ-08543, USA **) formerly with Sarnoff Corp., now with Infineon Technologies, Munich, Germany, Europe Abstract – A novel Diode-Triggered SCR (DTSCR) ESD protection element is introduced for low-voltage application (signal, supply voltage ≤ 1.8V) and extremely narrow ESD design margins. Trigger voltage engineering in conjunction with fast and efficient SCR voltage clamping is applied for the protection of ultra-sensitive circuit nodes, such as SiGe HBT bases (e.g. -

Foundation of Rf CMOS and Sige Bicmos Technologies

Foundation J. S. Dunn D. C. Ahlgren of rf CMOS and D. D. Coolbaugh N. B. Feilchenfeld SiGe BiCMOS G. Freeman D. R. Greenberg technologies R. A. Groves F. J. Guarı´n This paper provides a detailed description of the IBM SiGe Y. Hammad BiCMOS and rf CMOS technologies. The technologies provide A. J. Joseph high-performance SiGe heterojunction bipolar transistors (HBTs) combined with advanced CMOS technology and a L. D. Lanzerotti variety of passive devices critical for realizing an integrated S. A. St.Onge mixed-signal system-on-a-chip (SoC). The paper reviews the B. A. Orner process development and integration methodology, presents the J.-S. Rieh device characteristics, and shows how the development and K. J. Stein device selection were geared toward usage in mixed-signal IC S. H. Voldman development. P.-C. Wang M. J. Zierak S. Subbanna D. L. Harame D. A. Herman, Jr. B. S. Meyerson 1. Introduction increasing the Ge concentration and reducing the graded Silicon–germanium (SiGe) BiCMOS technology, which base width, adding carbon (C) to decrease diffusion, achieved its first manufacturing qualification in 1996, is reducing the thickness of the collector epitaxial layer, now in its fourth lithographic generation of development. and minimizing the emitter thermal cycle. In the 0.13-m This class of technology integrates high-performance generation, vertical and lateral profile scaling has led to a heterojunction bipolar transistors (HBTs) with state-of- reduction in the parasitics of the HBT, especially in the the-art CMOS technology. Key technology characteristics base, collector, and emitter resistances (RB, RC, RE) and for the four generations have been reported by IBM [1–4]. -

High Voltage Implanted RESURF P-LDMOS Using Bicmos

2132 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 40, NO. 11, NOVEMBER 1993 0.31 volts respectively at 60 A/cm2, compared with 0.32 planar junction under the drain, VBp. VBp can be derived and 0.41 Volts for devices with 1.5 pm P+ window, thus, by considering it as a punched-through diode breakdown. confirming the benefits of using submicron technology. To accurately calculate VBp,the doping profile of the bur- These JBS rectifiers exhibited reverse blocking voltages ied layer must be considered and is assumed exponential: of 30-32 V at 100”C, which is 80% of the plane parallel No = ND(0)exp (ax), where a is the impurity gradient. breakdown voltage for this doping in excellent agreement This assumption is quite effective within a range of x. with the simulations, as against the soft breakdown char- Calculating results shows that VBp increases with the in- acteristics (BV < 20 V at 100°C) of a Schottky rectifier. crease of td or the decrease of a. It implies and will further Leaka e current densities for Ti and Cr devices were 3.2 be verified by the experimental results that the model is A/cm 8 and 0.025 A/cm2 at 25 V and 100°C. Trade-off more accurate than the one assuming an abrupt buried curves between forward voltage drop and reverse leakage layer-drift region junction. current show 20X reduction in leakage current for the To use the RESURF principle, the charges in the lightly same forward drop as compared with previous reports [4], doped(drift region must be modified [3]. -

Advanced Bicmos Technology ABT Logic Enables

ABT Enables Optimal System Design SCBA001A March 1997 1 IMPORTANT NOTICE Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current. TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements. Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage (“Critical Applications”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office. In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards. TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. -

A Thz Pulse Radiator Based on PIN Diode Reverse Recovery

A THz Pulse Radiator Based on PIN Diode Reverse Recovery Sam Razavian and Aydin Babakhani Department of Electrical and Computer Engineering University of California, Los Angeles, CA 90095, USA [email protected], [email protected] Abstract — This paper presents a fully integrated oscillator-less THz pulse radiator based on reverse recovery of a PIN diode implemented using 130-nm SiGe BiCMOS technology. The chip radiates a wideband frequency comb in the THz regime through an on-chip antenna. The spacing between the THz tones can be programmed up to 10.5 GHz by tuning the frequency of the input trigger. The spectrum of the radiated frequency comb is measured from 320 GHz to 1.1 THz with 5.5-GHz spacing between the tones. The Non-Linear Q-Switching Impedance (NLQSI) technique is used for tuning the frequency tones and increasing the stability of the output stage. At a distance of 4 cm from the pulse radiator, the measured SNRs (including the losses) with 1 Hz resolution bandwidth are 51, 40, and 21 dB at 0.6, 0.8, and 1 THz, respectively with a 10-dB line-width of less than 2 Hz. With a 5.5-GHz input trigger, the total power consumption of the chip is 45 mW, with 20 mW consumed by the driver stage. Keywords — BiCMOS, frequency comb, NLQSI, on-chip antenna, PIN diode, pulse radiator, reverse recovery, THz. I. INTRODUCTION Fig. 1. (a) Structure of a PIN diode device in the SiGe 130-nm BiCMOS In recent years, broadband pulse generation techniques process, (b) Simple test-circuit to illustrate the sharp reverse recovery of a have been of great interest in the terahertz (THz) and PIN diode, (c) Voltage and current waveforms of a PIN diode in different mm-wave research due to wide range of applications, regions of operation. -

MOS Digital Integrated Circuits

EXTRA TOPICS RELATED TO x9 MOS Digital Integrated Circuits x9.1 Velocity Saturation x9.2 Subthreshold Conduction x9.3 Digital IC Technologies, Logic-Circuit Families, and Design Methodologies x9.4 Pseudo-NMOS Logic Circuits x9.5 Dynamic MOS Logic Circuits x9.6 Semiconductor Memories: Types and Architectures x9.7 Read-Only Memory x9.8 CMOS Image Sensors his supplement contains material removed from previous editions of the T textbook. These topics continue to be relevant and for this reason will be of great value to many instructors and students. The topics presented here relate to advanced topics in MOS digital integrated circuits, and can be selected to augment the materials in Chapter 17 (Sections x9.1 to x9.5) and Chapter 18 (Sections x9.6 to x9.8). x9.1 Velocity Saturation The short channels of MOSFETs fabricated in deep-submicron processes give rise to physical phenomena not present in long-channel devices, and thus to changes in the MOSFET i−v characteristics. The most important of these short-channel effects is velocity saturation. Here we refer to the drift velocity of electrons in the channel of an NMOS transistor (holes in PMOS) under the influence of the longitudinal electric field established by vDS. In our derivation of the MOSFET i−v characteristics in Chapter 5 of the eighth edition, we assumed that the velocity vn of the electrons in an n-channel device is given by Sedra/Smith/Chan Carusone/Gaudet Extra Topics for Microelectronic Circuits, Eighth Edition © Copyright Oxford Univesity Press 2020 1 vn = μnE (x9.1) where E is the electric field given by 푣 퐸 = 퐷푆 (x9.2) 퐿 The relationship in Eq. -

Design, Layout, and Testing of Sige Apds Fabricated in a Bicmos Process

UNLV Theses, Dissertations, Professional Papers, and Capstones 12-15-2018 Design, Layout, and Testing of Sige APDs Fabricated in a Bicmos Process Dane Laurence Gentry Follow this and additional works at: https://digitalscholarship.unlv.edu/thesesdissertations Part of the Electrical and Computer Engineering Commons, and the Physics Commons Repository Citation Gentry, Dane Laurence, "Design, Layout, and Testing of Sige APDs Fabricated in a Bicmos Process" (2018). UNLV Theses, Dissertations, Professional Papers, and Capstones. 3493. http://dx.doi.org/10.34917/14279623 This Thesis is protected by copyright and/or related rights. It has been brought to you by Digital Scholarship@UNLV with permission from the rights-holder(s). You are free to use this Thesis in any way that is permitted by the copyright and related rights legislation that applies to your use. For other uses you need to obtain permission from the rights-holder(s) directly, unless additional rights are indicated by a Creative Commons license in the record and/ or on the work itself. This Thesis has been accepted for inclusion in UNLV Theses, Dissertations, Professional Papers, and Capstones by an authorized administrator of Digital Scholarship@UNLV. For more information, please contact [email protected]. DESIGN, LAYOUT, AND TESTING OF SIGE APDS FABRICATED IN A BICMOS PROCESS By Dane Gentry Bachelor of Science in Electrical and Computer Engineering University of Nevada, Las Vegas 2016 A thesis submitted in partial fulfillment of the requirements for the Master of Science -

High-Performance Sige Bicmos Solutions

High-performance SiGe BiCMOS solutions Highlights Differentiated, performance-optimized offerings • Leverage a feature-rich for next-generation applications combination of active and passive The high-performance silicon germanium (SiGe) BiCMOS portfolio from devices to optimize your design GLOBALFOUNDRIES (GF) is designed to deliver the speed, performance and • Achieve hardware results you bandwidth that chips for next-generation hardware require. The silicon-proven can count on by utilizing some solutions enable you to maximize performance, integrate extensive digital and of the industry’s most accurate RF functionality and exploit an economical silicon platform. device models • Take performance to new levels SiGe HP target applications with SiGe 9HP, the highest fmax SiGe BiCMOS process in volume Highest Performance Performance/Value production today SiGe Solution 9HP 8XP 8HP 8WL 7WL • Access ongoing innovation from Applications the SiGe pioneer for differentiation that matters Automotive RADAR Automotive LiDAR Wireless infrastructure Gesture sensing Optical communications: Data center Optical communications: PON/GPON High-speed serial interfaces: USB/PCIe Test/measurement systems Aerospace and defense SiGe HP solutions Differentiating features GF’s SiGe HP solutions feature low noise figures; high linearity, gain and breakdown and operating voltages; simplified impedance matching; and excellent thermal stability. Advanced SiGe heterojunction bipolar transistors (HBTs) provide superior low-current and high-frequency performance while enabling the solutions to operate at high junction temperatures. Choose the ideal combination of performance and value for your application from a range of platforms (90 nm to 180 nm) and NPN ft performance levels (310 GHz to 60 GHz). An advanced copper (Cu) metallization feature, available in SiGe 9HP, 8XP and 8HP, enables you to take advantage of five times the current density at 100°C, or up to 25°C higher operating temperature at the same current density.