MOS Digital Integrated Circuits

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Role of Mosfets Transconductance Parameters and Threshold Voltage in CMOS Inverter Behavior in DC Mode

Preprints (www.preprints.org) | NOT PEER-REVIEWED | Posted: 28 July 2017 doi:10.20944/preprints201707.0084.v1 Article Role of MOSFETs Transconductance Parameters and Threshold Voltage in CMOS Inverter Behavior in DC Mode Milaim Zabeli1, Nebi Caka2, Myzafere Limani2 and Qamil Kabashi1,* 1 Department of Engineering Informatics, Faculty of Mechanical and Computer Engineering ([email protected]) 2 Department of Electronics, Faculty of Electrical and Computer Engineering ([email protected], [email protected]) * Correspondence: [email protected]; Tel.: +377-44-244-630 Abstract: The objective of this paper is to research the impact of electrical and physical parameters that characterize the complementary MOSFET transistors (NMOS and PMOS transistors) in the CMOS inverter for static mode of operation. In addition to this, the paper also aims at exploring the directives that are to be followed during the design phase of the CMOS inverters that enable designers to design the CMOS inverters with the best possible performance, depending on operation conditions. The CMOS inverter designed with the best possible features also enables the designing of the CMOS logic circuits with the best possible performance, according to the operation conditions and designers’ requirements. Keywords: CMOS inverter; NMOS transistor; PMOS transistor; voltage transfer characteristic (VTC), threshold voltage; voltage critical value; noise margins; NMOS transconductance parameter; PMOS transconductance parameter 1. Introduction CMOS logic circuits represent the family of logic circuits which are the most popular technology for the implementation of digital circuits, or digital systems. The small dimensions, low power of dissipation and ease of fabrication enable extremely high levels of integration (or circuits packing densities) in digital systems [1-5]. -

Logic Styles with Mosfets

Logic Styles with MOSFETs NMOS Logic One way of using MOSFET transistors to produce logic circuits uses only n-type (n-p-n) transistors, and this style is called NMOS logic (N for n-type transistors). An inverter circuit in NMOS is shown in the figure with n-p-n transistors replacing both the switch and the resistor of the inverter circuit examined earlier. The lower transistor in the circuit operates as a switch exactly as the idealised switch in the original circuit: with 5V on the Gate input, the conducting channel is created in the transistor and the “switch” is closed; with 0V on the Gate there is no channel and the transistor is non-conducting - the “switch” is open. The depletion mode transistor is produced by adding a small amount of donor material to the The upper transistor, called a depletion mode channel region of a n-p-n transistor, so that there are a small number of free electrons in the channel transistor, operates as a resistor to limit current even when there is no electric field across the flow when the “switch” is closed. This transistor is insulator. This provides a connection through the a modified n-p-n transistor that always has a transistor for all Gate voltages. The conductivity of channel present and is always conducting, although the channel is lowest (Resistance is highest) when the conductivity is low when there is 0V on the the Gate is at 0V. When the Gate is at 5V and more Gate and higher when 5V is on the Gate: see Box. -

Ionizing Radiation Effects on CMOS Imagers Manufactured in Deep Submicron Process

Ionizing Radiation Effects on CMOS Imagers Manufactured in Deep Submicron Process Vincent Goiffona, Pierre Magnana, Fr´ed´eric Bernardb, Guy Rollandb, Olivier Saint-P´ec, Nicolas Hugera and Franck Corbi`erea aUniversit´ede Toulouse, ISAE, 10 avenue E. Belin, 31055, Toulouse, France; bCNES, 18 avenue E. Belin, 31401, Toulouse, France; cEADS Astrium, 31 avenue des cosmonautes, 31402, Toulouse, France ABSTRACT We present here a study on both CMOS sensors and elementary structures (photodiodes and in-pixel MOSFETs) manufactured in a deep submicron process dedicated to imaging. We designed a test chip made of one 128×128- 3T-pixel array with 10 µm pitch and more than 120 isolated test structures including photodiodes and MOSFETs with various implants and different sizes. All these devices were exposed to ionizing radiation up to 100 krad and their responses were correlated to identify the CMOS sensor weaknesses. Characterizations in darkness and under illumination demonstrated that dark current increase is the major sensor degradation. Shallow trench isolation was identified to be responsible for this degradation as it increases the number of generation centers in photodiode depletion regions. Consequences on hardness assurance and hardening-by-design are discussed. Keywords: CMOS image sensor, CIS, APS, deep submicron technology, ionizing radiation, total dose, dark current, STI, hardening by design, RHDB 1. INTRODUCTION Ionizing radiation effects on CMOS image sensors for space and scientific applications have been studied1–6 for several years. However, the use of deep submicron technologies (DSM) has brought new behaviors7 such as enhanced gate oxide hardness or radiation induced narrow channel effect.8 These effects have been initially observed and explained on deep submicron low voltage MOS transistors dedicated to digital logic applications. -

A New Paradigm in High-Speed and High-Efficiency Silicon Photodiodes

382 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 65, NO. 2, FEBRUARY 2018 A New Paradigm in High-Speed and High-Efficiency Silicon Photodiodes for Communication—Part II: Device and VLSI Integration Challenges for Low-Dimensional Structures Hilal Cansizoglu , Member, IEEE, Aly F. Elrefaie, Fellow, IEEE, Cesar Bartolo-Perez, Toshishige Yamada, Senior Member, IEEE, Yang Gao, Ahmed S. Mayet, Mehmet F. Cansizoglu, Ekaterina Ponizovskaya Devine, Shih-Yuan Wang, Life Fellow, IEEE,and M. Saif Islam, Senior Member, IEEE (Invited Review Paper) Abstract— The ability to monolithically integrate high- Index Terms— CMOS integration, extended-reach links, speed photodetectors (PDs) with silicon (Si) can contribute high speed, high-efficiency photodetectors (PDs), high- to drastic reduction in cost. Such PDs are envisioned to performance computing, light detection and ranging, micro- be integral parts of high-speed optical interconnects in /nanostructures, single-photon detection, surface states, the future intrachip, chip-to-chip, board-to-board, rack-to- very-large-scale integration (VLSI) and ultralarge-scale inte- rack, and intra-/interdata center links. Si-based PDs are of gration (ULSI). special interest since they present the potential for mono- lithic integration with CMOS and BiCMOS very-large-scale integration and ultralarge-scale integration electronics. I. INTRODUCTION In the second part of this review, we present the efforts HE rise of distributed computing, cloud storage, social pursued by the researchers in engineering and integrating Si, SiGe alloys, and Ge PDs to CMOS and BiCMOS electron- Tmedia, and affordable hand-held devices currently allow ics and compare the performance of recently demonstrated extreme ease of transferring a plethora of data including CMOS-compatible ultrafast surface-illuminated Si PD with videos, pictures, and texts, all over the world. -

Notes for Lab 1 (Bipolar (Junction) Transistor Lab)

ECE 327: Electronic Devices and Circuits Laboratory I Notes for Lab 1 (Bipolar (Junction) Transistor Lab) 1. Introduce bipolar junction transistors • “Transistor man” (from The Art of Electronics (2nd edition) by Horowitz and Hill) – Transistors are not “switches” – Base–emitter diode current sets collector–emitter resistance – Transistors are “dynamic resistors” (i.e., “transfer resistor”) – Act like closed switch in “saturation” mode – Act like open switch in “cutoff” mode – Act like current amplifier in “active” mode • Active-mode BJT model – Collector resistance is dynamically set so that collector current is β times base current – β is assumed to be very high (β ≈ 100–200 in this laboratory) – Under most conditions, base current is negligible, so collector and emitter current are equal – β ≈ hfe ≈ hFE – Good designs only depend on β being large – The active-mode model: ∗ Assumptions: · Must have vEC > 0.2 V (otherwise, in saturation) · Must have very low input impedance compared to βRE ∗ Consequences: · iB ≈ 0 · vE = vB ± 0.7 V · iC ≈ iE – Typically, use base and emitter voltages to find emitter current. Finish analysis by setting collector current equal to emitter current. • Symbols – Arrow represents base–emitter diode (i.e., emitter always has arrow) – npn transistor: Base–emitter diode is “not pointing in” – pnp transistor: Emitter–base diode “points in proudly” – See part pin-outs for easy wiring key • “Common” configurations: hold one terminal constant, vary a second, and use the third as output – common-collector ties collector -

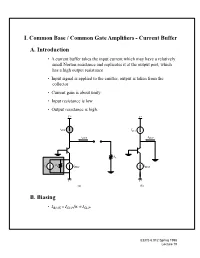

I. Common Base / Common Gate Amplifiers

I. Common Base / Common Gate Amplifiers - Current Buffer A. Introduction • A current buffer takes the input current which may have a relatively small Norton resistance and replicates it at the output port, which has a high output resistance • Input signal is applied to the emitter, output is taken from the collector • Current gain is about unity • Input resistance is low • Output resistance is high. V+ V+ i SUP ISUP iOUT IOUT RL R is S IBIAS IBIAS V− V− (a) (b) B. Biasing = /α ≈ • IBIAS ISUP ISUP EECS 6.012 Spring 1998 Lecture 19 II. Small Signal Two Port Parameters A. Common Base Current Gain Ai • Small-signal circuit; apply test current and measure the short circuit output current ib iout + = β v r gmv oib r − o ve roc it • Analysis -- see Chapter 8, pp. 507-509. • Result: –β ---------------o ≅ Ai = β – 1 1 + o • Intuition: iout = ic = (- ie- ib ) = -it - ib and ib is small EECS 6.012 Spring 1998 Lecture 19 B. Common Base Input Resistance Ri • Apply test current, with load resistor RL present at the output + v r gmv r − o roc RL + vt i − t • See pages 509-510 and note that the transconductance generator dominates which yields 1 Ri = ------ gm µ • A typical transconductance is around 4 mS, with IC = 100 A • Typical input resistance is 250 Ω -- very small, as desired for a current amplifier • Ri can be designed arbitrarily small, at the price of current (power dissipation) EECS 6.012 Spring 1998 Lecture 19 C. Common-Base Output Resistance Ro • Apply test current with source resistance of input current source in place • Note roc as is in parallel with rest of circuit g v m ro + vt it r − oc − v r RS + • Analysis is on pp. -

Precision Current Sources and Sinks Using Voltage References

Application Report SNOAA46–June 2020 Precision Current Sources and Sinks Using Voltage References Marcoo Zamora ABSTRACT Current sources and sinks are common circuits for many applications such as LED drivers and sensor biasing. Popular current references like the LM134 and REF200 are designed to make this choice easier by requiring minimal external components to cover a broad range of applications. However, sometimes the requirements of the project may demand a little more than what these devices can provide or set constraints that make them inconvenient to implement. For these cases, with a voltage reference like the TL431 and a few external components, one can create a simple current bias with high performance that is flexible to fit meet the application requirements. Current sources and sinks have been covered extensively in other Texas Instruments application notes such as SBOA046 and SLYC147, but this application note will cover other common current sources that haven't been previously discussed. Contents 1 Precision Voltage References.............................................................................................. 1 2 Current Sink with Voltage References .................................................................................... 2 3 Current Source with Voltage References................................................................................. 4 4 References ................................................................................................................... 6 List of Figures 1 Current -

MOSFET - Wikipedia, the Free Encyclopedia

MOSFET - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/MOSFET MOSFET From Wikipedia, the free encyclopedia The metal-oxide-semiconductor field-effect transistor (MOSFET, MOS-FET, or MOS FET), is by far the most common field-effect transistor in both digital and analog circuits. The MOSFET is composed of a channel of n-type or p-type semiconductor material (see article on semiconductor devices), and is accordingly called an NMOSFET or a PMOSFET (also commonly nMOSFET, pMOSFET, NMOS FET, PMOS FET, nMOS FET, pMOS FET). The 'metal' in the name (for transistors upto the 65 nanometer technology node) is an anachronism from early chips in which the gates were metal; They use polysilicon gates. IGFET is a related, more general term meaning insulated-gate field-effect transistor, and is almost synonymous with "MOSFET", though it can refer to FETs with a gate insulator that is not oxide. Some prefer to use "IGFET" when referring to devices with polysilicon gates, but most still call them MOSFETs. With the new generation of high-k technology that Intel and IBM have announced [1] (http://www.intel.com/technology/silicon/45nm_technology.htm) , metal gates in conjunction with the a high-k dielectric material replacing the silicon dioxide are making a comeback replacing the polysilicon. Usually the semiconductor of choice is silicon, but some chip manufacturers, most notably IBM, have begun to use a mixture of silicon and germanium (SiGe) in MOSFET channels. Unfortunately, many semiconductors with better electrical properties than silicon, such as gallium arsenide, do not form good gate oxides and thus are not suitable for MOSFETs. -

Lecture 12 Digital Circuits (II) MOS INVERTER CIRCUITS

Lecture 12 Digital Circuits (II) MOS INVERTER CIRCUITS Outline • NMOS inverter with resistor pull-up –The inverter • NMOS inverter with current-source pull-up • Complementary MOS (CMOS) inverter • Static analysis of CMOS inverter Reading Assignment: Howe and Sodini; Chapter 5, Section 5.4 6.012 Spring 2007 Lecture 12 1 1. NMOS inverter with resistor pull-up: Dynamics •CL pull-down limited by current through transistor – [shall study this issue in detail with CMOS] •CL pull-up limited by resistor (tPLH ≈ RCL) • Pull-up slowest VDD VDD R R VOUT: VOUT: HI LO LO HI V : VIN: IN C LO HI CL HI LO L pull-down pull-up 6.012 Spring 2007 Lecture 12 2 1. NMOS inverter with resistor pull-up: Inverter design issues Noise margins ↑⇒|Av| ↑⇒ •R ↑⇒|RCL| ↑⇒ slow switching •gm ↑⇒|W| ↑⇒ big transistor – (slow switching at input) Trade-off between speed and noise margin. During pull-up we need: • High current for fast switching • But also high incremental resistance for high noise margin. ⇒ use current source as pull-up 6.012 Spring 2007 Lecture 12 3 2. NMOS inverter with current-source pull-up I—V characteristics of current source: iSUP + 1 ISUP r i oc vSUP SUP _ vSUP Equivalent circuit models : iSUP + ISUP r r vSUP oc oc _ large-signal model small-signal model • High current throughout voltage range vSUP > 0 •iSUP = 0 for vSUP ≤ 0 •iSUP = ISUP + vSUP/ roc for vSUP > 0 • High small-signal resistance roc. 6.012 Spring 2007 Lecture 12 4 NMOS inverter with current-source pull-up Static Characteristics VDD iSUP VOUT VIN CL Inverter characteristics : iD = V 4 3 VIN VGS I + DD SUP roc 2 1 = vOUT vDS VDD (a) VOUT 1 2 3 4 VIN (b) High roc ⇒ high noise margins 6.012 Spring 2007 Lecture 12 5 PMOS as current-source pull-up I—V characteristics of PMOS: + S + VSG _ VSD G B − _ + IDp 5 V + D − V + G − V − D − ID(VSG,VSD) (a) = VSG 3.5 V 300 V = V + V = V − 1 V 250 (triode SD SG Tp SG region) V = 3 V 200 SG − IDp (µA) (saturation region) 150 = VSG 25 100 = 0, 0.5, VSG 1 V (cutoff region) V = 2 V 50 SG = VSG 1.5 V 12345 VSD (V) (b) Note: enhancement-mode PMOS has VTp <0. -

Chapter 10 Differential Amplifiers

Chapter 10 Differential Amplifiers 10.1 General Considerations 10.2 Bipolar Differential Pair 10.3 MOS Differential Pair 10.4 Cascode Differential Amplifiers 10.5 Common-Mode Rejection 10.6 Differential Pair with Active Load 1 Audio Amplifier Example An audio amplifier is constructed as above that takes a rectified AC voltage as its supply and amplifies an audio signal from a microphone. CH 10 Differential Amplifiers 2 “Humming” Noise in Audio Amplifier Example However, VCC contains a ripple from rectification that leaks to the output and is perceived as a “humming” noise by the user. CH 10 Differential Amplifiers 3 Supply Ripple Rejection vX Avvin vr vY vr vX vY Avvin Since both node X and Y contain the same ripple, their difference will be free of ripple. CH 10 Differential Amplifiers 4 Ripple-Free Differential Output Since the signal is taken as a difference between two nodes, an amplifier that senses differential signals is needed. CH 10 Differential Amplifiers 5 Common Inputs to Differential Amplifier vX Avvin vr vY Avvin vr vX vY 0 Signals cannot be applied in phase to the inputs of a differential amplifier, since the outputs will also be in phase, producing zero differential output. CH 10 Differential Amplifiers 6 Differential Inputs to Differential Amplifier vX Avvin vr vY Avvin vr vX vY 2Avvin When the inputs are applied differentially, the outputs are 180° out of phase; enhancing each other when sensed differentially. CH 10 Differential Amplifiers 7 Differential Signals A pair of differential signals can be generated, among other ways, by a transformer. -

EE 434 Lecture 2

EE 330 Lecture 6 • PU and PD Networks • Complex Logic Gates • Pass Transistor Logic • Improved Switch-Level Model • Propagation Delay Review from Last Time MOS Transistor Qualitative Discussion of n-channel Operation Source Gate Drain Drain Bulk Gate n-channel MOSFET Source Equivalent Circuit for n-channel MOSFET D D • Source assumed connected to (or close to) ground • VGS=0 denoted as Boolean gate voltage G=0 G = 0 G = 1 • VGS=VDD denoted as Boolean gate voltage G=1 • Boolean G is relative to ground potential S S This is the first model we have for the n-channel MOSFET ! Ideal switch-level model Review from Last Time MOS Transistor Qualitative Discussion of p-channel Operation Source Gate Drain Drain Bulk Gate Source p-channel MOSFET Equivalent Circuit for p-channel MOSFET D D • Source assumed connected to (or close to) positive G = 0 G = 1 VDD • VGS=0 denoted as Boolean gate voltage G=1 • VGS= -VDD denoted as Boolean gate voltage G=0 S S • Boolean G is relative to ground potential This is the first model we have for the p-channel MOSFET ! Review from Last Time Logic Circuits VDD Truth Table A B A B 0 1 1 0 Inverter Review from Last Time Logic Circuits VDD Truth Table A B C 0 0 1 0 1 0 A C 1 0 0 B 1 1 0 NOR Gate Review from Last Time Logic Circuits VDD Truth Table A B C A C 0 0 1 B 0 1 1 1 0 1 1 1 0 NAND Gate Logic Circuits Approach can be extended to arbitrary number of inputs n-input NOR n-input NAND gate gate VDD VDD A1 A1 A2 An A2 F A1 An F A2 A1 A2 An An A1 A 1 A2 F A2 F An An Complete Logic Family Family of n-input NOR gates forms -

Vlsi Design Lecture Notes B.Tech (Iv Year – I Sem) (2018-19)

VLSI DESIGN LECTURE NOTES B.TECH (IV YEAR – I SEM) (2018-19) Prepared by Dr. V.M. Senthilkumar, Professor/ECE & Ms.M.Anusha, AP/ECE Department of Electronics and Communication Engineering MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY (Autonomous Institution – UGC, Govt. of India) Recognized under 2(f) and 12 (B) of UGC ACT 1956 (Affiliated to JNTUH, Hyderabad, Approved by AICTE - Accredited by NBA & NAAC – ‘A’ Grade - ISO 9001:2015 Certified) Maisammaguda, Dhulapally (Post Via. Kompally), Secunderabad – 500100, Telangana State, India Unit -1 IC Technologies, MOS & Bi CMOS Circuits Unit -1 IC Technologies, MOS & Bi CMOS Circuits UNIT-I IC Technologies Introduction Basic Electrical Properties of MOS and BiCMOS Circuits MOS I - V relationships DS DS PMOS MOS transistor Threshold Voltage - VT figure of NMOS merit-ω0 Transconductance-g , g ; CMOS m ds Pass transistor & NMOS Inverter, Various BiCMOS pull ups, CMOS Inverter Technologies analysis and design Bi-CMOS Inverters Unit -1 IC Technologies, MOS & Bi CMOS Circuits INTRODUCTION TO IC TECHNOLOGY The development of electronics endless with invention of vaccum tubes and associated electronic circuits. This activity termed as vaccum tube electronics, afterward the evolution of solid state devices and consequent development of integrated circuits are responsible for the present status of communication, computing and instrumentation. • The first vaccum tube diode was invented by john ambrase Fleming in 1904. • The vaccum triode was invented by lee de forest in 1906. Early developments of the Integrated Circuit (IC) go back to 1949. German engineer Werner Jacobi filed a patent for an IC like semiconductor amplifying device showing five transistors on a common substrate in a 2-stage amplifier arrangement.