Technologies for Enhancing Multi-Gate Si MOSFET Performance

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Analog/Mixed-Signal Design in Finfet Technologies A.L.S

Analog/Mixed-Signal Design in FinFET Technologies A.L.S. Loke, E. Terzioglu, A.A. Kumar, T.T. Wee, K. Rim, D. Yang, B. Yu, L. Ge, L. Sun, J.L. Holland, C. Lee, S. Yang, J. Zhu, J. Choi, H. Lakdawala, Z. Chen, W.J. Chen, S. Dundigal, S.R. Knol, C.-G. Tan, S.S.C. Song, H. Dang, P.G. Drennan, J. Yuan, P.R. Chidambaram, R. Jalilizeinali, S.J. Dillen, X. Kong, and B.M. Leary [email protected] Qualcomm Technologies, Inc. September 4, 2017 CERN ESE Seminar (Based on AACD 2017) Mobile SoC Migration to FinFET Mobile SoC is now main driver for CMOS scaling • Power, Performance, Area, Cost (PPAC) considerations, cost = f(volume) • Snapdragon™ 820 - Qualcomm Technologies’ first 14nm product • Snapdragon™ 835 – World’s first 10nm product Not drawn to scale Plenty of analog/mixed-signal content Display • PLLs & DLLs Camera • Wireline I/Os Memory • Data converters BT & WLAN • Bandgap references DSP GPU • Thermal sensors • Regulators • ESD protection CPU Audio Modem SoC technology driven by logic & SRAM scaling needs due to cost Terzioglu, Qualcomm [1] Loke et al., Analog/Mixed-Signal Design in FinFET Technologies Slide 1 Outline • Fully-Depleted FinFET Basics • Technology Considerations • Design Considerations • Conclusion Loke et al., Analog/Mixed-Signal Design in FinFET Technologies Slide 2 Towards Stronger Gate Control log (I ) gate D VGS IDsat Cox I VDS S Dlin drain I source ϕs T I CB CD off lower supply lower power DIBL body VBS VGS VTsat VTlin VDD • Capacitor divider dictates source-barrier ϕs & ID • Fully-depleted finFET weakens CB, CD steeper -

Fabrication of Group IV Semiconductors on Insulator for Monolithic 3D Integration

Fabrication of Group IV Semiconductors on Insulator for Monolithic 3D Integration Ali Asadollahi Doctoral Thesis in Information and Communication Technology School of Electrical Engineering and Computer Science KTH Royal Institute of Technology Stockholm, Sweden 2017 KTH School of Electrical Engineering and Computer TRITA-EECS-AVL-2018:1 Science ISBN: 978-91-7729-658-4 SE-164 40 Stockholm SWEDEN Akademisk avhandling som med tillstånd av Kungliga Tekniska högskolan framlägges till offentlig granskning för avläggande av teknologie doktorsexamen fredagen den 16 februari 2018 klockan 10:00 i Ka-Sal C (Sal Sven-Olof Öhrvik), Electrum, Kungliga Tekniska högskolan, Kistagången 16, Kista. ©Ali Asadollahi, December 2017 Tryck: Universitetsservice US-AB, Stockholm, 2017 ii To My Parents “All the different nations in the world, despite their differences of appearance and language and the way of life, still have one thing in common, and that is what's inside in all of us. If we X-rayed the insides of different human beings, we wouldn't be able to tell from those X-rays what the person's language or background or race is.” Abbas Kiarostami iv Abstract The conventional 2D geometrical scaling of transistors is now facing many challenges in order to continue the performance enhancement while decreasing power consumption. The decrease in the device power consumption is related to the scaling of the power supply voltage (Vdd) and interconnects wiring length. In addition, monolithic three dimensional (M3D) integration in the form of vertically stacked devices, is a possible solution to increase the device density and reduce interconnect wiring length. Integrating strained germanium on insulator (sGeOI) pMOSFETs monolithically with strained silicon/silicon-germanium on insulator (sSOI/sSiGeOI) nMOSFETs can increase the device performance and packing density. -

Design of Finfet Based 1-Bit Full Adder

ISSN (Print) : 2320 – 3765 ISSN (Online): 2278 – 8875 International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering (A High Impact Factor, Monthly, Peer Reviewed Journal) Website: www.ijareeie.com Vol. 8, Issue 6, June 2019 Design of Finfet Based 1-Bit Full Adder Priti Sahu1, Ravi Tiwari2 M.Tech Scholar, Department of Electronics and Tele-Communication Engineering, Shri Shankaracharya Group of Institutions Engineering (SSGI), CSVTU, Bhilai, Chattisgarh, India Department of Electronics and Tele-Communication Engineering, Shri Shankaracharya Group of Institutions Engineering (SSGI), CSVTU, Bhilai, Chattisgarh, India ABSTRACT: This paper proposes a 1-bit Full adder using Fin type Field Effect Transistor (FinFETs) at 250nm CMOS technology. The paper is intended to reduce leakage current and leakage power, chip area, and to increase the switching speed of 1-bit Full Adder while maintaining the competitive performance with few transistors are used. In this paper, we are designed a double-gate (DG) FinFETs and extracting their transfer characteristics by using Synopsys TANNER- EDA simulation tool. We investigate the use of Double Gate FinFET technology which provides low leakage and high- performance operation by utilizing high speed and low threshold voltage transistors for logic cells. Which show that it is particularly effective in sub threshold circuits and can eliminate performance variations with Low power. A 22ns access time and frequency 0.045GHz provide 250nm CMOS process technology with 5V power supply is employed to carry out 1-bit Full Adder of speed, power and reliability compared to Metal Oxide Semiconductor Field Effect Transistor (MOSFET) based full adder designs. Hence FinFET is a promising candidate and is a better replacement for MOSFET. -

Fundamentals of Nanoelectronics (Fone)

ESF EUROCORES Programme Fundamentals of NanoElectronics (FoNE) Highlights European Science Foundation (ESF) Physical and Engineering Sciences (PESC) The European Science Foundation (ESF) is an The Physical and Engineering Sciences are key drivers independent, non-governmental organisation, the for research and innovation, providing fundamental members of which are 78 national funding agencies, insights and creating new applications for mankind. research performing agencies, academies and learned The goal of the ESF Standing Committee for Physical societies from 30 countries. and Engineering Sciences (PESC) is to become the The strength of ESF lies in its influential membership pan-European platform for innovative research and and in its ability to bring together the different domains competitive new ideas while addressing societal of European science in order to meet the challenges of issues in a more effective and sustainable manner. the future. The Committee is a unique cross-disciplinary Since its establishment in 1974, ESF, which has its group, with networking activities comprising a good headquarters in Strasbourg with offices in Brussels mix of experimental and theoretical approaches. and Ostend, has assembled a host of organisations It distinguishes itself by focusing on fundamental that span all disciplines of science, to create a research and engineering. PESC covers the following common platform for cross-border cooperation in broad spectrum of fields: chemistry, mathematics, Europe. informatics and the computer sciences, physics, ESF is dedicated to promoting collaboration in fundamental engineering sciences and materials scientific research, funding of research and science sciences. policy across Europe. Through its activities and instruments ESF has made major contributions to science in a global context. -

Three-Dimensional Integrated Circuit Design: EDA, Design And

Integrated Circuits and Systems Series Editor Anantha Chandrakasan, Massachusetts Institute of Technology Cambridge, Massachusetts For other titles published in this series, go to http://www.springer.com/series/7236 Yuan Xie · Jason Cong · Sachin Sapatnekar Editors Three-Dimensional Integrated Circuit Design EDA, Design and Microarchitectures 123 Editors Yuan Xie Jason Cong Department of Computer Science and Department of Computer Science Engineering University of California, Los Angeles Pennsylvania State University [email protected] [email protected] Sachin Sapatnekar Department of Electrical and Computer Engineering University of Minnesota [email protected] ISBN 978-1-4419-0783-7 e-ISBN 978-1-4419-0784-4 DOI 10.1007/978-1-4419-0784-4 Springer New York Dordrecht Heidelberg London Library of Congress Control Number: 2009939282 © Springer Science+Business Media, LLC 2010 All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden. The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights. Printed on acid-free paper Springer is part of Springer Science+Business Media (www.springer.com) Foreword We live in a time of great change. -

Memristive-Finfet Circuits for FFT & Vedic Multiplication

Special Issue - 2016 International Journal of Engineering Research & Technology (IJERT) ISSN: 2278-0181 NCETET - 2016 Conference Proceedings Threshold Logic Computing: Memristive-FinFET Circuits for FFT & Vedic Multiplication Nasria A Divya R PG Scholar Assistant Professor Applied Electronics and instrumentation Electronics and Communication Younus College of Engineering and Technology Younus College of Engineering and Technology Kollam, India Kollam, India Abstract—Threshold logic computing is the simplest kind of expensive because of their area, power, and delay overhead. computing units used to build artificial neural networks. Brain In the beginning stage, threshold gates have been mimic circuits can be developed electronically in different ways. implemented using CMOS devices, Single Electron But using Memristive Threshold Logic (MTL) cells have various Transistors and Monostable-Bistable Logic Elements and advantages than Logic gates. MTL cell is used for designing FFT resonant tunnelling diodes. Capacitor-based Threshold Logic computing useful for signal processing applications and Vedic addition and multiplications for efficient Arithmetic Logic unit gates (CTL) are implemented using capacitors as weights design. MTL cell is the basic cell which consist of two parts: along with CMOS-based comparator circuits. In CMOS CTL Memristor based input voltage averaging circuits and an output gates, sum of weighted input voltage is compared with a threshold circuit. The threshold circuit is the combination of fixed reference voltage, and based on this comparison, a Op-amp and FinFET circuit. FinFET circuits indicate much logical output is produced. CTL gates are used for 2D image lower power consumption, lower chip area and operates at filtering in. These CTL gates have many advantages such as lower voltages. -

Graphene Field-Effect Transistor Array with Integrated Electrolytic Gates Scaled to 200 Mm

Graphene field-effect transistor array with integrated electrolytic gates scaled to 200 mm N C S Vieira1,3, J Borme1, G Machado Jr.1, F Cerqueira2, P P Freitas1, V Zucolotto3, N M R Peres2 and P Alpuim1,2 1INL - International Iberian Nanotechnology Laboratory, 4715-330, Braga, Portugal. 2CFUM - Center of Physics of the University of Minho, 4710-057, Braga, Portugal. 3IFSC - São Carlos Institute of Physics, University of São Paulo, 13560-970, São Carlos-SP, Brazil E-mail: [email protected] Abstract Ten years have passed since the beginning of graphene research. In this period we have witnessed breakthroughs both in fundamental and applied research. However, the development of graphene devices for mass production has not yet reached the same level of progress. The architecture of graphene field-effect transistors (FET) has not significantly changed, and the integration of devices at the wafer scale has generally not been sought. Currently, whenever an electrolyte-gated FET (EGFET) is used, an external, cumbersome, out-of-plane gate electrode is required. Here, an alternative architecture for graphene EGFET is presented. In this architecture, source, drain, and gate are in the same plane, eliminating the need for an external gate electrode and the use of an additional reservoir to confine the electrolyte inside the transistor active zone. This planar structure with an integrated gate allows for wafer-scale fabrication of high-performance graphene EGFETs, with carrier mobility up to 1800 cm2 V-1 s-1. As a proof-of principle, a chemical sensor was achieved. It is shown that the sensor can discriminate between saline solutions of different concentrations. -

Engineered Carbon Nanotubes and Graphene for Nanoelectronics And

Engineered Carbon Nanotubes and Graphene for Nanoelectronics and Nanomechanics E. H. Yang Stevens Institute of Technology, Castle Point on Hudson, Hoboken, NJ, USA, 07030 ABSTRACT We are exploring nanoelectronic engineering areas based on low dimensional materials, including carbon nanotubes and graphene. Our primary research focus is investigating carbon nanotube and graphene architectures for field emission applications, energy harvesting and sensing. In a second effort, we are developing a high-throughput desktop nanolithography process. Lastly, we are studying nanomechanical actuators and associated nanoscale measurement techniques for re-configurable arrayed nanostructures with applications in antennas, remote detectors, and biomedical nanorobots. The devices we fabricate, assemble, manipulate, and characterize potentially have a wide range of applications including those that emerge as sensors, detectors, system-on-a-chip, system-in-a-package, programmable logic controls, energy storage systems, and all-electronic systems. INTRODUCTION A key attribute of modern warfare is the use of advanced electronics and information technologies. The ability to process, analyze, distribute and act upon information from sensors and other data at very high- speeds has given the US military unparalleled technological superiority and agility in the battlefield. While recent advances in materials and processing methods have led to the development of faster processors and high-speed devices, it is anticipated that future technological breakthroughs in these areas will increasingly be driven by advances in nanoelectronics. A vital enabler in generating significant improvements in nanoelectronics is graphene, a recently discovered nanoelectronic material. The outstanding electrical properties of both carbon nanotubes (CNTs) [1] and graphene [2] make them exceptional candidates for the development of novel electronic devices. -

Mobility Enhancement of Strained Si Transistors by Transfer Printing on Plastic Substrates

OPEN NPG Asia Materials (2016) 8, e256; doi:10.1038/am.2016.31 www.nature.com/am ORIGINAL ARTICLE Mobility enhancement of strained Si transistors by transfer printing on plastic substrates Wonho Lee1, Yun Hwangbo2, Jae-Hyun Kim2 and Jong-Hyun Ahn1 Strain engineering has been utilized to overcome the limitation of geometric scaling in Si-based thin-film transistor (TFT) technology by significantly improving carrier mobility. However, current strain engineering methods have several drawbacks: they generate atomic defects in the interface between Si and strain inducers, they involve high-cost epitaxial depositions and they are difficult to apply to flexible electronics with plastic substrates. Here, we report the formation of a strained Si membrane with oxidation-induced residual strain by releasing a host Si substrate of a silicon-on-insulator (SOI) wafer. The construction of the suspended Si/SiO2 structures induces 40.5% tensile strain on the top Si membrane. The fabricated TFTs with strained Si channels are transferred onto plastics using a roll-based transfer technique, and they exhibit a mobility enhancement factor of 1.2–1.4 compared with an unstrained Si TFT. NPG Asia Materials (2016) 8, e256; doi:10.1038/am.2016.31; published online 25 March 2016 INTRODUCTION substrates. A strained Si nanomembrane is fabricated by releasing the A critical path in the development of advanced silicon electronics bilayer of Si and SiO2 from the host Si layer of a silicon-on-insulator involves a reduction in the dimensions of device geometries such as (SOI) wafer. The oxidation-induced compressive strain in the SiO2 the channel thickness, channel length and gate dielectric thickness to layer of the SOI wafer is activated by forming a suspended structure increase the operating speed with lower power consumption and via the etching of the host Si that leads to planar expansion of the 1–4 the density of integration in circuits. -

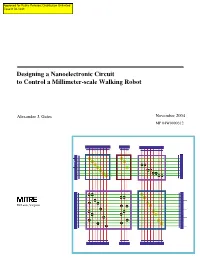

Designing a Nanoelectronic Circuit to Control a Millimeter-Scale Walking Robot

Designing a Nanoelectronic Circuit to Control a Millimeter-scale Walking Robot Alexander J. Gates November 2004 MP 04W0000312 McLean, Virginia Designing a Nanoelectronic Circuit to Control a Millimeter-scale Walking Robot Alexander J. Gates November 2004 MP 04W0000312 MITRE Nanosystems Group e-mail: [email protected] WWW: http://www.mitre.org/tech/nanotech Sponsor MITRE MSR Program Project No. 51MSR89G Dept. W809 Approved for public release; distribution unlimited. Copyright © 2004 by The MITRE Corporation. All rights reserved. Gates, Alexander Abstract A novel nanoelectronic digital logic circuit was designed to control a millimeter-scale walking robot using a nanowire circuit architecture. This nanoelectronic circuit has a number of benefits, including extremely small size and relatively low power consumption. These make it ideal for controlling microelectromechnical systems (MEMS), such as a millirobot. Simulations were performed using a SPICE circuit simulator, and unique device models were constructed in this research to assess the function and integrity of the nanoelectronic circuit’s output. It was determined that the output signals predicted for the nanocircuit by these simulations meet the requirements of the design, although there was a minor signal stability issue. A proposal is made to ameliorate this potential problem. Based on this proposal and the results of the simulations, the nanoelectronic circuit designed in this research could be used to begin to address the broader issue of further miniaturizing circuit-micromachine systems. i Gates, Alexander I. Introduction The purpose of this paper is to describe the novel nanoelectronic digital logic circuit shown in Figure 1, which has been designed by this author to control a millimeter-scale walking robot. -

Advanced MOSFET Structures and Processes for Sub-7 Nm CMOS Technologies

Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies By Peng Zheng A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences in the Graduate Division of the University of California, Berkeley Committee in charge: Professor Tsu-Jae King Liu, Chair Professor Laura Waller Professor Costas J. Spanos Professor Junqiao Wu Spring 2016 © Copyright 2016 Peng Zheng All rights reserved Abstract Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies by Peng Zheng Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences University of California, Berkeley Professor Tsu-Jae King Liu, Chair The remarkable proliferation of information and communication technology (ICT) – which has had dramatic economic and social impact in our society – has been enabled by the steady advancement of integrated circuit (IC) technology following Moore’s Law, which states that the number of components (transistors) on an IC “chip” doubles every two years. Increasing the number of transistors on a chip provides for lower manufacturing cost per component and improved system performance. The virtuous cycle of IC technology advancement (higher transistor density lower cost / better performance semiconductor market growth technology advancement higher transistor density etc.) has been sustained for 50 years. Semiconductor industry experts predict that the pace of increasing transistor density will slow down dramatically in the sub-20 nm (minimum half-pitch) regime. Innovations in transistor design and fabrication processes are needed to address this issue. The FinFET structure has been widely adopted at the 14/16 nm generation of CMOS technology. -

State-Of-The-Art and Future of Silicon on Insulator Technologies, Materials, and Devices Sorin Cristoloveanu *

Microelectronics Reliability 40 (2000) 771±777 www.elsevier.com/locate/microrel State-of-the-art and future of silicon on insulator technologies, materials, and devices Sorin Cristoloveanu * Laboratoire de Physique des Composants a Semiconducteurs (UA±CNRS & INPG), ENSERG, B.P. 257, 38016 Grenoble Cedex 1, France Abstract The context of SOI technologies is brie¯y presented in terms of wafer fabrication, con®guration/performance of typical SOI devices, and operation mechanisms in partially and fully depleted MOSFETs. The future of SOI is ten- tatively explored, by discussing the further scalability of SOI transistors as well as the innovating architectures proposed for the ultimate generations of SOI transistors. Ó 2000 Elsevier Science Ltd. All rights reserved. 1. Introduction 2. Synthesis of SOI wafers Silicon on insulator (SOI) technology, originally de- In the last 20 years, a variety of SOI structures have veloped for the niche of radiation-hard circuits, has ex- been conceived with the aim of separating, using a perienced three decades of continuous improvement in buried oxide (BOX), the active device volume from the material quality, device physics, and processing. Re- Si substrate. cently, SOI has joined the microelectronics roadmap: Silicon-on-sapphire (SOS, Fig. 1a1) is fabricated by SOI circuits are indeed attractive because of their epitaxial growth of a Si ®lm on Al2O3. The electrical enhanced performance (higher speed, lower power- properties may suer from lateral stress, in-depth inho- voltage) and scalability. mogeneity of the ®lm, and defective transition layer at The aim of this article is to provide a synthetic view the interface [1,2].