Lecture 14 FET Current and Voltage Sources and Current Mirrors The

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Notes for Lab 1 (Bipolar (Junction) Transistor Lab)

ECE 327: Electronic Devices and Circuits Laboratory I Notes for Lab 1 (Bipolar (Junction) Transistor Lab) 1. Introduce bipolar junction transistors • “Transistor man” (from The Art of Electronics (2nd edition) by Horowitz and Hill) – Transistors are not “switches” – Base–emitter diode current sets collector–emitter resistance – Transistors are “dynamic resistors” (i.e., “transfer resistor”) – Act like closed switch in “saturation” mode – Act like open switch in “cutoff” mode – Act like current amplifier in “active” mode • Active-mode BJT model – Collector resistance is dynamically set so that collector current is β times base current – β is assumed to be very high (β ≈ 100–200 in this laboratory) – Under most conditions, base current is negligible, so collector and emitter current are equal – β ≈ hfe ≈ hFE – Good designs only depend on β being large – The active-mode model: ∗ Assumptions: · Must have vEC > 0.2 V (otherwise, in saturation) · Must have very low input impedance compared to βRE ∗ Consequences: · iB ≈ 0 · vE = vB ± 0.7 V · iC ≈ iE – Typically, use base and emitter voltages to find emitter current. Finish analysis by setting collector current equal to emitter current. • Symbols – Arrow represents base–emitter diode (i.e., emitter always has arrow) – npn transistor: Base–emitter diode is “not pointing in” – pnp transistor: Emitter–base diode “points in proudly” – See part pin-outs for easy wiring key • “Common” configurations: hold one terminal constant, vary a second, and use the third as output – common-collector ties collector -

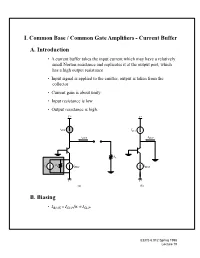

I. Common Base / Common Gate Amplifiers

I. Common Base / Common Gate Amplifiers - Current Buffer A. Introduction • A current buffer takes the input current which may have a relatively small Norton resistance and replicates it at the output port, which has a high output resistance • Input signal is applied to the emitter, output is taken from the collector • Current gain is about unity • Input resistance is low • Output resistance is high. V+ V+ i SUP ISUP iOUT IOUT RL R is S IBIAS IBIAS V− V− (a) (b) B. Biasing = /α ≈ • IBIAS ISUP ISUP EECS 6.012 Spring 1998 Lecture 19 II. Small Signal Two Port Parameters A. Common Base Current Gain Ai • Small-signal circuit; apply test current and measure the short circuit output current ib iout + = β v r gmv oib r − o ve roc it • Analysis -- see Chapter 8, pp. 507-509. • Result: –β ---------------o ≅ Ai = β – 1 1 + o • Intuition: iout = ic = (- ie- ib ) = -it - ib and ib is small EECS 6.012 Spring 1998 Lecture 19 B. Common Base Input Resistance Ri • Apply test current, with load resistor RL present at the output + v r gmv r − o roc RL + vt i − t • See pages 509-510 and note that the transconductance generator dominates which yields 1 Ri = ------ gm µ • A typical transconductance is around 4 mS, with IC = 100 A • Typical input resistance is 250 Ω -- very small, as desired for a current amplifier • Ri can be designed arbitrarily small, at the price of current (power dissipation) EECS 6.012 Spring 1998 Lecture 19 C. Common-Base Output Resistance Ro • Apply test current with source resistance of input current source in place • Note roc as is in parallel with rest of circuit g v m ro + vt it r − oc − v r RS + • Analysis is on pp. -

Precision Current Sources and Sinks Using Voltage References

Application Report SNOAA46–June 2020 Precision Current Sources and Sinks Using Voltage References Marcoo Zamora ABSTRACT Current sources and sinks are common circuits for many applications such as LED drivers and sensor biasing. Popular current references like the LM134 and REF200 are designed to make this choice easier by requiring minimal external components to cover a broad range of applications. However, sometimes the requirements of the project may demand a little more than what these devices can provide or set constraints that make them inconvenient to implement. For these cases, with a voltage reference like the TL431 and a few external components, one can create a simple current bias with high performance that is flexible to fit meet the application requirements. Current sources and sinks have been covered extensively in other Texas Instruments application notes such as SBOA046 and SLYC147, but this application note will cover other common current sources that haven't been previously discussed. Contents 1 Precision Voltage References.............................................................................................. 1 2 Current Sink with Voltage References .................................................................................... 2 3 Current Source with Voltage References................................................................................. 4 4 References ................................................................................................................... 6 List of Figures 1 Current -

Lecture 12 Digital Circuits (II) MOS INVERTER CIRCUITS

Lecture 12 Digital Circuits (II) MOS INVERTER CIRCUITS Outline • NMOS inverter with resistor pull-up –The inverter • NMOS inverter with current-source pull-up • Complementary MOS (CMOS) inverter • Static analysis of CMOS inverter Reading Assignment: Howe and Sodini; Chapter 5, Section 5.4 6.012 Spring 2007 Lecture 12 1 1. NMOS inverter with resistor pull-up: Dynamics •CL pull-down limited by current through transistor – [shall study this issue in detail with CMOS] •CL pull-up limited by resistor (tPLH ≈ RCL) • Pull-up slowest VDD VDD R R VOUT: VOUT: HI LO LO HI V : VIN: IN C LO HI CL HI LO L pull-down pull-up 6.012 Spring 2007 Lecture 12 2 1. NMOS inverter with resistor pull-up: Inverter design issues Noise margins ↑⇒|Av| ↑⇒ •R ↑⇒|RCL| ↑⇒ slow switching •gm ↑⇒|W| ↑⇒ big transistor – (slow switching at input) Trade-off between speed and noise margin. During pull-up we need: • High current for fast switching • But also high incremental resistance for high noise margin. ⇒ use current source as pull-up 6.012 Spring 2007 Lecture 12 3 2. NMOS inverter with current-source pull-up I—V characteristics of current source: iSUP + 1 ISUP r i oc vSUP SUP _ vSUP Equivalent circuit models : iSUP + ISUP r r vSUP oc oc _ large-signal model small-signal model • High current throughout voltage range vSUP > 0 •iSUP = 0 for vSUP ≤ 0 •iSUP = ISUP + vSUP/ roc for vSUP > 0 • High small-signal resistance roc. 6.012 Spring 2007 Lecture 12 4 NMOS inverter with current-source pull-up Static Characteristics VDD iSUP VOUT VIN CL Inverter characteristics : iD = V 4 3 VIN VGS I + DD SUP roc 2 1 = vOUT vDS VDD (a) VOUT 1 2 3 4 VIN (b) High roc ⇒ high noise margins 6.012 Spring 2007 Lecture 12 5 PMOS as current-source pull-up I—V characteristics of PMOS: + S + VSG _ VSD G B − _ + IDp 5 V + D − V + G − V − D − ID(VSG,VSD) (a) = VSG 3.5 V 300 V = V + V = V − 1 V 250 (triode SD SG Tp SG region) V = 3 V 200 SG − IDp (µA) (saturation region) 150 = VSG 25 100 = 0, 0.5, VSG 1 V (cutoff region) V = 2 V 50 SG = VSG 1.5 V 12345 VSD (V) (b) Note: enhancement-mode PMOS has VTp <0. -

Chapter 10 Differential Amplifiers

Chapter 10 Differential Amplifiers 10.1 General Considerations 10.2 Bipolar Differential Pair 10.3 MOS Differential Pair 10.4 Cascode Differential Amplifiers 10.5 Common-Mode Rejection 10.6 Differential Pair with Active Load 1 Audio Amplifier Example An audio amplifier is constructed as above that takes a rectified AC voltage as its supply and amplifies an audio signal from a microphone. CH 10 Differential Amplifiers 2 “Humming” Noise in Audio Amplifier Example However, VCC contains a ripple from rectification that leaks to the output and is perceived as a “humming” noise by the user. CH 10 Differential Amplifiers 3 Supply Ripple Rejection vX Avvin vr vY vr vX vY Avvin Since both node X and Y contain the same ripple, their difference will be free of ripple. CH 10 Differential Amplifiers 4 Ripple-Free Differential Output Since the signal is taken as a difference between two nodes, an amplifier that senses differential signals is needed. CH 10 Differential Amplifiers 5 Common Inputs to Differential Amplifier vX Avvin vr vY Avvin vr vX vY 0 Signals cannot be applied in phase to the inputs of a differential amplifier, since the outputs will also be in phase, producing zero differential output. CH 10 Differential Amplifiers 6 Differential Inputs to Differential Amplifier vX Avvin vr vY Avvin vr vX vY 2Avvin When the inputs are applied differentially, the outputs are 180° out of phase; enhancing each other when sensed differentially. CH 10 Differential Amplifiers 7 Differential Signals A pair of differential signals can be generated, among other ways, by a transformer. -

Transistor Current Source

PY 452 Advanced Physics Laboratory Hans Hallen Electronics Labs One electronics project should be completed. If you do not know what an op-amp is, do either lab 2 or lab 3. A written report is due, and should include a discussion of the circuit with inserted equations and plots as appropriate to substantiate the words and show that the measurements were taken. The report should not consist of the numbered items below and short answers, but should be one coherent discussion that addresses most of the issues brought out in the numbered items below. This is not an electronics course. Familiarity with electronics concepts such as input and output impedance, noise sources and where they matter, etc. are important in the lab AND SHOULD APPEAR IN THE REPORT. The objective of this exercise is to gain familiarity with these concepts. Electronics Lab #1 Transistor Current Source Task: Build and test a transistor current source, , +V with your choice of current (but don't exceed the transistor, power supply, or R ratings). R1 Rload You may wish to try more than one current. (1) Explain your choice of R1, R2, and Rsense. VCE (a) In particular, use the 0.6 V drop of VBE - rule for current flow to calculate I in R2 VBE Rsense terms of Rsense, and the Ic/Ib rule to estimate Ib hence the values of R1&R2. (2) Try your source over a wide range of Rload values, plot Iload vs. Rload and interpret. You may find it instructive to look at VBE and VCE with a floating (neither side grounded) multimeter. -

Current Source & Source Transformation Notes

EE301 – CURRENT SOURCES / SOURCE CONVERSION Learning Objectives a. Analyze a circuit consisting of a current source, voltage source and resistors b. Convert a current source and a resister into an equivalent circuit consisting of a voltage source and a resistor c. Evaluate a circuit that contains several current sources in parallel Ideal sources An ideal source is an active element that provides a specified voltage or current that is completely independent of other circuit elements. DC Voltage DC Current Source Source Constant Current Sources The voltage across the current source (Vs) is dependent on how other components are connected to it. Additionally, the current source voltage polarity does not have to follow the current source’s arrow! 1 Example: Determine VS in the circuit shown below. Solution: 2 Example: Determine VS in the circuit shown above, but with R2 replaced by a 6 k resistor. Solution: 1 8/31/2016 EE301 – CURRENT SOURCES / SOURCE CONVERSION 3 Example: Determine I1 and I2 in the circuit shown below. Solution: 4 Example: Determine I1 and VS in the circuit shown below. Solution: Practical voltage sources A real or practical source supplies its rated voltage when its terminals are not connected to a load (open- circuited) but its voltage drops off as the current it supplies increases. We can model a practical voltage source using an ideal source Vs in series with an internal resistance Rs. Practical current source A practical current source supplies its rated current when its terminals are short-circuited but its current drops off as the load resistance increases. We can model a practical current source using an ideal current source in parallel with an internal resistance Rs. -

Class 08: NMOS, Pseudo-NMOS

Class 08: NMOS, Pseudo-NMOS Topics: •02 NMOS Logic Gates •03 NMOS Logic Gates •04 Pseudo-NMOS •05 Pseudo-NMOS •06 Transistor Equivalency Dr. Joseph Elias; Dr. Andrew Mason 1 Class 08: NMOS, Pseudo-NMOS NMOS (Martin c. 1) § nMOS Inverter with resistive load § nMOS Inverter with depletion load Depletion nMOS, Vtn < 0 always ON for VGS = 0 § switch level model W/L Q1 > W/L Q2 so Q1 can “pull down” Vout § nMOS NOR gate c = a+b (a) NMOS off (b) NMOS on want to realize resistor with a transistor § nMOS NAND gate § Including transistor resistance c = ab rds º channel resistance RL >> rds so output close to 0V Dr. Joseph Elias; Dr. Andrew Mason 2 Class 08: NMOS, Pseudo-NMOS NMOS (Martin c. 1) • General nMOS schematic Examples: depletion-load nMOS logic – single load transistor – parallel and series nMOS transistor to complete the compliment of the desired function i.e., they determine when the output is low “0” rather than high “1” Dr. Joseph Elias; Dr. Andrew Mason 3 Class 08: NMOS, Pseudo-NMOS Pseudo-NMOS (Martin c. 4) •NMOS Common-Source Amplifier with •Pseudo-NMOS inverter with PMOS load current sourrce load and load capacitor •Choose W/L so that: •Choose Vbias in between VDD and ground Q2 always on since |Vgs| > |Vtp| Q2 in saturation if (for VDD=3.3) |Vds| > |Veff| > |Vgs| – |Vt| VDD – Vout > |Vgs| - |Vt| Vout < VDD - |Vgs| + |Vt| Vout < 1.65 + Vt < 2.45 Q1 in saturation if Vgs = Vin > Vt Vds > Veff > Vgs – Vt => •Current-source realized with a PMOS transistor Vout > Vin - Vt •Power Dissipation: Veff = Vgs - Vt output low (Vin is high): P = IL * VDD Vds = Vgs + Vdg at saturation, Vdg=-Vt output high (Vin is low): P = 0 Valid if: average static dissipation: P = ½ * IL * VDD Veff = |Vds-sat| > |Vgs| - |Vtp| -want drain at least Vt from gate Dr. -

AN-1530 Application Note

AN-1530 APPLICATION NOTE One Technology Way • P. O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com High Precision, Low Cost Current Sources Using the AD8276 Difference Amplifier and the AD8603 Op Amp CIRCUIT FUNCTION AND BENEFITS integrated current source, and the AD7794 is a high resolution, Current sources are widely used in industrial, communication, Σ-Δ, analog-to-digital converter (ADC) with two integrated and other equipment for sensor excitation and machine to current sources. For high currents, external MOSFETs or machine communication. For example, the 4 mA to 20 mA loop transistors are generally required. is widely used in process control equipment. Current sources using the low power AD8276 difference amplifier Programmable current sources can be built using a digital-to- and the AD8603 op amp are affordable, flexible, and is small in analog converter (DAC), op amp or difference amplifier, and size. Performance characteristics such as initial error, temperature matched resistors. Low value current sources can be integrated drift, and power dissipation make the AD8276 and the AD8603 into low output current sources or amplifiers. For example, the ideal candidates. AD8290 is an instrumentation amplifier with a single, +5V +VS 7 AD8276 RF1 40kΩ SENSE 5 –IN RG1 40kΩ 2 T1 OUT 6 RG2 40kΩ V V 3 OUT REF +IN RF2 40kΩ REF +5V R1 1 3 5 V 1 LOAD 4 4 AD8603 I –VS 2 O RLOAD 08358-001 Figure 1. Current Source Using the AD8276 Difference Amplifier and the AD8603 Op Amp (Simplified Schematic) Rev. -

Field Effect Transistors

Introduction to Nanoelectronics Part 5. Field Effect Transistors Field Effect transistors (FETs) are the backbone of the electronics industry. The remarkable progress of electronics over the last few decades is due in large part to advances in FET technology, especially their miniaturization, which has improved speed, decreased power consumption and enabled the fabrication of more complex circuits. Consequently, engineers have worked to roughly double the number of FETs in a complex chip such as an integrated circuit every 1.5-2 years; see Fig. 1 in the Introduction. This trend, known now as Moore‟s law, was first noted in 1965 by Gordon Moore, an Intel engineer. We will address Moore‟s law and its limits specifically at the end of the class. But for now, we simply note that FETs are already small and getting smaller. Intel‟s latest processors have a source-drain separation of approximately 65nm. In this section we will first look at the simplest FETs: molecular field effect transistors. We will use these devices to explain field effect switching. Then, we will consider ballistic quantum wire FETs, ballistic quantum well FETs and ultimately non-ballistic macroscopic FETs. (i) Molecular FETs The architecture of a molecular field effect transistor is shown in Fig. 5.1. The molecule bridges the source and drain contact providing a channel for electrons to flow. There is also a third terminal positioned close to the conductor. This contact is known as the gate, as it is intended to control the flow of charge through the channel. The gate does not inject charge directly. -

Electrical Engineering Dictionary

ratio of the power per unit solid angle scat- tered in a specific direction of the power unit area in a plane wave incident on the scatterer R from a specified direction. RADHAZ radiation hazards to personnel as defined in ANSI/C95.1-1991 IEEE Stan- RS commonly used symbol for source dard Safety Levels with Respect to Human impedance. Exposure to Radio Frequency Electromag- netic Fields, 3 kHz to 300 GHz. RT commonly used symbol for transfor- mation ratio. radial basis function network a fully R-ALOHA See reservation ALOHA. connected feedforward network with a sin- gle hidden layer of neurons each of which RL Typical symbol for load resistance. computes a nonlinear decreasing function of the distance between its received input and Rabi frequency the characteristic cou- a “center point.” This function is generally pling strength between a near-resonant elec- bell-shaped and has a different center point tromagnetic field and two states of a quan- for each neuron. The center points and the tum mechanical system. For example, the widths of the bell shapes are learned from Rabi frequency of an electric dipole allowed training data. The input weights usually have transition is equal to µE/hbar, where µ is the fixed values and may be prescribed on the electric dipole moment and E is the maxi- basis of prior knowledge. The outputs have mum electric field amplitude. In a strongly linear characteristics, and their weights are driven 2-level system, the Rabi frequency is computed during training. equal to the rate at which population oscil- lates between the ground and excited states. -

Module 4-5-Differential Amplifiers

EE105 – Fall 2015 Microelectronic Devices and Circuits Module 4-5: DifferentialAmplifiers Prof. Ming C. Wu [email protected] 511 Sutardja Dai Hall (SDH) Differential & Common Mode Signals Why Differential? • Differential circuits are much less sensitive to noises and interferences • Differential configuration enables us to bias amplifiers and connect multiple stages without using coupling or bypass capacitors • Differential amplifiers are widely used in IC’s – Excellent matching of transistors, which is critical for differential circuits – Differential circuits require more transistorsà not an issue for IC Neural Recording An array of electrodes is implanted in the motor cortex and senses extracellular signals that include firing from nearbyneurons The propagation of signals from neuron to neuron is called an Action Potential, which is analogous to a digital “pulse” Extracellular Neuronal Signals oltage V Local Field Potential (LFP) 1Hz-300Hz;; 10µV-1mV Action Potential “spikes” 300Hz- Time 10kHz 10µV-1mV l The goal of a neural recording device is to record - the small amplitude neural signals and pick out the meaningful signals from the “noise”. l These signals are then decoded to create trajectories, movements, and speeds for controlling prostheses, computers, etc. 60Hz and Other Interferers 60 Hz Action Noise Potentials • In reality, the tiny signals recorded from the brain can get corrupted by numerous interferers. • Ambient 60Hz noise couples into electrical signals in and on the body • Motion can cause voltage artifacts