AN-1001 Understanding Power MOSFET Parameters

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Imperial College London Department of Physics Graphene Field Effect

Imperial College London Department of Physics Graphene Field Effect Transistors arXiv:2010.10382v2 [cond-mat.mes-hall] 20 Jul 2021 By Mohamed Warda and Khodr Badih 20 July 2021 Abstract The past decade has seen rapid growth in the research area of graphene and its application to novel electronics. With Moore's law beginning to plateau, the need for post-silicon technology in industry is becoming more apparent. Moreover, exist- ing technologies are insufficient for implementing terahertz detectors and receivers, which are required for a number of applications including medical imaging and secu- rity scanning. Graphene is considered to be a key potential candidate for replacing silicon in existing CMOS technology as well as realizing field effect transistors for terahertz detection, due to its remarkable electronic properties, with observed elec- tronic mobilities reaching up to 2 × 105 cm2 V−1 s−1 in suspended graphene sam- ples. This report reviews the physics and electronic properties of graphene in the context of graphene transistor implementations. Common techniques used to syn- thesize graphene, such as mechanical exfoliation, chemical vapor deposition, and epitaxial growth are reviewed and compared. One of the challenges associated with realizing graphene transistors is that graphene is semimetallic, with a zero bandgap, which is troublesome in the context of digital electronics applications. Thus, the report also reviews different ways of opening a bandgap in graphene by using bi- layer graphene and graphene nanoribbons. The basic operation of a conventional field effect transistor is explained and key figures of merit used in the literature are extracted. Finally, a review of some examples of state-of-the-art graphene field effect transistors is presented, with particular focus on monolayer graphene, bilayer graphene, and graphene nanoribbons. -

Role of Mosfets Transconductance Parameters and Threshold Voltage in CMOS Inverter Behavior in DC Mode

Preprints (www.preprints.org) | NOT PEER-REVIEWED | Posted: 28 July 2017 doi:10.20944/preprints201707.0084.v1 Article Role of MOSFETs Transconductance Parameters and Threshold Voltage in CMOS Inverter Behavior in DC Mode Milaim Zabeli1, Nebi Caka2, Myzafere Limani2 and Qamil Kabashi1,* 1 Department of Engineering Informatics, Faculty of Mechanical and Computer Engineering ([email protected]) 2 Department of Electronics, Faculty of Electrical and Computer Engineering ([email protected], [email protected]) * Correspondence: [email protected]; Tel.: +377-44-244-630 Abstract: The objective of this paper is to research the impact of electrical and physical parameters that characterize the complementary MOSFET transistors (NMOS and PMOS transistors) in the CMOS inverter for static mode of operation. In addition to this, the paper also aims at exploring the directives that are to be followed during the design phase of the CMOS inverters that enable designers to design the CMOS inverters with the best possible performance, depending on operation conditions. The CMOS inverter designed with the best possible features also enables the designing of the CMOS logic circuits with the best possible performance, according to the operation conditions and designers’ requirements. Keywords: CMOS inverter; NMOS transistor; PMOS transistor; voltage transfer characteristic (VTC), threshold voltage; voltage critical value; noise margins; NMOS transconductance parameter; PMOS transconductance parameter 1. Introduction CMOS logic circuits represent the family of logic circuits which are the most popular technology for the implementation of digital circuits, or digital systems. The small dimensions, low power of dissipation and ease of fabrication enable extremely high levels of integration (or circuits packing densities) in digital systems [1-5]. -

Junction Field Effect Transistor (JFET)

Junction Field Effect Transistor (JFET) The single channel junction field-effect transistor (JFET) is probably the simplest transistor available. As shown in the schematics below (Figure 6.13 in your text) for the n-channel JFET (left) and the p-channel JFET (right), these devices are simply an area of doped silicon with two diffusions of the opposite doping. Please be aware that the schematics presented are for illustrative purposes only and are simplified versions of the actual device. Note that the material that serves as the foundation of the device defines the channel type. Like the BJT, the JFET is a three terminal device. Although there are physically two gate diffusions, they are tied together and act as a single gate terminal. The other two contacts, the drain and source, are placed at either end of the channel region. The JFET is a symmetric device (the source and drain may be interchanged), however it is useful in circuit design to designate the terminals as shown in the circuit symbols above. The operation of the JFET is based on controlling the bias on the pn junction between gate and channel (note that a single pn junction is discussed since the two gate contacts are tied together in parallel – what happens at one gate-channel pn junction is happening on the other). If a voltage is applied between the drain and source, current will flow (the conventional direction for current flow is from the terminal designated to be the gate to that which is designated as the source). The device is therefore in a normally on state. -

Chapter1: Semiconductor Diode

Chapter1: Semiconductor Diode. Electronics I Discussion Eng.Abdo Salah Theoretical Background: • The semiconductor diode is formed by doping P-type impurity in one side and N-type of impurity in another side of the semiconductor crystal forming a p-n junction as shown in the following figure. At the junction initially free charge carriers from both side recombine forming negatively c harged ions in P side of junction(an atom in P -side accept electron and be comes negatively c harged ion) and po sitive ly c harged ion on n side (an atom in n-side accepts hole i.e. donates electron and becomes positively charged ion)region. This region deplete of any type of free charge carrier is called as depletion region. Further recombination of free carrier on both side is prevented because of the depletion voltage generated due to charge carriers kept at distance by depletion (acts as a sort of insulation) layer as shown dotted in the above figure. Working principle: When voltage is not app lied acros s the diode , de pletion region for ms as shown in the above figure. When the voltage is applied be tween the two terminals of the diode (anode and cathode) two possibilities arises depending o n polarity of DC supply. [1] Forward-Bias Condition: When the +Ve terminal of the battery is connected to P-type material & -Ve terminal to N-type terminal as shown in the circuit diagram, the diode is said to be forward biased. The application of forward bias voltage will force electrons in N-type and holes in P -type material to recombine with the ions near boundary and to flow crossing junction. -

Failure Precursors for Insulated Gate Bipolar Transistors (Igbts) Nishad Patil1, Diganta Das1, Kai Goebel2 and Michael Pecht1

Failure Precursors for Insulated Gate Bipolar Transistors (IGBTs) 1 1 2 1 Nishad Patil , Diganta Das , Kai Goebel and Michael Pecht 1Center for Advanced Life Cycle Engineering (CALCE) University of Maryland College Park, MD 20742, USA 2NASA Ames Research Center Moffett Field, CA 94035, USA Abstract Failure precursors indicate changes in a measured variable that can be associated with impending failure. By identifying precursors to failure and by monitoring them, system failures can be predicted and actions can be taken to mitigate their effects. In this study, three potential failure precursor candidates, threshold voltage, transconductance, and collector-emitter ON voltage, are evaluated for insulated gate bipolar transistors (IGBTs). Based on the failure causes determined by the failure modes, mechanisms and effects analysis (FMMEA), IGBTs are aged using electrical-thermal stresses. The three failure precursor candidates of aged IGBTs are compared with new IGBTs under a temperature range of 25-200oC. The trends in the three electrical parameters with changes in temperature are correlated to device degradation. A methodology is presented for validating these precursors for IGBT prognostics using a hybrid approach. Keywords: Failure precursors, IGBTs, prognostics Failure precursors indicate changes in a measured variable structure of an IGBT is similar to that of a vertical that can be associated with impending failure [1]. A diffusion power MOSFET (VDMOS) [3] except for an systematic method for failure precursor selection is additional p+ layer above the collector as seen in Figure 1. through the use of the failure modes, mechanisms, and The main characteristic of the vertical configuration is that effects analysis (FMMEA) [2]. -

MOSFET - Wikipedia, the Free Encyclopedia

MOSFET - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/MOSFET MOSFET From Wikipedia, the free encyclopedia The metal-oxide-semiconductor field-effect transistor (MOSFET, MOS-FET, or MOS FET), is by far the most common field-effect transistor in both digital and analog circuits. The MOSFET is composed of a channel of n-type or p-type semiconductor material (see article on semiconductor devices), and is accordingly called an NMOSFET or a PMOSFET (also commonly nMOSFET, pMOSFET, NMOS FET, PMOS FET, nMOS FET, pMOS FET). The 'metal' in the name (for transistors upto the 65 nanometer technology node) is an anachronism from early chips in which the gates were metal; They use polysilicon gates. IGFET is a related, more general term meaning insulated-gate field-effect transistor, and is almost synonymous with "MOSFET", though it can refer to FETs with a gate insulator that is not oxide. Some prefer to use "IGFET" when referring to devices with polysilicon gates, but most still call them MOSFETs. With the new generation of high-k technology that Intel and IBM have announced [1] (http://www.intel.com/technology/silicon/45nm_technology.htm) , metal gates in conjunction with the a high-k dielectric material replacing the silicon dioxide are making a comeback replacing the polysilicon. Usually the semiconductor of choice is silicon, but some chip manufacturers, most notably IBM, have begun to use a mixture of silicon and germanium (SiGe) in MOSFET channels. Unfortunately, many semiconductors with better electrical properties than silicon, such as gallium arsenide, do not form good gate oxides and thus are not suitable for MOSFETs. -

The Reliability of the Silicon Nitride Dielectric in Capacitive MEMS

The Pennsylvania State University The Graduate School Department of Materials Science and Engineering THE RELIABILITY OF THE SILICON NITRIDE DIELECTRIC IN CAPACITIVE MEMS SWITCHES A Thesis in Materials Science and Engineering by Abuzer Dogan © 2005 Abuzer Dogan Submitted in Partial Fulfillment of the Requirements for the Degree of Master of Science August 2005 I grant The Pennsylvania State University the nonexclusive right to use this work for the University's own purposes and to make single copies of the work available to the public on a not-for-profit basis if copies are not otherwise available. Abuzer Dogan We approve the thesis of Abuzer Dogan. Date of Signature Susan Trolier-McKinstry Professor of Ceramic Science and Engineering Thesis Advisor Michael Lanagan Associate Professor of Engineering Science and Mechanics and Materials Science and Engineering Mark Horn Associate Professor of Engineering Science and Mechanics James P. Runt Professor of Polymer Science Associate Head for Graduate Studies iii ABSTRACT Silicon nitride thin film dielectrics can be used in capacitive radio frequency micro-electromechanical systems switches since they provide a low insertion loss, good isolation, and low return loss. The lifetime of these switches is believed to be adversely affected by charge trapping in the silicon nitride. These charges cause the metal bridge to be partially or fully pulled down, degrading the on-off ratio of the switch. Little information is available in the literature providing a fundamental solution to this problem. Consequently, the goals of this research were to characterize SixNy–based MIM (Metal-Insulator-Metal) capacitors and capacitive MEMS switches to measure the current-voltage response. -

AN5252 Low-Voltage Power MOSFET Switching Behavior And

AN5252 Application note Low-voltage Power MOSFET switching behavior and performance evaluation in motor control application topologies Introduction During the last years, some applications based on electrical power conversion are gaining more and more space in the civil and industrial fields. The constant development of microprocessors and the improvement of modulation techniques, which are useful for the control of power devices, have led to a more accurate control of the converted power as well as of the power dissipation, thus increasing the efficiency of the motor control applications. Nowdays, frequency modulation techniques are used to control the torque and the speed of brushless motors in several high- and low-voltage applications and in different circuit topologies using power switches in different technologies such as MOSFETs and IGBTs. Therefore, the devices have to guarantee the best electrical efficiency and the least possible impact in terms of emissions. The aim of this application note is to provide a description of the most important parameters which are useful for choosing a low- voltage Power MOSFET device for a motor control application. Three different motor control applications and topology cases are deeply analyzed to offer to motor drive designers the guidelines required for an efficient and reliable design when using the MOSFET technology in hard-switch applications: • BLDC motor in a 3-phase inverter topology • DC motor in H-bridge configuration • DC motor in single-switch configuration AN5252 - Rev 1 - November 2018 - By C. Mistretta and F. Scrimizzi www.st.com For further information contact your local STMicroelectronics sales office. AN5252 Control techniques and brushless DC (BLDC) motors 1 Control techniques and brushless DC (BLDC) motors During the last years, servomotors have evolved from mostly brush to brushless type. -

Design of Cascode-Based Transconductance Amplifiers With

Design of Cascode-Based Transconductance Amplifiers with Low-Gain PVT Variability and Gain Enhancement Using a Body-Biasing Technique Nuno Pereira, Luis Oliveira, João Goes To cite this version: Nuno Pereira, Luis Oliveira, João Goes. Design of Cascode-Based Transconductance Amplifiers with Low-Gain PVT Variability and Gain Enhancement Using a Body-Biasing Technique. 4th Doctoral Conference on Computing, Electrical and Industrial Systems (DoCEIS), Apr 2013, Costa de Caparica, Portugal. pp.590-599, 10.1007/978-3-642-37291-9_64. hal-01348806 HAL Id: hal-01348806 https://hal.archives-ouvertes.fr/hal-01348806 Submitted on 25 Jul 2016 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. Distributed under a Creative Commons Attribution| 4.0 International License Design of Cascode-based Transconductance Amplifiers with Low-gain PVT Variability and Gain Enhancement Using a Body-biasing Technique Nuno Pereira 2, Luis B. Oliveira 1,2 and João Goes 1,2 1 Centre for Technologies and Systems (CTS) – UNINOVA 2 Dept. of Electrical Engineering (DEE), Universidade Nova de Lisboa (UNL) Campus FCT/UNL, 2829-516, Caparica, Portugal [email protected], [email protected], [email protected] Abstract. -

Analog Integrated Current Drivers for Bioimpedance Applications: a Review

sensors Review Analog Integrated Current Drivers for Bioimpedance Applications: A Review Nazanin Neshatvar * , Peter Langlois, Richard Bayford and Andreas Demosthenous Department of Electronic and Electrical Engineering, University College London, Torrington Place, London WC1E 7JE, UK; [email protected] (P.L.); [email protected] (R.B.); [email protected] (A.D.) * Correspondence: [email protected] Received: 17 January 2019; Accepted: 4 February 2019; Published: 13 February 2019 Abstract: An important component in bioimpedance measurements is the current driver, which can operate over a wide range of impedance and frequency. This paper provides a review of integrated circuit analog current drivers which have been developed in the last 10 years. Important features for current drivers are high output impedance, low phase delay, and low harmonic distortion. In this paper, the analog current drivers are grouped into two categories based on open loop or closed loop designs. The characteristics of each design are identified. Keywords: bioimpedance measurement; current driver; integrated circuit; linear feedback; nonlinear feedback; transconductance 1. Introduction Bioimpedance measurement is defined as the study of biological tissue/cell in response to an alternating electric field, which can cover a frequency range from tens of Hz to several MHz [1,2]. The electrical properties of tissue/cell (conductive and dielectric properties) are characterized by frequency variable complex electrical bioimpedance providing important information about the tissue/cell physiology and pathology. In order to measure the bioimpedance, a current stimulus is required to be provided through a set of electrodes and measuring the corresponding potential via the same, or another, pair of electrodes. -

MOSFET Technology Scaling, Leakage Current, and Other Topics

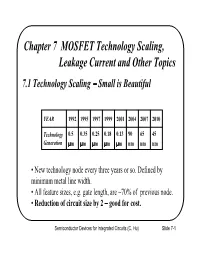

Chapter 7 MOSFET Technology Scaling, Leakage Current and Other Topics 7.1 Technology Scaling Small is Beautiful YEAR 1992 1995 1997 1999 2001 2004 2007 2010 Technology 0.5 0.35 0.25 0.18 0.13 90 65 45 Generation µµµm µµµm µµµm µµµm µµµm nm nm nm • New technology node every three years or so. Defined by minimum metal line width. • All feature sizes, e.g. gate length, are ~70% of previous node. • Reduction of circuit size by 2 good for cost. Semiconductor Devices for Integrated Circuits (C. Hu) Slide 7-1 International Technology Roadmap for Semiconductors, 1999 Edition Year of Shipment 1999 2002 2005 2008 2011 2014 DRAM metal half pitch 180 130 100 70 50 35 (nm) MPU physical Lg (nm) 140 85 65 45 32 22 Tox (nm) 1.5-1.8 1.5-1.9 1-1.5 0.8-1.2 0.6-0.8 0.5-0.6 VDD 1.5-1.8 1.2-1.5 0.9-1.2 0.6-0.9 0.5-0.6 0.3-0.6 µµµ µµµ Ion,HP ( A/ m) 750/350 750/350 750/350 750/350 750/350 750/350 µµµ Ioff,HP (nA/ m) 5 10 20 40 60 160 µµµ µµµ Ion,LP ( A/ m) 490/230 490/230 490/230 490/230 490/230 490/230 µµµ Ioff,LP (pA/ m) 7 10 20 40 80 160 No known solutions •Vdd is reduced at each node to contain power consumption in spite of rising transistor density and frequency •Tox is reduced to raise I on for speed consideration Semiconductor Devices for Integrated Circuits (C. -

Resistors, Diodes, Transistors, and the Semiconductor Value of a Resistor

Resistors, Diodes, Transistors, and the Semiconductor Value of a Resistor Most resistors look like the following: A Four-Band Resistor As you can see, there are four color-coded bands on the resistor. The value of the resistor is encoded into them. We will follow the procedure below to decode this value. • When determining the value of a resistor, orient it so the gold or silver band is on the right, as shown above. • You can now decode what resistance value the above resistor has by using the table on the following page. • We start on the left with the first band, which is BLUE in this case. So the first digit of the resistor value is 6 as indicated in the table. • Then we move to the next band to the right, which is GREEN in this case. So the second digit of the resistor value is 5 as indicated in the table. • The next band to the right, the third one, is RED. This is the multiplier of the resistor value, which is 100 as indicated in the table. • Finally, the last band on the right is the GOLD band. This is the tolerance of the resistor value, which is 5%. The fourth band always indicates the tolerance of the resistor. • We now put the first digit and the second digit next to each other to create a value. In this case, it’s 65. 6 next to 5 is 65. • Then we multiply that by the multiplier, which is 100. 65 x 100 = 6,500. • And the last band tells us that there is a 5% tolerance on the total of 6500.