MEMS Four-Terminal Variable Capacitor for Low Power Capacitive Adiabatic Logic with High Logic State Differentiation Hatem Samaali, Y

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Modelling and Characterization of DCO Using Pass Transistors

2833 E.Kanniga et al./ Elixir Power Elec. Engg. 35 (2011) 2833-2835 Available online at www.elixirpublishers.com (Elixir International Journal) Power Electronics Engineering Elixir Power Elec. Engg. 35 (2011) 2833-2835 Modelling and characterization of DCO using Pass Transistors E.Kanniga 1 and M.Sundararajan 2 1Department of ECE, Bharath University, Chennai-73 2Gojan School of Business & Technology, Chennai-52. ARTICLE INFO ABSTRACT Article history: In the field of simulation work, it could proceed to an extent that, simulate with arbitrary Received: 6 April 2011; values of the passive component and the voltage sources. The simulation results recorded Received in revised form: various strategic points in the circuit indicate and validate the fact that the circuit is working 19 May 2011; in the expected lines with regard to the energy transfer in the expected lines with regard to Accepted: 26 May 2011; the energy transfer in the tank circuit and sustenance in DC transient Analysis. Also in this proposed experimental work, it is observed that for an arbitrary load, the voltage obtained is Keywords agreeing with the theoretically computed DC-Voltage levels. The scope of the work can be Digital controlled oscillator, extended to the actual calculation of the passives, the initial voltages across the capacitors Steady state transient response, and inductors. In addition to the exciting DC levels of the sources employed. The small Simulation LTSPICE, signal analysis can also be done with due regard to the desired behavioural properties of Varactors. switching devices used. © 2011 Elixir All rights reserved. ntroduction In the digital world there is an increased requirement for Fig1 shows that NMOS transistors configured as a Varactor Digitally Controlled Oscillator (DCO). -

Commissioning of the Mice Rf System* A

5th International Particle Accelerator Conference IPAC2014, Dresden, Germany JACoW Publishing ISBN: 978-3-95450-132-8 doi:10.18429/JACoW-IPAC2014-WEPME020 COMMISSIONING OF THE MICE RF SYSTEM* A. Moss, A. Wheelhouse, T. Stanley, C. White, STFC, Daresbury Laboratory, Warrington, UK K. Ronald, C.G. Whyte, A.J. Dick, D.C. Speirs, SUPA, Dept.of Physics, University of Strathclyde, Glasgow, UK S. Alsari, Imperial College of Science and Technology, London, UK on behalf of the MICE Collaboration Abstract feature adjustable sections to change the response of the cavity to both input line and resistive load. On the output The Muon Ionisation Cooling Experiment (MICE) is of the amplifier, the cavity length and hence its resonant being constructed at Rutherford Appleton Laboratory in frequency can be adjusted, whilst a stub tuner is located in the UK. The muon beam will be cooled using multiple the output coax section to alter the coupling factor into hydrogen absorbers then reaccelerated using an RF cavity the output coax so that the amplifier may be used to drive system operating at 201MHz. This paper describes recent a range of different load conditions. For use in the MICE progress in commissioning the amplifier systems at their system the 4616 operates in long pulse mode using grid design operation conditions, installation and operation as pulsed operation and can provide up to 250kW RF output part of the MICE project. power. INTRODUCTION 4616 Power Supply The muon ionisation cooling experiment is a The power supply for the tetrode amplifier consists of a demonstration of practical cooling for future muon TDK-Lambda 500A capacitor charger power supply acceleration schemes. -

Eimac Care and Feeding of Tubes Part 3

SECTION 3 ELECTRICAL DESIGN CONSIDERATIONS 3.1 CLASS OF OPERATION Most power grid tubes used in AF or RF amplifiers can be operated over a wide range of grid bias voltage (or in the case of grounded grid configuration, cathode bias voltage) as determined by specific performance requirements such as gain, linearity and efficiency. Changes in the bias voltage will vary the conduction angle (that being the portion of the 360° cycle of varying anode voltage during which anode current flows.) A useful system has been developed that identifies several common conditions of bias voltage (and resulting anode current conduction angle). The classifications thus assigned allow one to easily differentiate between the various operating conditions. Class A is generally considered to define a conduction angle of 360°, class B is a conduction angle of 180°, with class C less than 180° conduction angle. Class AB defines operation in the range between 180° and 360° of conduction. This class is further defined by using subscripts 1 and 2. Class AB1 has no grid current flow and class AB2 has some grid current flow during the anode conduction angle. Example Class AB2 operation - denotes an anode current conduction angle of 180° to 360° degrees and that grid current is flowing. The class of operation has nothing to do with whether a tube is grid- driven or cathode-driven. The magnitude of the grid bias voltage establishes the class of operation; the amount of drive voltage applied to the tube determines the actual conduction angle. The anode current conduction angle will determine to a great extent the overall anode efficiency. -

RF-CMOS-MEMS Based Frequency-Reconfigurable Amplifiers

IEEE 2009 Custom Intergrated Circuits Conference (CICC) RF-CMOS-MEMS based Frequency-Reconfigurable Amplifiers Tamal Mukherjee and Gary K. Fedder Carnegie Mellon University Abstract-Chips from a foundry RF process are post-processed to The resulting MEMS structures are composed of the CMOS release MEMS passive devices and enable single-chip metal/dielectric stack. This paper focuses on a 6-metal reconfigurable circuits. A MEMS variable capacitor, capable of 0.18 µm and a 4-metal 0.35 µm foundry process. Multi-project 7:1 tuning ratio, reconfigures a narrow-band low-noise amplifier wafer chips from both processes are processed identically and a power amplifier over a 1 GHz frequency range. A except that the oxide etch for the 0.18 µm case is extended to suspended MEMS inductor, with > 50% improvement in Q, lowers amplifier power consumption. compensate for the thicker 6-metal stack. A. MEMS Variable Capacitor I. INTRODUCTION A MEMS variable capacitor for use in reconfigurable RF Multiband transceivers are a critical component in circuits should have high tuning range, linearity and Q, and envisioned software-controlled radios. In power-constrained low parasitic capacitance and resistance at its terminals. The mobile terminals, they either need wideband RF front ends, or latest MEMS variable capacitor extends an electrothermal frequency-reconfigurable narrowband front-ends. The design [9], in which large displacements (~10 µm) can be wideband approach is fraught with inadequate sampling rates, achieved using low voltages (< 5V) unlike the electrostatic inferior linearity and high power. An ideal solution is a fully- designs typically used in RF MEMS capacitive switches. -

Vacuum Capacitors Combining Expertise and Technology 2 Vacuum Capacitors Vacuum Capacitors 3

Led by experience. Driven by curiosity. Vacuum Capacitors Combining expertise and technology 2 Vacuum Capacitors Vacuum Capacitors 3 Table of contents We empower new technologies 4 Advanced technologies 7 Variable Vacuum Capacitors 12 Fixed Vacuum Capacitors 30 Trimmer Vacuum Capacitor 38 Motorized Capacitors 42 Customized solutions 48 Series overview 50 Service Bulletins 54 Contacts 56 4 Vacuum Capacitors Vacuum Capacitors 5 We empower new technologies Comet is a leading expert in RF power delivery and a global innovation partner of RF related business- es for more than 50 years. Our products have earned a global reputation for quality and reliabili- ty over a broad variety of applications. By exploring the mysteries of plasma behavior Comet is contributing to the evolution of the semiconductor industry. With the goal to provide our customers with the most precise tools we “We create solutions engineer and manufacture the most advanced RF power systems and diagnostic tools to master that respond both to plasma processes. today’s trends and Comet’s profound know-how in RF circuit modeling tomorrow’s needs.” and design has its origin in the development of vacuum capacitors. A broad range of capacitors Michael Kammerer for all needs guarantees you highest performance, President Comet repeatability and reliability of your tools. Besides Plasma Control Technologies that, the unique modular and customized design allows a high degree of flexibility in production and guarantees the delivery of special types on short notice. To improve the performance of our Imped- ance Matching Networks exclusively Comet Vaccum Capacitors are used. In this catalog you will learn more about the broadest selection of capacitance, power, voltage and drive systems in the market. -

Precision Variable Capacitors

---------- ----------------------------------------------------------------------------- 234 PHILIPS TECHNICAL REVIEW VOLUME 20 PRECISION VARIABLE CAPACITORS by A. A. TURNBULL *). 621.319.43 Electronic equipment for military uses is designed for specifications which require components of very high quality, Components must frequently be not only of high accuracy and stability but must also be compact and robust. The article below describes two precision variable capac- itors which, although compact, have a performance comparable with laboratory capacitors of considerably larger size. Two types of precision variable capacitors (fig. 1) requirement IS that the capacitors should be have been designed at the Mullard Research sufficiently small to allow their convenient installa- Laboratories for high grade electronic equipment, tion in equipment, particularly in compact military meeting stringent specifications as regards their equipment. The linear-law capacitor, for example, accuracy and stability 1). One of these capacitors was originally designed for a specific equipment, in gives a linear frequency law for use in transmitter which three of these capacitors were ganged in master-oscillator circuits or in receiver local oscilla- line. In the layout of this equipment only a limited tor circuits. The other is a sine-frequency-law space was available for the capacitors. Similar 95605 Fig. 1. The two precision capacitors with covers removed. Left, the linear-law capacitor. Right, the sine-law capacitor. capacitor and was designed primarily for the con- considerations also limit the size of the sine-law version of radar range and bearing information capacitor. from polar to cartesian form 2). Some of the features common to both the capaci- The term stability in connection with these tors may be described, before passing on to the capacitors implies stability over long periods, detailed consideration of each type. -

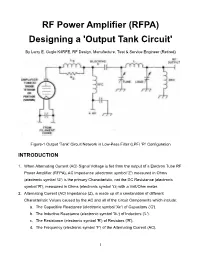

RF Power Amplifier (RFPA) Designing a 'Output Tank Circuit'

RF Power Amplifier (RFPA) Designing a 'Output Tank Circuit' By Larry E. Gugle K4RFE, RF Design, Manufacture, Test & Service Engineer (Retired) Figure-1 Output 'Tank' Circuit Network in Low-Pass Filter (LPF) 'Pi' Configuration INTRODUCTION 1. When Alternating Current (AC) Signal Voltage is fed from the output of a Electron Tube RF Power Amplifier (RFPA), AC Impedance (electronic symbol 'Z') measured in Ohms (electronic symbol '') is the primary Characteristic, not the DC Resistance (electronic symbol 'R'), measured in Ohms (electronic symbol 'with a Volt/Ohm meter. 2. Alternating Current (AC) Impedance (Z), is made up of a combination of different Characteristic Values caused by the AC and all of the circuit Components which include: a. The Capacitive Reactance (electronic symbol 'Xc') of Capacitors ('C'). b. The Inductive Reactance (electronic symbol 'XL') of Inductors ('L'). c. The Resistance (electronic symbol 'R') of Resistors ('R'). d. The Frequency (electronic symbol 'F') of the Alternating Current (AC). 1 3. When any one of these Characteristic Values change, the value of the AC Impedance (Z) will also change. 4. Plate Tune and Load Coupling Networks, either in a ‘Pi’ or ‘Pi-L’ configuration, are designed so that a RF Power Amplifier (RFPA) provides Optimum Output Power with a minimum of Odd-Order Harmonic, Intermodulation Distortion (IMD) content. 5. To obtain high efficient operation from an Electron Tube RF Power Amplifier (RFPA), the RF Amplifying Device, either a Power Triode, Tetrode or Pentode, is normally operated in it’s Linear Region of Conduction Angle (Class ‘AB1’, 'AB2' or ‘B’) for Single Side Band Suppressed Carrier - Amplitude Modulation (SSBSC-AM) Telephony Signals and operated in it’s Non-Linear Region of Conduction Angle (Class ‘C’) for Interrupted Continuous Wave (CW) ‘On’ and ‘Off’ Keying Telegraphy, Frequency Modulation (FM) Telephony and Phase Modulation (PM) Telephony Signals. -

Blumlein-Type X-Band Klystron Modulator for Japan Linear Collider

© 1991 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE. Blumlein-type X-band Klystron Modulator for JapanLinear Collider Tetsuo Shidara, Mitsuo Akemoto, Masato Yoshida, Seishi Takeda and Koji Takata KEK, National Laboratory for High Energy Physics l-l Oho, Tsukuba-shi, Ibaraki-ken, 305 Japan Iwao Ohshima and Tsuneharu Teranishi Heavy Apparatus Engineering Laboratory, Toshiba Corp. 2-l Ukishima-cho, Kawasaki-ku, Kawasaki-shi, Kanagawa-ken, 210 Japan Abstracf A Blumlein-type X-band klystron modulator using magnetic-pulse-compression (MPC) techniques was designed and constructed relevant to the future Japan Linear Collider (JLC) project. This modulator has been designed to produce pulses that are 200-ns wide, 600-kV peak voltage, 1200-A peak current and a short rise time of - 70 ns with a repetition 21. mn rate exceeding 200 Hz. To realize a compact modulator, a spiral structure was adopted to conductors of the triaxial Figure 1. Simplified diagram of the X-band klystron Blumlein. Special care was taken regarding the location of modulator using a PFN, pulse transformer and the magnetic switch and the charging reactor in order to magnetic switches. step-up eliminate any undesirable voltage during the charging process. Tronrtormcr Bldein Details concerning this X-band klystron modulator and its / ---$$g+> preliminary performance are described. ,a: ,I II jc - ---q-;,, I. -

Advanced RC Phase Delay Capacitive Sensor Interface Circuits for MEMS

Advanced RC Phase Delay Capacitive Sensor Interface Circuits for MEMS by Yuan Meng A thesis submitted to the Graduate Faculty of Auburn University in partial fulfillment of the requirements for the Degree of Master of Science Auburn, Alabama May 9, 2015 Keywords: capacitive sensor, interface circuit, RC network, phase delay, MEMS Copyright 2015 by Yuan Meng Approved by Robert Dean, Chair, Associate Professor of Electrical and Computer Engineering Thomas Baginski, Professor of Electrical and Computer Engineering Thaddeus Roppel, Associate Professor of Electrical and Computer Engineering Abstract Many types of sensors in MEMS technology convert a measurand to a proportional change in capacitance. One of the techniques of measuring capacitance is utilizing the phase delay of an RC network with a resistor and the sensor capacitor. Specifically, the state of an input square wave signal is delayed by the RC network and gives a pulse width modulated signal according to the phase delay at the output, which is proportional to the capacitance, if the resistance is fixed. However, the response of this method becomes severely nonlinear if the phase delay is bigger than approximately 45°. Two improved implementations are presented to avoid the nonlinearity caused by the capacitor being not fully charged and discharged each cycle. The first one uses a PMOSFET switch to charge the unknown capacitor and an NMOSFET to discharge it during each measurement cycle. The second one uses an analog switch to switch the resistance to be significantly lower when the capacitor needs to be fully charged or discharged in each cycle. Both methods were simulated and proved effective. -

Variable Capacitors

Tech Notes - Variable capacitors A Variable Capacitor is one whose capacitance may be intentionally and repeatedly changed mechanically. Variable capacitors are often used in L/C circuits to set the resonance frequency, for example, to tune a radio (therefore they are sometimes called tuning capacitors), or as a variable reactance for impedance matching in antenna tuners. Can also known as a "variable air” capacitors. The old name for a capacitor was condensor. Tuning capacitors: A typical variable capacitor consists of two sets of metal plates arranged so that the rotor plates move between the stator plates. Air is often the dielectric. As the position of the rotor is changed, the capacitance value is likewise changed. This type of capacitor is used for tuning most radio receivers. A typical physical construction is shown below. The capacitors pictured above, from left, include our 365 pF dual-gang variable, a 365 pf variable with 8:1 shaft reduction drive built into the shaft, a 365 pF with shaft extended with nylon parts to isolate the capacitor from the user, and a 365 pF attached to a 6:1 external planetary reduction drive. Variable capacitors for tuning radio equipment are made in many formats and can be single gang type (the second and fourth ones above) but can have two three or four sections “ganged” in the Tech Notes - Variable capacitors same shaft. The fourth one above has a five to one reduction drive connected between the capacitor and the tuning knob to make tuning easier. Simple radio receivers will have a “dial drum” connected to a small diameter shaft to achieve the same aim. -

Technician License Course Chapter 3.2

Technician License Course Chapter 3.2 Electricity, Components and Circuits Lesson Plan Module 6 Larry Hall KD0RIU 1 Electronics – Controlling the Flow of Current • To make an electronic device (like a radio) do something useful (like a receiver), we need to control and manipulate the flow of current. • There are a number of different electronic components that we use to do this. 2 The Resistor • The function of the • Circuit Symbol resistor is to restrict (limit) the flow of current through it. 3 The Capacitor • The function of the • Circuit Symbol capacitor is to temporarily store electric field or charge. – Like a very temporary storage battery. – Stores energy in an electrostatic field of electrons. 4 The Inductor • The function of the • Circuit Symbol inductor is to temporarily store energy in a magnetic field around the inductor. – Is basically a coil of wire. 5 Resonance • Because capacitors and inductors store energy in different ways, the stored energy can actually cancel each other under the right conditions. – Capacitors – electric field – Inductors – magnetic field • Cancelled current = no reactance, just leaving resistance. 6 Resonant Antenna • If an antenna is designed correctly, the capacitive reactance cancels the inductive reactance. • Theoretically, the resulting reactance is zero. – Leaving only resistance – meaning minimum impediment to the radio frequency currents flowing in the antenna and sending the radio wave into space. 7 Antennas are Part Capacitor – Part Inductor – Part Resistor • Antennas actually have characteristics of capacitor, inductor and resistor electronic components. • Capacitors and inductors, because they store energy in fields, react differently to ac than dc. – Special kind of resistance to the flow of ac – called reactance. -

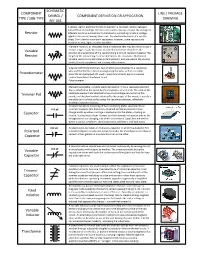

Download Schematic-Symbols-Page-1.Pdf

SCHEMATIC COMPONENT LINE / PACKAGE SYMBOL / COMPONENT DEFINITION OR APPLICATION TYPE / SUB-TYPE DRAWING REF DES A device used in electrical circuits to maintain a constant relation between current flow and voltage. Resistors are used to step up or lower the voltage at Resistor different points in a circuit and to transform a current signal into a voltage signal or vice versa, among other uses. The electrical behavior of a resistor obeys Ohm's law for a constant resistance; however, some resistors are sensitive to heat, light, or other variables. Variable resistors, or rheostats, have a resistance that may be varied across a Variable certain range, usually by means of a mechanical device that alters the position of one terminal of the resistor along a strip of resistant material. The Resistor length of the intervening material determines the resistance. Mechanical variable resistors are also called potentiometers, and are used in the volume knobs of audio equipment and in many other devices. a device with three terminals, two of which are connected to a resistance wire and the third to a brush moving along the wire, so that a variable Potentiometer potential can be tapped off: used in electronic circuits, esp as a volume control Sometimes shortened to pot Potentiometer. Manually adjustable, variable, electrical resistor. It has a resistance element that is attached to the circuit by three contacts, or terminals. The ends of the resistance element are attached to two input voltage conductors of the Trimmer Pot circuit, and the third contact, attached to the output of the circuit, is usually a movable terminal that slides across the resistance element, effectively dividing it into two resistors.