PAP Advanced Computer Architectures 1 ISA Development History

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Arm Arhitektura Napreduje – No Postoje Izazovi

ARM ARHITEKTURA NAPREDUJE – NO POSTOJE IZAZOVI SAŽETAK Procesori ARM ISA arhitekture ne koriste se više "samo" za mobitele i tablete, nego i za serverska računala (pa i superračunala), te laptop / desktop računala. I Apple je kod Macintosh računala prešao sa Intel arhitekture na ARM arhitekturu. Veliki izazov kod tog prelaska bio je - kako omogućiti da se programski kod pisan za Intelovu ISA arhitekturu, izvršava na procesoru M1 koji ima ARM arhitekturu. Općenito, želja je da se programi pisani za jednu ISA arhitekturu mogu sa što manje napora izvršavati na računalima koja imaju drugačiju ISA arhitekturu. Problem je u tome što različite ISA arhitekture mogu imati dosta različite memorijske modele. ABSTRACT ARM ISA processors are no longer used "only" for mobile phones and tablets, but also for server computers (even supercomputers) and laptops / desktops. Apple has also switched from Intel to ARM on Macintosh computers. The big challenge in that transition was - how to enable program code written for Intel's ISA architecture to run on an M1 processor that has an ARM architecture. In general, the desire is that programs written for one ISA architecture can be executed with as little effort as possible on computers that have a different ISA architecture. The problem is that different ISA architectures can have quite different memory models. 1. UVOD Procesori ARM ISA arhitekture ne koriste se više "samo" za mobitele i tablete, nego i za serverska računala (pa i superračunala), te laptop/desktop računala. Koriste se i u industriji, u proizvodnim procesima, a i kao ugradbeni čipovi u ostale proizvode, npr. za ugradnju u IOT uređaje i u vozila (posebno autonomna vozila). -

Installation and Upgrade General Checklist Report

VeritasTM Services and Operations Readiness Tools Installation and Upgrade Checklist Report for InfoScale Storage 7.3.1, Solaris 11, SPARC Index Back to top Important Notes Components for InfoScale System requirements Product features Product documentation Patches for InfoScale Storage and Platform Platform configuration Host bus adapter (HBA) parameters and switch parameters Operations Manager Array Support Libraries (ASLs) Additional tasks to consider Important Notes Back to top Note: You have not selected the latest product version. Consider installing or upgrading to the latest version; otherwise, you may encounter issues that have already been fixed. To run a new report for the latest product version, select it from the Veritas product drop-down list. Array Support Libraries (ASLs) When installing Veritas products, please be aware that ASLs updates are not included in the patches update bundle. Please go to the Array Support Libraries (ASLs) to get the latest updates for your disk arrays. Components for InfoScale Back to top The InfoScale product you selected contains the following component(s). Dynamic Multi-Pathing Storage Foundation Storage Foundation Cluster File System Get more introduction of Veritas InfoScale. System requirements Back to top Required CPU number and memory: Required number of CPUs Required memory SF or SFHA N/A 2GB SFCFS or SFCFSHA 2 2GB 1 of 11 VeritasTM Services and Operations Readiness Tools Required disk space: Partitions Minimum space required Maximum space required Recommended space /opt 99 MB 1051 MB 134 MB /root 1 MB 30 MB 1 MB /usr 3 MB 237 MB 3 MB /var 1 MB 1 MB 1 MB Supported architectures: SPARC M5 series [1] SPARC M6 series [1] SPARC M7 series [1][2] SPARC S7 series [1] SPARC T3 series [1] SPARC T4 series [1] SPARC T5 series [1] SPARC T7 series [1][2] SPARC T8 series [1][2] SPARC64 X+ series [1] SPARC64 XII series [1] SPARC64-V series SPARC64-VI series SPARC64-VII/VII+ series SPARC64-X series [1] UltraSPARC II series UltraSPARC III series UltraSPARC IV series UltraSPARC T1 series [1] UltraSPARC T2/T2+ series [1] 1. -

Fujitsu's Vision for High Performance Computing

FujitsuFujitsu’’ss VisionVision forfor HighHigh PerformancePerformance ComputingComputing October 26, 2004 Yuji Oinaga Fujitsu Ltd. 1 CONTENTSCONTENTS HPC Policy and Concept Current HPC Platform HPC2500 IA-Cluster Major HPC customers Road Map Toward Peta-Scale Computing 2 FUJITSUFUJITSU HPCHPC PolicyPolicy ~ Developing & Providing Top Level Supercomputer ~ - High Computational Power - High Speed Interconnect - Reliability/Availability - Leading Edge Semiconductor Technology - Highly Reliable, HPC Featured Operating System & Middleware - Sophisticated Compilers and Development Tools 3 HistoryHistory ofof HPCHPC PlatformPlatform PRIMEPOWER HPC2500 VPP5000 Vector Parallel VPP300/700 IA32/IPF Cluster PRIMEPOWER VPP500 2000 Vector VP2000 AP3000 VP Series AP1000 F230-75APU Scalar 1980 1985 1990 1995 2000 2005 4 ConceptConcept ofof FujitsuFujitsu HPCHPC ProvideProvide thethe best/fastestbest/fastest platformplatform forfor eacheach applications.applications. -Scalar SMP : PRIMEPOWER, New Linux SMP -IA Cluster : PRIMERGY Cluster ProvideProvide thethe highhigh speedspeed interconnect.interconnect. -Crossbar : High Speed Optical Interconnect -Multi-Stage : Infiniband ProvideProvide HighHigh Operability/UsabilityOperability/Usability -Enhancement of Operability/Usability : Extended Partitioning, Dynamic Reconfiguration -Cluster Middleware : Total Cluster Control System ( Parallelnavi ) Shared Rapid File System ( SRFS ) 5 FujitsuFujitsu’’ss CurrentCurrent HPCHPC PlatformPlatform ~ Fujitsu is a leading edge company in HPC field ~ SPARC/Solaris -

Computer Architectures an Overview

Computer Architectures An Overview PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Sat, 25 Feb 2012 22:35:32 UTC Contents Articles Microarchitecture 1 x86 7 PowerPC 23 IBM POWER 33 MIPS architecture 39 SPARC 57 ARM architecture 65 DEC Alpha 80 AlphaStation 92 AlphaServer 95 Very long instruction word 103 Instruction-level parallelism 107 Explicitly parallel instruction computing 108 References Article Sources and Contributors 111 Image Sources, Licenses and Contributors 113 Article Licenses License 114 Microarchitecture 1 Microarchitecture In computer engineering, microarchitecture (sometimes abbreviated to µarch or uarch), also called computer organization, is the way a given instruction set architecture (ISA) is implemented on a processor. A given ISA may be implemented with different microarchitectures.[1] Implementations might vary due to different goals of a given design or due to shifts in technology.[2] Computer architecture is the combination of microarchitecture and instruction set design. Relation to instruction set architecture The ISA is roughly the same as the programming model of a processor as seen by an assembly language programmer or compiler writer. The ISA includes the execution model, processor registers, address and data formats among other things. The Intel Core microarchitecture microarchitecture includes the constituent parts of the processor and how these interconnect and interoperate to implement the ISA. The microarchitecture of a machine is usually represented as (more or less detailed) diagrams that describe the interconnections of the various microarchitectural elements of the machine, which may be everything from single gates and registers, to complete arithmetic logic units (ALU)s and even larger elements. -

Die Meilensteine Der Computer-, Elek

Das Poster der digitalen Evolution – Die Meilensteine der Computer-, Elektronik- und Telekommunikations-Geschichte bis 1977 1977 1978 1979 1980 1981 1982 1983 1984 1985 1986 1987 1988 1989 1990 1991 1992 1993 1994 1995 1996 1997 1998 1999 2000 2001 2002 2003 2004 2005 2006 2007 2008 2009 2010 2011 2012 2013 2014 2015 2016 2017 2018 2019 2020 und ... Von den Anfängen bis zu den Geburtswehen des PCs PC-Geburt Evolution einer neuen Industrie Business-Start PC-Etablierungsphase Benutzerfreundlichkeit wird gross geschrieben Durchbruch in der Geschäftswelt Das Zeitalter der Fensterdarstellung Online-Zeitalter Internet-Hype Wireless-Zeitalter Web 2.0/Start Cloud Computing Start des Tablet-Zeitalters AI (CC, Deep- und Machine-Learning), Internet der Dinge (IoT) und Augmented Reality (AR) Zukunftsvisionen Phasen aber A. Bowyer Cloud Wichtig Zählhilfsmittel der Frühzeit Logarithmische Rechenhilfsmittel Einzelanfertigungen von Rechenmaschinen Start der EDV Die 2. Computergeneration setzte ab 1955 auf die revolutionäre Transistor-Technik Der PC kommt Jobs mel- All-in-One- NAS-Konzept OLPC-Projekt: Dass Computer und Bausteine immer kleiner, det sich Konzepte Start der entwickelt Computing für die AI- schneller, billiger und energieoptimierter werden, Hardware Hände und Finger sind die ersten Wichtige "PC-Vorläufer" finden wir mit dem werden Massenpro- den ersten Akzeptanz: ist bekannt. Bei diesen Visionen geht es um die Symbole für die Mengendarstel- schon sehr früh bei Lernsystemen. iMac und inter- duktion des Open Source Unterstüt- möglichen zukünftigen Anwendungen, die mit 3D-Drucker zung und lung. Ägyptische Illustration des Beispiele sind: Berkley Enterprice mit neuem essant: XO-1-Laptops: neuen Technologien und Konzepte ermöglicht Veriton RepRap nicht Ersatz werden. -

Microprocessor

MICROPROCESSOR www.MPRonline.com THE REPORTINSIDER’S GUIDE TO MICROPROCESSOR HARDWARE FUJITSU’S SPARC64 V IS REAL DEAL Fujitsu’s design differs from HAL’s version; faster than US III By Kevin Krewell {10/21/02-01} At Microprocessor Forum 2002, Fujitsu stepped forward to carry the banner for the fastest SPARC processor, surpassing Sun’s fastest UltraSPARC III on clock frequency and SPEC performance. In fact, at 1.35GHz, the Fujitsu processor has the highest clock frequency of any 64-bit server processor now in production. This by a Fujitsu acquisition, HAL Computer. At Micro- clock-speed advantage—plus large on-chip processor Forum 1999, Mike Shebanow, then vice caches; a fast system-crossbar switch; and a four- president and CTO of the HAL Computer Divi- issue, out-of-order core—translates into good sion of Fujitsu, proposed a complex and very wide SPEC benchmark performance for Fujitsu’s superscalar version of the SPARC64 V processor, SPARC64 V processor. The SPARC64 V is an evo- with an instruction trace cache, superspeculation, lutionary step in Fujitsu’s SPARC processor line and split L2 cache (see MPR 11/15/99-01,“Hal instead of the more-radical approach proposed three Makes Sparcs Fly”). Mike’s innovative chip never made years ago by HAL Computer at Microprocessor Forum it to market, but the trace-cache idea became a mainstream 1999. This latest version of Fujitsu’s SPARC processor fam- processor feature, shipping in Intel’s Pentium 4 microarchi- ily, revealed by Fujitsu’s director of Development Depart- tecture. The Pentium 4 also paralleled another of Mike’s ment (Processor Development Division) Aiichiro Inoue, is based on an enhanced version of the previous SPARC64 GP processor core, with larger caches and advanced semicon- L1I$ Decode & FP (16) L1D$ L2$ 128KB I-buffer Issue (4) SP (10) 128KB 2MB ductor process technology. -

AMD EPYC™ 7003 Series Cpus Set New Standard As Highest Performance Server Processor

March 15, 2021 AMD EPYC™ 7003 Series CPUs Set New Standard as Highest Performance Server Processor New AMD EPYC processor extends per socket performance leadership and best per core performance1** with new “Zen 3” cores and modern security features Partners including AWS, Cisco, Dell Technologies, Google Cloud, HPE, Lenovo, Microsoft Azure, Oracle Cloud Infrastructure, Supermicro, Tencent Cloud and others grow EPYC processor ecosystem to an expected 400 cloud instances and 100 new OEM platforms by end of 2021 SANTA CLARA, Calif., March 15, 2021 (GLOBE NEWSWIRE) -- At a digital event, AMD (NASDAQ: AMD) announced the new AMD EPYC™ 7003 Series CPUs, which includes the AMD EPYC 7763, the world’s highest-performing server processor2*. The new EPYC 7003 series processors help HPC, cloud and enterprise customers do more, faster, by delivering the best performance of any server CPU with up to 19% more instructions per clock3. “With the launch of our 3rd Gen AMD EPYC processors, we are incredibly excited to deliver the fastest server CPU in the world. These processors extend our data center leadership and help customers solve today’s most complex IT challenges, while substantially growing our ecosystem,” said Forrest Norrod, senior vice president and general manager, Data Center and Embedded Solutions Business Group. “We not only double the performance over the competition in HPC, cloud and enterprise workloads with our newest server CPUs, but together with the AMD Instinct GPUs, we are breaking the exascale barrier in supercomputing and helping to tackle problems that have previously been beyond humanity’s reach.” AMD EPYC Processors, Powering the Modern Data Center Available immediately, AMD EPYC 7003 Series Processors have up to 64 “Zen 3” cores per processor and introduce new levels of per-core cache memory, while continuing to offer the PCIe® 4 connectivity and class-leading memory bandwidth4 that defined the EPYC 7002 series CPUs. -

Guía Sobre Tiflotecnología Y Tecnología De Apoyo Para Uso

Guía sobre Tiflotecnología y Tecnología de Apoyo para uso educativo (Última actualización: febrero 2016) Guía sobre Tiflotecnología y Tecnología de Apoyo para uso educativo ÍNDICE INTRODUCCIÓN ..................................................................................................................................... 6 CONOCIMIENTOS BÁSICOS .................................................................................................................. 11 DEFINICIONES.................................................................................................................................... 11 HARDWARE ....................................................................................................................................... 14 SOFTWARE ........................................................................................................................................ 18 OTROS DISPOSITIVOS ........................................................................................................................ 19 SISTEMA OPERATIVO (VERSIONES) WINDOWS, OS X, IOS, ANDROID, WINDOWS MOBILE, LINUX ........ 22 WINDOWS ......................................................................................................................................... 23 OS X ................................................................................................................................................... 25 LINUX ............................................................................................................................................... -

Amd's Commitment To

This presentation contains forward-looking statements concerning Advanced Micro Devices, Inc. (AMD) such as AMD’s journey; the proposed transaction with Xilinx, Inc. including expectations, benefits and plans of the proposed transaction; total addressable markets; AMD’s technology roadmaps; the features, functionality, performance, availability, timing and expected benefits of future AMD products; AMD’s path forward in data center, PCs and gaming; and AMD’s 2021 financial outlook, long-term financial model and ability to drive shareholder returns, which are made pursuant to the Safe Harbor provisions of the Private Securities Litigation Reform Act of 1995. Forward looking statements are commonly identified by words such as "would," "may," "expects," "believes," "plans," "intends," "projects" and other terms with similar meaning. Investors are cautioned that the forward- looking statements in this presentation are based on current beliefs, assumptions and expectations, speak only as of the date of this presentation and involve risks and uncertainties that could cause actual results to differ materially from current expectations. Such statements are subject to certain known and unknown risks and uncertainties, many of which are difficult to predict and generally beyond AMD's control, that could cause actual results and other future events to differ materially from those expressed in, or implied or projected by, the forward-looking information and statements. Investors are urged to review in detail the risks and uncertainties in AMD’s Securities and Exchange Commission filings, including but not limited to AMD’s most recent reports on Forms 10-K and 10-Q. AMD does not assume, and hereby disclaims, any obligation to update forward-looking statements made in this presentation, except as may be required by law. -

AMD Announces World's Best Mobile Processors¹ in CES 2021 Keynote

January 12, 2021 AMD Announces World’s Best Mobile Processors¹ In CES 2021 Keynote AMD Ryzen Threadripper PRO Processors, designed for the most demanding professional workloads, coming to retail channel SANTA CLARA, Calif., Jan. 12, 2021 (GLOBE NEWSWIRE) -- CES 2021 -- Today, AMD (NASDAQ: AMD) announced the full portfolio of AMD Ryzen™ 5000 Series Mobile Processors, bringing the highly-efficient and extremely powerful “Zen 3” core architecture to the laptop market. New AMD Ryzen 5000 Series Mobile Processors provide unprecedented levels of performance and incredible battery life for gamers, creators, and professionals. New laptops powered by Ryzen 5000 Series Mobile processors will be available from major PC manufacturers including ASUS, HP and Lenovo, starting in Q1 2021. Expanding its leadership client computing product portfolio featuring the “Zen 3” core, AMD also announced the AMD Ryzen PRO 5000 Series Mobile Processors, delivering enterprise- grade security and seamless manageability to commercial users. Throughout the course of 2021, AMD expects a broad portfolio of more than 150 consumer and commercial notebooks based on the Ryzen 5000 Series Mobile Processors. “As the PC becomes an even more essential part of how we work, play and connect, users demand more performance, security and connectivity,” said Saeid Moshkelani, senior vice president and general manager, Client business unit, AMD. “The new AMD Ryzen 5000 Series Desktop and Mobile Processors bring the best innovation AMD has to offer to consumers and professionals as we continue our commitment to delivering best-in-class experiences with instant responsiveness, incredible battery life and fantastic designs. With our PC partners, we are delivering top-quality performance and no-compromise solutions alongside our record-breaking growth in the notebook and desktop space in the previous year.” AMD Ryzen 5000 Series Mobile Processors Building upon the previous generation of leadership mobile processors, the Ryzen 5000 Series includes high-performance H- and ultra-mobile U-Series processors. -

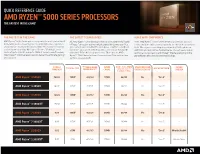

Amd Ryzen™ 5000 Series Processors the Fastest in the Game1

QUICK REFERENCE GUIDE AMD RYZEN™ 5000 SERIES PROCESSORS THE FASTEST IN THE GAME1 THE FASTEST IN THE GAME1 THE LATEST TECHNOLOGIES BUILD WITH CONFIDENCE AMD Ryzen™ 5000 Series processors power the next generation of All AMD RyzenTM 5000 Series processors come with the full suite With AMD RyzenTM 5000 Series desktop processors, you can demanding games, providing one of a kind immersive experiences of Ryzen™ processor technologies designed to elevate your PC’s easily configure and customize your rig for the ultimate gaming and dominate any multithreaded task like 3D and video rendering, processing power including Precision Boost 2 and Precision Boost build. These processors drop-in ready with a BIOS update on and software compiling. With up to 16 cores, 32 threads, boost Overdrive3. Also get maximum graphics and storage bandwidth AMD 500 and 400 Series motherboards. You can easily tweak 2 clocks of up to 4.9GHz and up to 72MB of cache in select models, with these PCIe® 4.0 ready processors. That's not all, AMD and tune your processor with Ryzen™ Master and jump in the TM AMD Ryzen 5000 Series processors deliver the ultimate gaming RyzenTM 5000 Series features the exceptional 7nm architecture game faster with AMD StoreMI technology. performance. performance-per-watt. CORES/ UP TOMAX/BASE TOTAL PCIE® 4.0 LANES UNLOCKED FOR IN BOX THREADS TYPICAL TDP FREQUENCY2,4 CACHE WITH X570 CHIPSET OVERCLOCKING5 ARCHITECTURE COOLER (USABLE / TOTAL) AMD Ryzen™ 9 5950X 16/32 105W 4.9/3.4 72MB 36/44 Yes "Zen 3" - AMD Ryzen™ 9 3950X 16/32 105W 4.7/3.5 72MB -

Amd Ryzentm 5000 Series Mobile Processors

AMD RYZENTM 5000 SERIES MOBILE PROCESSORS ELEVATING BUSINESS COMPUTING BUILT FOR SUCCESS AMD Ryzen™ 5000 Series Mobile Processors offer the advanced technology you need to stay ahead of the competition. Built on up to 7nm “Zen 3” architecture AMD Ryzen™ is the only processor Up to 90% higher multi-thread for processor performance leadership and family with up to 8 high performance performance vs the competition.2 incredible battery life. X86 cores for ultrathin notebooks.1 POWERHOUSE PRODUCTIVITY Whether working from office, huddle room, home or hotel, stay productive everywhere with the winning performance offered by AMD Ryzen™ 5000 series mobile processors. AMD RyzenTM 7 5800U Performance +90% +49% +30% +23% Up to +2% +9% .......................................................................................................................................................................................................... Cinebench R20 Single Cinebench R20 Multi- GeekBench v5 PassMark 10 PCMark 10 Benchmark MS Office Overall Thread Thread Multi-Core CPU Mark PCMark 10 Apps Intel Core i7-1165G7 RyzenTM 7 5800U See endnote 2 AMD RyzenTM 5 5600U Performance +90% +43% Up to +29% +5% +19% +8% .......................................................................................................................................................................................................... Cinebench R20 Single Cinebench R20 Multi- GeekBench v5 PassMark 10 PCMark 10 Benchmark MS Office Overall Thread Thread Multi-Core CPU Mark PCMark 10 Apps