Ryzen 3 3200G Overclock Settings

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Improving Resource Utilization in Heterogeneous CPU-GPU Systems

Improving Resource Utilization in Heterogeneous CPU-GPU Systems A Dissertation Presented to the Faculty of the School of Engineering and Applied Science University of Virginia In Partial Fulfillment of the requirements for the Degree Doctor of Philosophy (Computer Engineering) by Michael Boyer May 2013 c 2013 Michael Boyer Abstract Graphics processing units (GPUs) have attracted enormous interest over the past decade due to substantial increases in both performance and programmability. Programmers can potentially leverage GPUs for substantial performance gains, but at the cost of significant software engineering effort. In practice, most GPU applications do not effectively utilize all of the available resources in a system: they either fail to use use a resource at all or use a resource to less than its full potential. This underutilization can hurt both performance and energy efficiency. In this dissertation, we address the underutilization of resources in heterogeneous CPU-GPU systems in three different contexts. First, we address the underutilization of a single GPU by reducing CPU-GPU interaction to improve performance. We use as a case study a computationally-intensive video-tracking application from systems biology. Because of the high cost of CPU-GPU coordination, our initial, straightforward attempts to accelerate this application failed to effectively utilize the GPU. By leveraging some non-obvious optimization strategies, we significantly decreased the amount of CPU-GPU interaction and improved the performance of the GPU implementation by 26x relative to the best CPU implementation. Based on the lessons we learned, we present general guidelines for optimizing GPU applications as well as recommendations for system-level changes that would simplify the development of high-performance GPU applications. -

Application-Controlled Frequency Scaling Explained

The TURBO Diaries: Application-controlled Frequency Scaling Explained Jons-Tobias Wamhoff, Stephan Diestelhorst, and Christof Fetzer, Technische Universät Dresden; Patrick Marlier and Pascal Felber, Université de Neuchâtel; Dave Dice, Oracle Labs https://www.usenix.org/conference/atc14/technical-sessions/presentation/wamhoff This paper is included in the Proceedings of USENIX ATC ’14: 2014 USENIX Annual Technical Conference. June 19–20, 2014 • Philadelphia, PA 978-1-931971-10-2 Open access to the Proceedings of USENIX ATC ’14: 2014 USENIX Annual Technical Conference is sponsored by USENIX. The TURBO Diaries: Application-controlled Frequency Scaling Explained Jons-Tobias Wamhoff Patrick Marlier Dave Dice Stephan Diestelhorst Pascal Felber Christof Fetzer Technische Universtat¨ Dresden, Germany Universite´ de Neuchatel,ˆ Switzerland Oracle Labs, USA Abstract these features from an application as needed. Examples in- Most multi-core architectures nowadays support dynamic volt- clude: accelerating the execution of key sections of code on age and frequency scaling (DVFS) to adapt their speed to the the critical path of multi-threaded applications [9]; boosting system’s load and save energy. Some recent architectures addi- time-critical operations or high-priority threads; or reducing tionally allow cores to operate at boosted speeds exceeding the the energy consumption of applications executing low-priority nominal base frequency but within their thermal design power. threads. Furthermore, workloads specifically designed to run In this paper, we propose a general-purpose library that on processors with heterogeneous cores (e.g., few fast and allows selective control of DVFS from user space to accelerate many slow cores) may take additional advantage of application- multi-threaded applications and expose the potential of hetero- level frequency scaling. -

Die Meilensteine Der Computer-, Elek

Das Poster der digitalen Evolution – Die Meilensteine der Computer-, Elektronik- und Telekommunikations-Geschichte bis 1977 1977 1978 1979 1980 1981 1982 1983 1984 1985 1986 1987 1988 1989 1990 1991 1992 1993 1994 1995 1996 1997 1998 1999 2000 2001 2002 2003 2004 2005 2006 2007 2008 2009 2010 2011 2012 2013 2014 2015 2016 2017 2018 2019 2020 und ... Von den Anfängen bis zu den Geburtswehen des PCs PC-Geburt Evolution einer neuen Industrie Business-Start PC-Etablierungsphase Benutzerfreundlichkeit wird gross geschrieben Durchbruch in der Geschäftswelt Das Zeitalter der Fensterdarstellung Online-Zeitalter Internet-Hype Wireless-Zeitalter Web 2.0/Start Cloud Computing Start des Tablet-Zeitalters AI (CC, Deep- und Machine-Learning), Internet der Dinge (IoT) und Augmented Reality (AR) Zukunftsvisionen Phasen aber A. Bowyer Cloud Wichtig Zählhilfsmittel der Frühzeit Logarithmische Rechenhilfsmittel Einzelanfertigungen von Rechenmaschinen Start der EDV Die 2. Computergeneration setzte ab 1955 auf die revolutionäre Transistor-Technik Der PC kommt Jobs mel- All-in-One- NAS-Konzept OLPC-Projekt: Dass Computer und Bausteine immer kleiner, det sich Konzepte Start der entwickelt Computing für die AI- schneller, billiger und energieoptimierter werden, Hardware Hände und Finger sind die ersten Wichtige "PC-Vorläufer" finden wir mit dem werden Massenpro- den ersten Akzeptanz: ist bekannt. Bei diesen Visionen geht es um die Symbole für die Mengendarstel- schon sehr früh bei Lernsystemen. iMac und inter- duktion des Open Source Unterstüt- möglichen zukünftigen Anwendungen, die mit 3D-Drucker zung und lung. Ägyptische Illustration des Beispiele sind: Berkley Enterprice mit neuem essant: XO-1-Laptops: neuen Technologien und Konzepte ermöglicht Veriton RepRap nicht Ersatz werden. -

AMD's Early Processor Lines, up to the Hammer Family (Families K8

AMD’s early processor lines, up to the Hammer Family (Families K8 - K10.5h) Dezső Sima October 2018 (Ver. 1.1) Sima Dezső, 2018 AMD’s early processor lines, up to the Hammer Family (Families K8 - K10.5h) • 1. Introduction to AMD’s processor families • 2. AMD’s 32-bit x86 families • 3. Migration of 32-bit ISAs and microarchitectures to 64-bit • 4. Overview of AMD’s K8 – K10.5 (Hammer-based) families • 5. The K8 (Hammer) family • 6. The K10 Barcelona family • 7. The K10.5 Shanghai family • 8. The K10.5 Istambul family • 9. The K10.5-based Magny-Course/Lisbon family • 10. References 1. Introduction to AMD’s processor families 1. Introduction to AMD’s processor families (1) 1. Introduction to AMD’s processor families AMD’s early x86 processor history [1] AMD’s own processors Second sourced processors 1. Introduction to AMD’s processor families (2) Evolution of AMD’s early processors [2] 1. Introduction to AMD’s processor families (3) Historical remarks 1) Beyond x86 processors AMD also designed and marketed two embedded processor families; • the 2900 family of bipolar, 4-bit slice microprocessors (1975-?) used in a number of processors, such as particular DEC 11 family models, and • the 29000 family (29K family) of CMOS, 32-bit embedded microcontrollers (1987-95). In late 1995 AMD cancelled their 29K family development and transferred the related design team to the firm’s K5 effort, in order to focus on x86 processors [3]. 2) Initially, AMD designed the Am386/486 processors that were clones of Intel’s processors. -

AMD EPYC™ 7003 Series Cpus Set New Standard As Highest Performance Server Processor

March 15, 2021 AMD EPYC™ 7003 Series CPUs Set New Standard as Highest Performance Server Processor New AMD EPYC processor extends per socket performance leadership and best per core performance1** with new “Zen 3” cores and modern security features Partners including AWS, Cisco, Dell Technologies, Google Cloud, HPE, Lenovo, Microsoft Azure, Oracle Cloud Infrastructure, Supermicro, Tencent Cloud and others grow EPYC processor ecosystem to an expected 400 cloud instances and 100 new OEM platforms by end of 2021 SANTA CLARA, Calif., March 15, 2021 (GLOBE NEWSWIRE) -- At a digital event, AMD (NASDAQ: AMD) announced the new AMD EPYC™ 7003 Series CPUs, which includes the AMD EPYC 7763, the world’s highest-performing server processor2*. The new EPYC 7003 series processors help HPC, cloud and enterprise customers do more, faster, by delivering the best performance of any server CPU with up to 19% more instructions per clock3. “With the launch of our 3rd Gen AMD EPYC processors, we are incredibly excited to deliver the fastest server CPU in the world. These processors extend our data center leadership and help customers solve today’s most complex IT challenges, while substantially growing our ecosystem,” said Forrest Norrod, senior vice president and general manager, Data Center and Embedded Solutions Business Group. “We not only double the performance over the competition in HPC, cloud and enterprise workloads with our newest server CPUs, but together with the AMD Instinct GPUs, we are breaking the exascale barrier in supercomputing and helping to tackle problems that have previously been beyond humanity’s reach.” AMD EPYC Processors, Powering the Modern Data Center Available immediately, AMD EPYC 7003 Series Processors have up to 64 “Zen 3” cores per processor and introduce new levels of per-core cache memory, while continuing to offer the PCIe® 4 connectivity and class-leading memory bandwidth4 that defined the EPYC 7002 series CPUs. -

Amd's Commitment To

This presentation contains forward-looking statements concerning Advanced Micro Devices, Inc. (AMD) such as AMD’s journey; the proposed transaction with Xilinx, Inc. including expectations, benefits and plans of the proposed transaction; total addressable markets; AMD’s technology roadmaps; the features, functionality, performance, availability, timing and expected benefits of future AMD products; AMD’s path forward in data center, PCs and gaming; and AMD’s 2021 financial outlook, long-term financial model and ability to drive shareholder returns, which are made pursuant to the Safe Harbor provisions of the Private Securities Litigation Reform Act of 1995. Forward looking statements are commonly identified by words such as "would," "may," "expects," "believes," "plans," "intends," "projects" and other terms with similar meaning. Investors are cautioned that the forward- looking statements in this presentation are based on current beliefs, assumptions and expectations, speak only as of the date of this presentation and involve risks and uncertainties that could cause actual results to differ materially from current expectations. Such statements are subject to certain known and unknown risks and uncertainties, many of which are difficult to predict and generally beyond AMD's control, that could cause actual results and other future events to differ materially from those expressed in, or implied or projected by, the forward-looking information and statements. Investors are urged to review in detail the risks and uncertainties in AMD’s Securities and Exchange Commission filings, including but not limited to AMD’s most recent reports on Forms 10-K and 10-Q. AMD does not assume, and hereby disclaims, any obligation to update forward-looking statements made in this presentation, except as may be required by law. -

Amd Power Management Srilatha Manne 11/14/2013 Outline

AMD POWER MANAGEMENT SRILATHA MANNE 11/14/2013 OUTLINE APUs and HSA Richland APU APU Power Management Monitoring and Management Features 2 | DOE WEBINAR| NOV 14, 2013 APU: ACCELERATED PROCESSING UNIT The APU has arrived and it is a great advance over previous platforms Combines scalar processing on CPU with parallel processing on the GPU and high-bandwidth access to memory Advantages over other forms of compute offload: Easier to program Easier to optimize Easier to load-balance Higher performance Lower power © Copyright 2012 HSA Foundation. All Rights Reserved. 3 WHAT IS HSA? Joins CPUs, GPUs, and accelerators into a unified computing framework Single address space accessible to avoid the overhead of data copying HSA Accelerated Applications Access to Broad Set of Programming Use-space queuing to minimize Languages communication overhead Pre-emptive context switching for better Legacy quality of service Applications Simplified programming HSA Runtime Single, standard computing environments Infrastructure Support for mainstream languages— OS C, C++, Fortran, Java, .NET Lower development costs Memory Optimized compute density Radical performance improvement for CPU GPU ACC HPC, big data, and multimedia workloads HSA Platform Low power to maximize performance per watt 4 | AMD OPTERON™ PROCESSOR ROADMAP | NOVEMBER 13, 2013 A NEW ERA OF PROCESSOR PERFORMANCE Heterogeneous Single-core Era Multi-core Era Systems Era Temporarily Enabled by: Constrained by: Enabled by: Constrained by: Enabled by: Moore’s Power Moore’s Law Power Abundant data Constrained by: Law Complexity SMP Parallel SW parallelism Programming Voltage architecture Scalability Power efficient models Scaling GPUs Comm.overhead pthreads OpenMP / TBB … Assembly C/C++ Java Shader CUDA OpenCL … C++ and Java ? we are here we are Performance Performance here Throughput Performance Performance we are Modern Modern Application here Single-thread Single-thread Performance Time Time (# of processors) Time (Data-parallel exploitation) © Copyright 2012 HSA Foundation. -

AMD Announces World's Best Mobile Processors¹ in CES 2021 Keynote

January 12, 2021 AMD Announces World’s Best Mobile Processors¹ In CES 2021 Keynote AMD Ryzen Threadripper PRO Processors, designed for the most demanding professional workloads, coming to retail channel SANTA CLARA, Calif., Jan. 12, 2021 (GLOBE NEWSWIRE) -- CES 2021 -- Today, AMD (NASDAQ: AMD) announced the full portfolio of AMD Ryzen™ 5000 Series Mobile Processors, bringing the highly-efficient and extremely powerful “Zen 3” core architecture to the laptop market. New AMD Ryzen 5000 Series Mobile Processors provide unprecedented levels of performance and incredible battery life for gamers, creators, and professionals. New laptops powered by Ryzen 5000 Series Mobile processors will be available from major PC manufacturers including ASUS, HP and Lenovo, starting in Q1 2021. Expanding its leadership client computing product portfolio featuring the “Zen 3” core, AMD also announced the AMD Ryzen PRO 5000 Series Mobile Processors, delivering enterprise- grade security and seamless manageability to commercial users. Throughout the course of 2021, AMD expects a broad portfolio of more than 150 consumer and commercial notebooks based on the Ryzen 5000 Series Mobile Processors. “As the PC becomes an even more essential part of how we work, play and connect, users demand more performance, security and connectivity,” said Saeid Moshkelani, senior vice president and general manager, Client business unit, AMD. “The new AMD Ryzen 5000 Series Desktop and Mobile Processors bring the best innovation AMD has to offer to consumers and professionals as we continue our commitment to delivering best-in-class experiences with instant responsiveness, incredible battery life and fantastic designs. With our PC partners, we are delivering top-quality performance and no-compromise solutions alongside our record-breaking growth in the notebook and desktop space in the previous year.” AMD Ryzen 5000 Series Mobile Processors Building upon the previous generation of leadership mobile processors, the Ryzen 5000 Series includes high-performance H- and ultra-mobile U-Series processors. -

PAP Advanced Computer Architectures 1 ISA Development History

Advanced Computer Architectures History and Future Czech Technical University in Prague, Faculty of Electrical Engineering Slides authors: Michal Štepanovský, update Pavel Píša B4M35PAP Advanced Computer Architectures 1 ISA development history 1936 Alan Turing: On computable numbers, with an application to 1939 Bombe: the Entscheidungsproblem designed to crack 1937: Howard Aiken: Concept of Enigma Automatic Sequence Controlled 1941 Konrad Zuse: Calculator – ASCC. Z3 – the world first 1945 John von Neumann: First functional Turing Draft of a Report on the EDVAC. complete computer, New idea: Stored-program program controlled computer. Previous computers 1944 Harvard Mark I required to physically modified to 1944 Colossus for given task. Remark: stored- 1946 ENIAC program idea appeared even 1947 Transistor earlier in 1943 year – ENIAC 1948 Manchester development: J. P. Eckert a J. Baby – the first stored- Mauchly program computer 1949 EDSAC – Computers of that era are single accumulator equipped by accumulator (one 1953 EDSAC, register) for arithmetic and logic Manchester Mark I, operations which is fixed IBM 700 series: single accumulator destination and one of source + index register operands. 2 B4M35PAP Advanced Computer Architectures 2 ISA development history 1954 John Backus: FORTRAN (FOrmula TRANslator) language There is a significant separation of the programming model from 1958: JohnMcCarthy: LSP (LISt implementation !!! Processing) language 1961 B5000: Computer designed and 1960 ALGOL (ALGOrithmic Language) optimized for ALGOL 60 -

Energy-Aware Resource Management for Heterogeneous Systems

FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO Energy-aware resource management for heterogeneous systems Eduardo Fernandes Mestrado Integrado em Engenharia Informática e Computação Supervisor: Jorge Barbosa July 7, 2016 Energy-aware resource management for heterogeneous systems Eduardo Fernandes Mestrado Integrado em Engenharia Informática e Computação July 7, 2016 Abstract Nowadays computers, be they personal or a node contained in a multi machine environment, can contain different kinds of processing units. A common example is the personal computer that nowadays always includes a CPU and a GPU, both capable of executing code, sometimes even in the same integrated circuit package. These are the so called heterogeneous systems. It’s important to be aware that the various processing units aren’t equal, for instance CPUs are very different from GPUs. This raises a problem, since not every task can be executed in all processing units. To solve this problem a new task scheduling algorithm was developed with the aid of SimDag from the SimGrid toolkit. This algorithm uses a DAG (directed acyclic graph) to aid the scheduling of different tasks, be they from a single application or from various different applications. The algorithm is based on the HEFT scheduling algorithm, a greedy algorithm with a short execution time, developed by Topcuoglu et al. This new algorithm is aware of the different pro- cessing units and of the different performance/power levels. This solves the problem of not all tasks being able to be executed in all processing units. Since previous studies show that reducing the CPU clock speed on DVFS (dynamic voltage frequency scaling) CPUs can reduce the energy spent by the CPU while executing various tasks with little increase in runtime. -

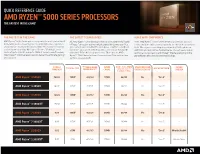

Amd Ryzen™ 5000 Series Processors the Fastest in the Game1

QUICK REFERENCE GUIDE AMD RYZEN™ 5000 SERIES PROCESSORS THE FASTEST IN THE GAME1 THE FASTEST IN THE GAME1 THE LATEST TECHNOLOGIES BUILD WITH CONFIDENCE AMD Ryzen™ 5000 Series processors power the next generation of All AMD RyzenTM 5000 Series processors come with the full suite With AMD RyzenTM 5000 Series desktop processors, you can demanding games, providing one of a kind immersive experiences of Ryzen™ processor technologies designed to elevate your PC’s easily configure and customize your rig for the ultimate gaming and dominate any multithreaded task like 3D and video rendering, processing power including Precision Boost 2 and Precision Boost build. These processors drop-in ready with a BIOS update on and software compiling. With up to 16 cores, 32 threads, boost Overdrive3. Also get maximum graphics and storage bandwidth AMD 500 and 400 Series motherboards. You can easily tweak 2 clocks of up to 4.9GHz and up to 72MB of cache in select models, with these PCIe® 4.0 ready processors. That's not all, AMD and tune your processor with Ryzen™ Master and jump in the TM AMD Ryzen 5000 Series processors deliver the ultimate gaming RyzenTM 5000 Series features the exceptional 7nm architecture game faster with AMD StoreMI technology. performance. performance-per-watt. CORES/ UP TOMAX/BASE TOTAL PCIE® 4.0 LANES UNLOCKED FOR IN BOX THREADS TYPICAL TDP FREQUENCY2,4 CACHE WITH X570 CHIPSET OVERCLOCKING5 ARCHITECTURE COOLER (USABLE / TOTAL) AMD Ryzen™ 9 5950X 16/32 105W 4.9/3.4 72MB 36/44 Yes "Zen 3" - AMD Ryzen™ 9 3950X 16/32 105W 4.7/3.5 72MB -

Amd Ryzentm 5000 Series Mobile Processors

AMD RYZENTM 5000 SERIES MOBILE PROCESSORS ELEVATING BUSINESS COMPUTING BUILT FOR SUCCESS AMD Ryzen™ 5000 Series Mobile Processors offer the advanced technology you need to stay ahead of the competition. Built on up to 7nm “Zen 3” architecture AMD Ryzen™ is the only processor Up to 90% higher multi-thread for processor performance leadership and family with up to 8 high performance performance vs the competition.2 incredible battery life. X86 cores for ultrathin notebooks.1 POWERHOUSE PRODUCTIVITY Whether working from office, huddle room, home or hotel, stay productive everywhere with the winning performance offered by AMD Ryzen™ 5000 series mobile processors. AMD RyzenTM 7 5800U Performance +90% +49% +30% +23% Up to +2% +9% .......................................................................................................................................................................................................... Cinebench R20 Single Cinebench R20 Multi- GeekBench v5 PassMark 10 PCMark 10 Benchmark MS Office Overall Thread Thread Multi-Core CPU Mark PCMark 10 Apps Intel Core i7-1165G7 RyzenTM 7 5800U See endnote 2 AMD RyzenTM 5 5600U Performance +90% +43% Up to +29% +5% +19% +8% .......................................................................................................................................................................................................... Cinebench R20 Single Cinebench R20 Multi- GeekBench v5 PassMark 10 PCMark 10 Benchmark MS Office Overall Thread Thread Multi-Core CPU Mark PCMark 10 Apps