Advancing Silicon Performance Beyond the Capabilities of Discrete

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

MW6IC2420NBR1 2450 Mhz, 20 W, 28 V CW RF LDMOS Integrated

Freescale Semiconductor Document Number: MW6IC2420N Technical Data Rev. 3, 12/2010 RF LDMOS Integrated Power Amplifier MW6IC2420NBR1 The MW6IC2420NB integrated circuit is designed with on--chip matching that makes it usable at 2450 MHz. This multi--stage structure is rated for 26 to 32 Volt operation and covers all typical industrial, scientific and medical modulation formats. 2450 MHz, 20 W, 28 V Driver Applications CW • Typical CW Performance at 2450 MHz: VDD =28Volts,IDQ1 = 210 mA, RF LDMOS INTEGRATED POWER I = 370 mA, P = 20 Watts DQ2 out AMPLIFIER Power Gain — 19.5 dB Power Added Efficiency — 27% • Capable of Handling 3:1 VSWR, @ 28 Vdc, 2170 MHz, 20 Watts CW Output Power • Stable into a 3:1 VSWR. All Spurs Below --60 dBc @ 100 mW to 10 Watts CW Pout. Features Y • Characterized with Series Equivalent Large--Signal Impedance Parameters and Common Source Scattering Parameters • On--Chip Matching (50 Ohm Input, DC Blocked, >3 Ohm Output) • Integrated Quiescent Current Temperature Compensation with Enable/Disable Function (1) • Integrated ESD Protection CASE 1329--09 • 225°C Capable Plastic Package TO--272 WB--16 • RoHS Compliant PLASTIC • In Tape and Reel. R1 Suffix = 500 Units, 44 mm Tape Width, 13 inch Reel GND 1 16 GND VDS1 2 NC 3 15 NC NC 4 LIFETIME BU VDS1 NC 5 RF / RFin 6 14 out RFin RFout/VDS2 VDS2 NC 7 VGS1 8 VGS2 9 VGS1 Quiescent Current VDS1 10 13 NC (1) VGS2 Temperature Compensation GND 11 12 GND VDS1 (Top View) Note: Exposed backside of the package is the source terminal for the transistors. -

Failure Precursors for Insulated Gate Bipolar Transistors (Igbts) Nishad Patil1, Diganta Das1, Kai Goebel2 and Michael Pecht1

Failure Precursors for Insulated Gate Bipolar Transistors (IGBTs) 1 1 2 1 Nishad Patil , Diganta Das , Kai Goebel and Michael Pecht 1Center for Advanced Life Cycle Engineering (CALCE) University of Maryland College Park, MD 20742, USA 2NASA Ames Research Center Moffett Field, CA 94035, USA Abstract Failure precursors indicate changes in a measured variable that can be associated with impending failure. By identifying precursors to failure and by monitoring them, system failures can be predicted and actions can be taken to mitigate their effects. In this study, three potential failure precursor candidates, threshold voltage, transconductance, and collector-emitter ON voltage, are evaluated for insulated gate bipolar transistors (IGBTs). Based on the failure causes determined by the failure modes, mechanisms and effects analysis (FMMEA), IGBTs are aged using electrical-thermal stresses. The three failure precursor candidates of aged IGBTs are compared with new IGBTs under a temperature range of 25-200oC. The trends in the three electrical parameters with changes in temperature are correlated to device degradation. A methodology is presented for validating these precursors for IGBT prognostics using a hybrid approach. Keywords: Failure precursors, IGBTs, prognostics Failure precursors indicate changes in a measured variable structure of an IGBT is similar to that of a vertical that can be associated with impending failure [1]. A diffusion power MOSFET (VDMOS) [3] except for an systematic method for failure precursor selection is additional p+ layer above the collector as seen in Figure 1. through the use of the failure modes, mechanisms, and The main characteristic of the vertical configuration is that effects analysis (FMMEA) [2]. -

RF LDMOS/EDMOS: Embedded Devices for Highly Integrated Solutions

RF LDMOS/EDMOS: embedded devices for highly integrated solutions T. Letavic, C. Li, M. Zierak, N. Feilchenfeld, M. Li, S. Zhang, P. Shyam, V. Purakh Outline • PowerSoc systems and product drivers – Systems that benefit from embedded power supplies also require .. • Ubiquitous wireless connectivity – RF integration (802.11.54, BTLE, BT, WPAN, …) • MCU + memory – code, actuation, network configuration – IoT network edge node = miniaturized embedded power supply and RF link • PowerSoC and RF device integration strategies – 180nm bulk-Si mobile power management process – LDMOS – 55nm bulk-Si silicon IoT platform – EDMOS – DC and RF benchmark to 5V CMOS • Power and RF application characterization – ISM bands, WiFi, performance against cellular industry standards – Embedded power and RF with the same device unit cell • Summary – PowerSoc and RF use the same device unit cell 2 Embedded power and RF: Envelope Tracking https://www.nujira.com Motorola eg. US 6,407,634 B1, US 6,617,920 B2 • RF supply modulation to reduce power dissipation (WiFi, 4G LTE) – Linear amplifier: 5Vpk-pk 80 MHz BW, >16QAM -> fT > 20 Ghz – SMPS: > 10-20 MHz fsw, 5-7 V FSOA, ultra-low Rsp*Qgg FOM • Optimal solution fT/fmax of cSiGe/GaN/GaAs with Si BCD voltage handling – RF LDMOS and RF EDMOS are challenging the incumbents …. 3 Embedded Power and RF: IoT Edge Node Semtech integrated RF transceiver SX123SX • Wireless IEEE 802.15.4, IEEE 802.11.ah, 2G/3G/4G LTE MTC, …. – 50 B connected endpoints 2020 (Cisco Mobility Report Dec 2016) – Integrated low power RF modem + PA, SMPS, -

Gan Or Gaas, TWT Or Klystron - Testing High Power Amplifiers for RADAR Signals Using Peak Power Meters

Application Note GaN or GaAs, TWT or Klystron - Testing High Power Amplifiers for RADAR Signals using Peak Power Meters Vitali Penso Applications Engineer, Boonton Electronics Abstract Measuring and characterizing pulsed RF signals used in radar applications present unique challenges. Unlike communication signals, pulsed radar signals are “on” for a short time followed by a long “off” period, during “on” time the system transmits anywhere from kilowatts to megawatts of power. The high power pulsing can stress the power amplifier (PA) in a number of ways both during the on/off transitions and during prolonged “on” periods. As new PA device technologies are introduced, latest one being GaN, the behavior of the amplifier needs to be thoroughly tested and evaluated. Given the time domain nature of the pulsed RF signal, the best way to observe the performance of the amplifier is through time domain signal analysis. This article explains why the peak power meter is a must have test instrument for characterizing the behavior of pulsed RF power amplifiers (PA) used in radar systems. Radar Power Amplifier Technology Overview Peak Power Meter for Pulsed RADAR Measurements Before we look at the peak power meter and its capabilities, let’s The most critical analysis of the pulsed RF signal takes place in the look at different technologies used in high power amplifiers (HPA) time domain. Since peak power meters measure, analyze and dis- for RADAR systems, particularly GaN on SiC, and why it has grabbed play the power envelope of a RF signal in the time domain, they the attention over the past decade. -

Quiescent Current Control for the RF Integrated Circuit Device Family

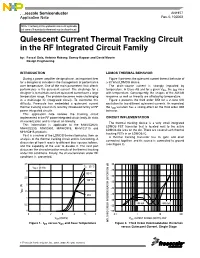

Freescale Semiconductor AN1977 Application Note Rev. 0, 10/2003 NOTE: The theory in this application note is still applicable, but some of the products referenced may be discontinued. Quiescent Current Thermal Tracking Circuit in the RF Integrated Circuit Family by: Pascal Gola, Antoine Rabany, Samay Kapoor and David Maurin Design Engineering INTRODUCTION LDMOS THERMAL BEHAVIOR During a power amplifier design phase, an important item Figure 1 presents the quiescent current thermal behavior of for a designer to consider is the management of performance a 30 Watt LDMOS device. over temperature. One of the main parameters that affects The drain-source current is strongly impacted by performance is the quiescent current. The challenge for a temperature. In Class AB and for a given VGS, the IDQ rises designer is to maintain constant quiescent current over a large with temperature. Consequently, the shapes of the AM/AM temperature range. The problem becomes more challenging response as well as linearity are affected by temperature. in a multistage IC (integrated circuit). To overcome this Figure 2 presents the third order IMD for a 2-tone CW difficulty, Freescale has embedded a quiescent current excitation for two different quiescent currents. As expected, thermal tracking circuit in its recently introduced family of RF the IDQ variation has a strong effect on the third order IMD power integrated circuits. behavior. This application note reviews the tracking circuit implemented in the RF power integrated circuit family, its static CIRCUIT IMPLEMENTATION characterization and its impact on linearity. The thermal tracking device is a very small integrated This information is applicable to the MW4IC2020, LDMOS FET transistor that is located next to the active MW4IC2230, MWIC930, MW4IC915, MHVIC2115 and LDMOS die area on the die. -

MOSFET - Wikipedia, the Free Encyclopedia

MOSFET - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/MOSFET MOSFET From Wikipedia, the free encyclopedia The metal-oxide-semiconductor field-effect transistor (MOSFET, MOS-FET, or MOS FET), is by far the most common field-effect transistor in both digital and analog circuits. The MOSFET is composed of a channel of n-type or p-type semiconductor material (see article on semiconductor devices), and is accordingly called an NMOSFET or a PMOSFET (also commonly nMOSFET, pMOSFET, NMOS FET, PMOS FET, nMOS FET, pMOS FET). The 'metal' in the name (for transistors upto the 65 nanometer technology node) is an anachronism from early chips in which the gates were metal; They use polysilicon gates. IGFET is a related, more general term meaning insulated-gate field-effect transistor, and is almost synonymous with "MOSFET", though it can refer to FETs with a gate insulator that is not oxide. Some prefer to use "IGFET" when referring to devices with polysilicon gates, but most still call them MOSFETs. With the new generation of high-k technology that Intel and IBM have announced [1] (http://www.intel.com/technology/silicon/45nm_technology.htm) , metal gates in conjunction with the a high-k dielectric material replacing the silicon dioxide are making a comeback replacing the polysilicon. Usually the semiconductor of choice is silicon, but some chip manufacturers, most notably IBM, have begun to use a mixture of silicon and germanium (SiGe) in MOSFET channels. Unfortunately, many semiconductors with better electrical properties than silicon, such as gallium arsenide, do not form good gate oxides and thus are not suitable for MOSFETs. -

AN5252 Low-Voltage Power MOSFET Switching Behavior And

AN5252 Application note Low-voltage Power MOSFET switching behavior and performance evaluation in motor control application topologies Introduction During the last years, some applications based on electrical power conversion are gaining more and more space in the civil and industrial fields. The constant development of microprocessors and the improvement of modulation techniques, which are useful for the control of power devices, have led to a more accurate control of the converted power as well as of the power dissipation, thus increasing the efficiency of the motor control applications. Nowdays, frequency modulation techniques are used to control the torque and the speed of brushless motors in several high- and low-voltage applications and in different circuit topologies using power switches in different technologies such as MOSFETs and IGBTs. Therefore, the devices have to guarantee the best electrical efficiency and the least possible impact in terms of emissions. The aim of this application note is to provide a description of the most important parameters which are useful for choosing a low- voltage Power MOSFET device for a motor control application. Three different motor control applications and topology cases are deeply analyzed to offer to motor drive designers the guidelines required for an efficient and reliable design when using the MOSFET technology in hard-switch applications: • BLDC motor in a 3-phase inverter topology • DC motor in H-bridge configuration • DC motor in single-switch configuration AN5252 - Rev 1 - November 2018 - By C. Mistretta and F. Scrimizzi www.st.com For further information contact your local STMicroelectronics sales office. AN5252 Control techniques and brushless DC (BLDC) motors 1 Control techniques and brushless DC (BLDC) motors During the last years, servomotors have evolved from mostly brush to brushless type. -

Design, Implementation, Modeling, and Optimization of Next Generation Low-Voltage Power Mosfets

Design, Implementation, Modeling, and Optimization of Next Generation Low-Voltage Power MOSFETs by Abraham Yoo A thesis submitted in conformity with the requirements for the degree of Doctor of Philosophy Department of Materials Science and Engineering University of Toronto © Copyright by Abraham Yoo 2010 Design, Implementation, Modeling, and Optimization of Next Generation Low-Voltage Power MOSFETs Abraham Yoo Doctor of Philosophy Department of Materials Science and Engineering University of Toronto 2010 Abstract In this thesis, next generation low-voltage integrated power semiconductor devices are proposed and analyzed in terms of device structure and layout optimization techniques. Both approaches strive to minimize the power consumption of the output stage in DC-DC converters. In the first part of this thesis, we present a low-voltage CMOS power transistor layout technique, implemented in a 0.25µm, 5 metal layer standard CMOS process. The hybrid waffle (HW) layout was designed to provide an effective trade-off between the width of diagonal source/drain metal and the active device area, allowing more effective optimization between switching and conduction losses. In comparison with conventional layout schemes, the HW layout exhibited a 30% reduction in overall on-resistance with 3.6 times smaller total gate charge for CMOS devices with a current rating of 1A. Integrated DC-DC buck converters using HW output stages were found to have higher efficiencies at switching frequencies beyond multi-MHz. ii In the second part of the thesis, we present a CMOS-compatible lateral superjunction FINFET (SJ-FINFET) on a SOI platform. One drawback associated with low-voltage SJ devices is that the on-resistance is not only strongly dependent on the drift doping concentration but also on the channel resistance as well. -

Ampleon Company Presentation

Microwave Journal Educational Webinar Ampleon Brings RF Power Innovations towards Industrial Heating Market Gerrit Huisman Robin Wesson Klaus Werner Nov, 17, 2016 Amplify the future | 1 Ampleon at a Glance Our Company Our Businesses • European Company / Headquarters in • Building transistors and other RF Power products Nijmegen/Netherlands for over 50 years • 1,250 employees globally in 18 sites • Industry Leader for 35 years, addressing • Worldwide Sales, Application and R&D – Mobile Broadband – Broadcast • Own manufacturing facility – Aerospace & Defense • Partnering with leading external manufacturers – ISM – RF Energy Technologies & Products Customers • Broad LDMOSTaco and GaN technology portfolio Reinier Zwemstra Beltman • Comprehensive package line-up • Chief Operations Head of Sales OutstandingOfficer product consistency Amplify the future | 2 Ampleon and RF Energy • Recognized as thought leader • Co-founder of RF Energy Alliance • Working with the leaders in new application domains Amplify the future | 3 RF Power Industrial market dominated by vacuum tubes • Current solutions mainly based on ‘old’ vacuum tube principles • Somewhat fragmented market with large and many small vendors – TWT (Traveling Wave Tubes) – Klystron – Magnetrons – CFA (Crossed Field Amplifiers) – Gyrotrons Amplify the future | 4 2020 TAM VED’s about ~$1B $1.2B in 2014 TAM VEDS Source ABI research TWT 63% Klystron 17% Gyrotron 3% magnetron Cross Field 15% 2% Not included: domestic magnetrons, Aerospace market Amplify the future | 5 Solid state penetrates the -

50V RF LDMOS an Ideal RF Power Technology for ISM, Broadcast and Commercial Aerospace Applications Freescale.Com/Rfpower I

White Paper 50V RF LDMOS An ideal RF power technology for ISM, broadcast and commercial aerospace applications freescale.com/RFpower I. INTRODUCTION RF laterally diffused MOS (LDMOS) is currently the dominant device technology used in high-power RF power amplifier (PA) applications for frequencies ranging from 1 MHz to greater than 3.5 GHz. Beginning in the early 1990s, LDMOS has gained wide acceptance for cellular infrastructure PA applications, and now is the dominant RF power device technology for cellular infrastructure. This device technology offered significant advantages over the previous incumbent device technology, the silicon bipolar transistor, providing superior linearity, efficiency, gain and lower cost packaging options. LDMOS technology has continued to evolve to meet the ever more demanding requirements of the cellular infrastructure market, achieving higher levels of efficiency, gain, power and operational frequency[1-8]. The LDMOS device structure is highly flexible. While the cellular infrastructure market has standardized on 28–32V operation, several years ago Freescale developed 50V processes for applications outside of cellular infrastructure. These 50V devices are targeted for use in a wide variety of applications where high power density is a key differentiator and include industrial, scientific, medical (ISM), broadcast and commercial aerospace applications. Many of the same attributes that led to the displacement of bipolar transistors from the cellular infrastructure market in the early 1990s are equally valued in the broad RF power market: high power, gain, efficiency and linearity, low cost and outstanding reliability. In addition, the RF power market demands the very high RF ruggedness that LDMOS can deliver. The enhanced ruggedness LDMOS devices available from Freescale can displace not only bipolar devices but VMOS and vacuum tube devices that are still used in some ISM, broadcast and commercial aerospace applications. -

Fundamentals of MOSFET and IGBT Gate Driver Circuits

Application Report SLUA618A–March 2017–Revised October 2018 Fundamentals of MOSFET and IGBT Gate Driver Circuits Laszlo Balogh ABSTRACT The main purpose of this application report is to demonstrate a systematic approach to design high performance gate drive circuits for high speed switching applications. It is an informative collection of topics offering a “one-stop-shopping” to solve the most common design challenges. Therefore, it should be of interest to power electronics engineers at all levels of experience. The most popular circuit solutions and their performance are analyzed, including the effect of parasitic components, transient and extreme operating conditions. The discussion builds from simple to more complex problems starting with an overview of MOSFET technology and switching operation. Design procedure for ground referenced and high side gate drive circuits, AC coupled and transformer isolated solutions are described in great details. A special section deals with the gate drive requirements of the MOSFETs in synchronous rectifier applications. For more information, see the Overview for MOSFET and IGBT Gate Drivers product page. Several, step-by-step numerical design examples complement the application report. This document is also available in Chinese: MOSFET 和 IGBT 栅极驱动器电路的基本原理 Contents 1 Introduction ................................................................................................................... 2 2 MOSFET Technology ...................................................................................................... -

Insulated Gate Bipolar Transistors (Igbts)

ECE442 Power Semiconductor Devices and Integrated Circuits Insulated Gate Bipolar Transistors (IGBTs) Zheng Yang (ERF 3017, email: [email protected]) Silicon Power Device Status Overview Silicon Power Rectifiers In the case of low voltage (<100V), the silicon P-i-N rectifier has been replaced by the silicon Schottky rectifier. In the case of high voltage (>100V), the silicon P-i-N rectifier continues to dominate but significant improvements are expected. Silicon Power Switches In the case of low voltage (<100V) systems, the silicon bipolar power transistor has been replaced by the silicon power MOSFET. In the case of high voltage (>100V) systems, the silicon bipolar power transistor has been replaced by the silicon IGBT. Power devices from wide-bandgap materials [cited from “H Amano et al, “The 2018 GaN power electronics roadmap”, Journal of Physics D: Applied Physics 51, 163001 (2018)] Background Pros of power MOSFET: (1) It has an excellent low on-state voltage drop due to the low resistance of the drift region (at low and modest voltages). (2) It is a voltage-controlled device and has a very high input impedance in steady-state due to its MOS gate structure. (3) It has a very fast inherent switching speed in comparison to power BJTs, due to the absence of minority carrier injection. (4) It has superior ruggedness and forward biased safe operating area (SOA) when compared to power BJTs. Cons of power MOSFET: Due to its excellent electrical characteristics, it would be desirable to utilize power MOSFET’s for high voltage power electronics applications. Unfortunately, the specific on-resistance of the drift region increases very rapidly with increasing breakdown voltage because of the need to reduce its doping concentration and increase its thickness.